## **General Description**

The MAX528/MAX529 are monolithic devices combining an octal 8-bit, digital-to-analog converter (DAC), 8 output buffers, and serial-interface logic in a space-saving shrink small outline package (SSOP). The MAX528 operates from a single supply up to 15V or from split supplies totaling up to 20V, including +5V/-15V, +12V/-5V, and +15V/-5V. The MAX529 operates from a single +5V supply or from ±5V split supplies. For both parts, a shutdown pin reduces current consumption to under 50µA, while retaining all internal DAC data.

Three output modes are serially programmable for each pair of 8 analog outputs. An unbuffered mode connects the internal R-2R DAC network directly to the output pin, reducing power consumption and avoiding the buffer's DC errors. A full-buffered mode inserts a buffer between the R-2R network and the output, providing +5mA/-2mA output drive. Half-buffered output mode is similar, but uses less power while still providing up to 15mA of output drive in a unipolar output configuration.

Serial data can be "daisy-chained" from one device to another. On power-up, all data bits are reset to 0, and analog outputs enter the unbuffered mode.

## Applications

Digital Gain and Offset Adjustment Digital Calibration Multiple Trim Pot Replacement Microcontrolled Analog Outputs

## Features

- ♦ Now Available in Space-Saving SSOP

- ♦ 8 Buffered Noninverting Outputs

- **♦ Buffer Disable Control**

- ♦ 2 Pairs of Differential Reference Inputs

- ♦ 3-Wire Serial Interface

- ♦ Single +5V or Dual ±5V Supply Operation (MAX529)

- ♦ Low-Power Shutdown

- ♦ Stable Driving Output Capacitance Loads

# Ordering Information

| PART      | TEMP. RANGE     | PIN-PACKAGE    |

|-----------|-----------------|----------------|

| MAX528CPP | 0°C to +70°C    | 20 Plastic DIP |

| MAX528CWG | 0°C to +70°C    | 24 Wide SO     |

| MAX528CAG | 0°C to +70°C    | 24 SSOP        |

| MAX528C/D | 0°C to +70°C    | Dice*          |

| MAX528EPP | -40°C to +85°C  | 20 Plastic DIP |

| MAX528EWG | -40°C to +85°C  | 24 Wide SO     |

| MAX528EAG | -40°C to +85°C  | 24 SSOP        |

| MAX528MJP | -55°C to +125°C | 20 CERDIP**    |

#### Ordering Information continued on last page.

- Contact factory for dice specifications.

- \*\* Contact factory for availability and processing to MIL-STD-883.

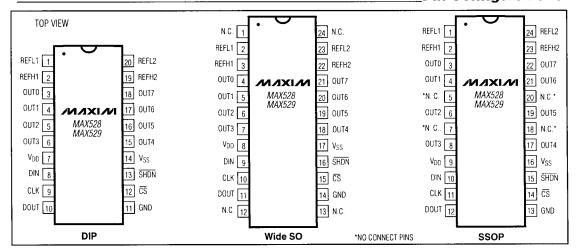

## Pin Configurations

MIXIM

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

# **ABSOLUTE MAXIMUM RATINGS - MAX528**

| V <sub>DD</sub> to GND       | 0.3V to +17V                                     |

|------------------------------|--------------------------------------------------|

| VDD to VSS                   | 0.3V to +22V                                     |

| Vss to GND                   | -17V to +0.3V                                    |

| REFH1 - REFL1, REFH2 - REFL2 |                                                  |

| REFH1 - Vss. REFH2 - Vss     | +17V                                             |

| REFH1, REFH2                 | REFL 0.3V to Vnn + 0.3V                          |

| REFL1, REFL2                 | Vss - 0.3V to REFH_ + 0.3V                       |

| OUT(1-8)                     | Vss - 0.3V to V <sub>DD</sub> + 0.3V             |

| OUT(1-8) to Vss              | +17V                                             |

| OUT(1-8) Current             | ±20mA                                            |

| DIN, CLK, CS, DOUT           | 0.3V to V <sub>DD</sub> + 0.3V                   |

| SHDN                         | V <sub>SS</sub> - 0.3V to V <sub>DD</sub> + 0.3V |

|                              |                                                  |

| DOUT Current±20mA                                     |

|-------------------------------------------------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| Plastic DIP (derate 11.11mW/°C above +70°C)889mW      |

| Wide SO (derate 11.76mW/°C above +70°C)941mW          |

| SSOP (derate 8.00mW/°C above +70°C)640mW              |

| CERDIP (derate 11.11mW/°C above +70°C)889mW           |

| Operating Temperature Ranges:                         |

| MAX528C0°C to +70°C                                   |

| MAX528E40°C to +85°C                                  |

| MAX528MJP55°C to +125°C                               |

| Storage Temperature Range65°C to +160°C               |

| Lead Temperature (soldering, 10 sec)+300°C            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS - MAX528**

(Unbuffered Mode:  $V_{DD} = +12V$ ,  $V_{SS} = 0V$ ; Full-Buffered Mode:  $V_{DD} = +12V$ ,  $V_{SS} = -5V$ ; GND = 0V, REFH = +5V, REFL = 0V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                                          | SYMBOL                              | CONDITIONS                                                                 | CONDITIONS UNBUFFERED MODE (Note 1) |       | FULL-BUFFERED MODE<br>(Note 2) |                      |      | UNITS                  |              |  |

|----------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|-------------------------------------|-------|--------------------------------|----------------------|------|------------------------|--------------|--|

|                                                    |                                     |                                                                            | MIN                                 | _ TYP | MAX                            | MIN                  | TYP  | MAX                    |              |  |

| STATIC PERFORMAN                                   | ICE                                 |                                                                            |                                     |       |                                |                      |      | _                      | _            |  |

| Resolution                                         |                                     |                                                                            | 8                                   |       |                                | 8                    |      |                        | Bits         |  |

| Relative Accuracy (Note 3)                         | RLE                                 |                                                                            |                                     | ±0.3  | ±1.0                           |                      | ±0.3 | ±1.0                   | LSB          |  |

| Differential<br>Nonlinearity (Note 4)              | DNL                                 | Guaranteed monotonic                                                       | ł                                   | ±0.3  | ±1.0                           |                      | ±0.3 | ±1.0                   | LSB          |  |

| Full-Scale Error                                   | FSE                                 | R <sub>LOAD</sub> = open                                                   |                                     |       | ±1/2                           | 1                    | _    |                        | LSB          |  |

| Gain Error (Note 5)                                |                                     | RLOAD = open                                                               |                                     |       | _                              |                      | -0.2 |                        | %            |  |

| ——————————————————————————————————————             |                                     | $R_{LOAD} = 5k\Omega$                                                      |                                     |       |                                | 0.0                  | -1.3 | -2.5                   | %            |  |

| Zero-Code Error                                    |                                     |                                                                            |                                     |       | ±5                             |                      |      | ±60                    | mV           |  |

| Zero-Code Tempco                                   |                                     |                                                                            |                                     | ±5    |                                |                      | ±100 |                        | μV/"C        |  |

| DAC Output<br>Resistance                           | Rout                                |                                                                            | 8.5k                                | 13k   | 20k                            |                      | 55   | 100                    | Ω            |  |

| DAC Output<br>Resistance Match                     | ΔR <sub>OUT</sub> /R <sub>OUT</sub> |                                                                            |                                     | 0.5   |                                |                      | 5.0  | -                      | %            |  |

| V <sub>DD</sub> Supply Rejection<br>Ratio (Note 6) | PSRRV <sub>DD</sub>                 | DAC code = 55 (hex)                                                        |                                     | 0.1   | 1.0                            |                      | 0.3  | 2.0                    | mV/V         |  |

| Vss Supply Rejection<br>Ratio (Notes 4,6)          | PSRRV <sub>SS</sub>                 | DAC code = 55 (hex)                                                        | ,                                   | 0.1   | 1.0                            |                      | 0.8  | 5.0                    | mV/V         |  |

| REFERENCE INPUT                                    | _                                   |                                                                            |                                     |       |                                |                      |      |                        | -            |  |

| Voltage Range                                      | REFH                                | REFH - REFL = 11V                                                          | REFL                                |       | V <sub>DD</sub> -3             | REFL                 |      | <br>V <sub>DD</sub> -3 | $\Gamma_{v}$ |  |

| (Note 7)                                           | REFL                                | max                                                                        | VSS                                 |       | REFH                           | V <sub>SS</sub> +1.5 |      | REFH                   | \ \          |  |

| Input Resistance<br>(Note 8)                       | REFH1/REFL1,<br>or<br>REFH2/REFL2   | DAC code = 55 (hex)                                                        | 2.0                                 | 3.4   |                                | 2.0                  | 3.4  | _                      | kΩ           |  |

| Input Capacitance                                  | CREFH                               | DAC loaded with 0s                                                         |                                     | 40    |                                |                      | 40   |                        | _            |  |

| при Сараспансе                                     | CHEFH                               | DAC loaded with 1s                                                         |                                     | 250   |                                | †                    | 125  |                        | pF           |  |

| AC Feedthrough                                     |                                     | REFH=10kHz, 0-10V <sub>p-p</sub><br>sinewave, all DACs at<br>code 00 (hex) |                                     | -70   |                                |                      | -70  |                        | dB           |  |

# **ELECTRICAL CHARACTERISTICS - MAX528 (continued)**

(Unbuffered Mode:  $V_{DD} = +12V$ ,  $V_{SS} = 0V$ ; Full-Buffered Mode:  $V_{DD} = +12V$ ,  $V_{SS} = -5V$ ; GND = 0V, REFH = +5V, REFL = 0V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                      | SYMBOL          | CONDITIONS                                                                                                                       | UNBU | (Note 1) |      | FULL-B   | UFFEREI<br>(Note 2) |      | UNITS |

|--------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|------|----------|------|----------|---------------------|------|-------|

| . ,                            |                 |                                                                                                                                  | MIN  | TYP      | MAX  | MIN      | TYP                 | MAX  |       |

| POWER REQUIREMEN               | ITS             |                                                                                                                                  |      |          |      |          | _                   |      |       |

| Positive Supply Range          | V <sub>DD</sub> |                                                                                                                                  | 10.8 |          | 16.5 | 10.8     |                     | 16.5 | V     |

| Negative Supply<br>Range       | V <sub>SS</sub> |                                                                                                                                  | 0    |          | -5.5 | -1.5     |                     | -5.5 |       |

| Positve Supply<br>Current      | IDD             | $\frac{DIN = CLK = 0V}{CS = SHDN} = 5V$                                                                                          | _    | 0.3      | 1.0  |          | 5.5                 | 9.0  | mA    |

| Negative Supply<br>Current     | ISS             | DIN = CLK = 0V,<br>CS = SHDN = 5V                                                                                                |      | 0.1      | 0.5  | <u> </u> | 5.5                 | 9.0  | mA    |

| I <sub>DD</sub> at Shutdown    | lDD             | SHDN = low                                                                                                                       |      |          | 50_  |          |                     | 50   | μΑ    |

| Iss at Shutdown                | Iss             | SHDN = low                                                                                                                       |      |          | 50   |          |                     | 50   | μΑ    |

| DYNAMIC PERFORMA               | NCE (Note 7)    |                                                                                                                                  |      |          |      | ,        |                     |      | _     |

| V <sub>OUT</sub> Settling Time |                 | To ±1/2LSB; C <sub>LOAD</sub> = 20pF, from rising edge of CS                                                                     |      | 1        | 3    |          | 0.6                 | 2.0  | μs    |

| Digital Coupling               |                 | Serial input: 1MHz<br>CLK, DIN alternating<br>1s and 0s (0.5MHz),<br>C <sub>L</sub> = 20pF, 0V to 5V<br>input levels at CLK, DIN |      | 20       |      |          | 20                  |      | mVp-p |

|                                |                 | Full-scale output transition on all 7 other channels (CS high)                                                                   |      | 40       |      |          | 20                  |      | nV-s  |

| Crosstalk                      |                 | 1LSB output transition<br>on all 7 other channels<br>(CS high)                                                                   |      | 2        |      |          | 10                  |      |       |

# **DIGITAL AND SWITCHING CHARACTERISTICS - MAX528**

$(V_{DD} = +12V, V_{SS} = -5V, REFH = +5V, REFL = 0V, T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)$

| PARAMETER                        | SYMBOL            | CONDITIONS                               | MIN | TYP | MAX | UNITS     |

|----------------------------------|-------------------|------------------------------------------|-----|-----|-----|-----------|

| DIGITAL INPUTS DIN, CLK, CS, SI  | IDN               |                                          |     |     |     |           |

| Input High Voltage               | V <sub>INH</sub>  | DIN, CLK, CS                             | 2.4 |     |     | V         |

| Input Low Voltage                | V <sub>IN</sub> L | DIN, CLK, CS                             |     |     | 0.8 | V         |

| Input High Voltage               | VINH              | SHDN                                     | 3.0 |     |     | V         |

| Input Low Voltage                | VINL              | SHDN                                     |     |     | 0.5 | V         |

| Input Hysteresis                 |                   | DIN, CLK, CS                             |     | 0.1 |     | V         |

| Input Leakage Current            |                   | V <sub>IN</sub> = 0V or V <sub>DD</sub>  |     |     | ±1  | μΑ        |

| Input Capacitance (Note 7)       |                   |                                          |     |     | 10  | pF        |

| DIGITAL OUTPUT, DOUT, open dra   | n output, 1ks     | 2 pull-up resistor to +5V                |     |     |     | ,         |

| Output Low Voltage               | VOL               | ISINK = 5mA                              |     |     | 0.4 | \ \ \ \ _ |

| Output High Leakage              | ILKG              | V <sub>OUT</sub> = 0V to V <sub>DD</sub> |     |     | ±10 | μΑ        |

| Output High Capacitance (Note 7) | Cout              |                                          |     |     | 15  | pF        |

# **DIGITAL AND SWITCHING CHARACTERISTICS - MAX528 (continued)**

(VDD = +12V, VSS = -5V, REFH = +5V, REFL = 0V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                            | SYMBOL          | CONDITIONS                                     | MIN            | TYP | MAX | UNITS |

|--------------------------------------|-----------------|------------------------------------------------|----------------|-----|-----|-------|

| SWITCHING CHARACTERISTICS            |                 |                                                |                |     |     |       |

| CLK Pulse Width High                 | tсн             |                                                | 80             |     |     | ns    |

| CLK Pulse Width Low                  | tCL             |                                                | 80             |     |     | ns    |

| DIN to CLK High Setup                | t <sub>DS</sub> |                                                | 40             |     |     | ns    |

| DIN to CLK High Hold                 | tDH             |                                                | 15             |     |     | ns    |

| CS Low to CLK High Setup             | tCSS0           |                                                | 50             |     |     | ns    |

| CS High to CLK High Setup            | tCSS1           |                                                | 50             |     |     | ns    |

| Delay, CLK Low to Low CS             | tCSH0           |                                                | 0              |     |     | ns    |

| Delay, CLK High to High CS           | tCSH1           |                                                | 50             |     |     | ns    |

| CS Pulse Width                       | tcsw            |                                                | 130            |     |     | ns    |

| CLK High to DOUT Data Valid (Note 9) | tDO             | $C_{LOAD}$ = 20pF, Rpullup = 1k $\Omega$ to 5V | 15<br>(Note 7) |     | 130 | ns    |

| CS Low to DOUT Enable (Note 10)      | t <sub>DV</sub> | $C_{LOAD}$ = 20pF, Rpullup = 1k $\Omega$ to 5V |                |     | 90  | ns    |

| CS High to DOUT Disable (Note 10)    | tTR             | $C_{LOAD}$ = 20pF, Rpullup = 1k $\Omega$ to 5V |                |     | 90  | ns    |

Note 1: Unbuffered mode – buffers disabled. No output load. Note 2: Full-buffered mode – buffers enabled; bipolar output mode;  $R_{LOAD} = 5k\Omega$ . Note 3: Relative accuracy in unbuffered mode guaranteed by relative accuracy test in full-buffered mode. Note 4: Specification in Unbuffered Mode column guaranteed by design only. Not subject to test. Note 5: Gain error with full-buffered mode enabled = no-load gain error - (DAC output resistance/ $R_{LOAD}$ ). Example: -0.2% typ no-load error - (55 $\Omega$ /5 $k\Omega$ ) = -1.3% typ error for 5 $k\Omega$  load. Note 6: PSRR tested over supply range specified under power requirements; PSRR = (VouT1 - VouT2)/(VsuPPLY1 - VsuPPLY2). Note 7: Guaranteed by design, not subject to test. Note 8: Input resistance tested only under Unbuffered Mode conditions in Note1 above. Note 9: VoH = 2.4V, VoL = 0.8V. Note 10: toy and tra are defined as the time required for DOUT to change 0.5V.

Note 10: tDV and tTR are defined as the time required for DOUT to change 0.5V.

| ABSOLUTE | MAXIMUM | <b>RATINGS</b> - | <b>MAX529</b> |

|----------|---------|------------------|---------------|

|----------|---------|------------------|---------------|

| V <sub>DD</sub> to GND0.3V to +7V                 | DOUT Current                                          |

|---------------------------------------------------|-------------------------------------------------------|

| V <sub>DD</sub> to V <sub>SS</sub>                | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| Vss to GND7V to +0.3V                             | Plastic DIP (derate 11.11mW/°C above +70°C) 889mW     |

| REFH1 - REFL1, REFH2 - REFL20.3V to +12V          | Wide SO (derate 11.76mW/°C above +70°C) 941mW         |

| REFH1 - V <sub>SS</sub> , REFH2 - V <sub>SS</sub> | CERDIP (derate 11.11mW/°C above +70°C) 889mW          |

| REFH1, REFH2 REFL 0.3V to V <sub>DD</sub> + 0.3V  | Operating Temperature Ranges:                         |

| REFL1, REFL2                                      | MAX528C 0°C to +70°C                                  |

| OUT(1-8)                                          | MAX528E40°C to +85°C                                  |

| OUT(1-8) to Vss                                   | MAX528MJP55°C to +125°C                               |

| OUT(1-8) Current                                  | Storage Temperature Range65°C to +160°C               |

| DIN, CLK, CS, DOUT0.3V to V <sub>DD</sub> + 0.3V  | Lead Temperature (soldering, 10 sec) +300°C           |

| SHDN Vss - 0.3V to Vnp + 0.3V                     |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS - MAX529**

$(Unbuffered\ Mode:\ V_{DD} = +5V,\ V_{SS} = GND = 0V,\ REFH = +2.5V,\ REFL = 0V:\ Full-Buffered\ Mode:\ V_{DD} = +5V,\ V_{SS} = -5V,\ GND = 0V,\ REFH = +2.5V,\ REFL = -2.5V,\ TA = T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.)$

| PARAMETER                                             | SYMBOL                              | CONDITIONS               | UNBU            | JFFERED<br>(Note 1) |                        | FULL-B               | UFFERI<br>(Note 2 | ED MODE                | UNITS |

|-------------------------------------------------------|-------------------------------------|--------------------------|-----------------|---------------------|------------------------|----------------------|-------------------|------------------------|-------|

|                                                       |                                     |                          | MIN             | TYP                 | MAX                    | MIN                  | TYP               | MAX                    |       |

| STATIC PERFORMANCE                                    | CE                                  |                          |                 |                     |                        |                      |                   |                        |       |

| Resolution                                            |                                     |                          | 8               |                     |                        | 8                    |                   |                        | Bits  |

| Relative Accuracy<br>(Note 3)                         | RLE                                 |                          |                 | ±0.3                | ±1.0                   |                      | ±0.3              | ±1.0                   | LSB   |

| Differential<br>Nonlinearity (Note 4)                 | DNL                                 | Guaranteed monotonic     |                 | ±0.3                | ±1.0 .                 |                      | ±0.3              | ±1.0                   | LSB   |

| Full-Scale Error                                      | FSE                                 | R <sub>LOAD</sub> = open |                 |                     | ±1/2                   |                      |                   |                        | LSB   |

| Gain Error (Note 5)                                   |                                     | RLOAD = open             |                 |                     |                        |                      | -0.2              |                        | %     |

| Gair Ellor (Note 3)                                   |                                     | $R_{LOAD} = 5k\Omega$    |                 |                     |                        | 0.0                  | -1.3              | -2.5                   | %     |

| Unipolar Offset Error                                 |                                     | DAC code = 00 (hex)      |                 |                     | ±5                     |                      |                   |                        | mV    |

| Bipolar Offset Error                                  |                                     | DAC code = 80 (hex)      |                 |                     |                        |                      |                   | ±60                    | mV    |

| Offset Error Tempco                                   |                                     |                          |                 | ±5                  |                        |                      | ±100              |                        | μV/°C |

| DAC Output Resistance                                 | Rout                                |                          | 8.5k            | 13k                 | 20k                    | 1                    | 55                | 100                    | Ω     |

| DAC Output<br>Resistance Match                        | ΔR <sub>OUT</sub> /R <sub>OUT</sub> |                          |                 | 0.5                 |                        |                      | 5.0               |                        | %     |

| V <sub>DD</sub> Supply Rejection<br>Ratio (Note 6)    | PSRRV <sub>DD</sub>                 | DAC code = 55 (hex)      |                 | 1.5                 | 5                      |                      | 3                 | 10                     | mV/V  |

| V <sub>SS</sub> Supply Rejection<br>Ratio (Notes 4,6) | PSRRV <sub>SS</sub>                 | DAC code = 55 (hex)      |                 | 0.3                 | 2                      |                      | 1                 | 5                      | mV/V  |

| REFERENCE INPUT                                       |                                     |                          |                 |                     |                        |                      |                   |                        |       |

| Voltage Range                                         | REFH                                |                          | REFL            |                     | V <sub>DD</sub> - 2.25 | REFL                 |                   | V <sub>DD</sub> - 2.25 |       |

| (Note 7)                                              | REFL                                |                          | $V_{\text{SS}}$ |                     | REFH                   | V <sub>SS</sub> +1.5 |                   | REFH                   | V     |

| Input Resistance<br>(Note 8)                          | REFH1/REFL1,<br>or<br>REFH2/REFL2   | DAC code = 55 (hex)      | 2.0             | 3.4                 |                        | 2.0                  | 3.4               |                        | kΩ    |

| Innut Congoitanos                                     | Coccu                               | DAC loaded with 0s       |                 | 40                  |                        |                      | 40                |                        | pF    |

| Input Capacitance                                     | CREFH                               | DAC loaded with 1s       |                 | 250                 |                        |                      | 125               |                        | , pi  |

# **ELECTRICAL CHARACTERISTICS - MAX529 (continued)**

(Unbuffered Mode:  $V_{DD} = +5V$ ,  $V_{SS} = GND = ON$ , REFH = +2.5V, REFL = 0V; Full-Buffered Mode:  $V_{DD} = +5V$ ,  $V_{SS} = -5V$ , GND = 0V, REFH = +2.5V, REFL = -2.5V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER SYM                  | SYMBOL          | CONDITIONS                                                                                                                       | UNBL | JFFERED<br>(Note 1) |      | FULL-B | UFFEREI<br>(Note 2) | MODE         | UNITS |

|--------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|--------|---------------------|--------------|-------|

|                                |                 |                                                                                                                                  | MIN  | TYP                 | MAX  | MIN    | TYP                 | MAX          |       |

| AC Feedthrough                 |                 | REFH=10kHz, 0-2.5V <sub>p-p</sub><br>sinewave, all DACs at<br>code 00 (hex)                                                      | ·    | -70                 |      |        | -70                 | <del>-</del> | dB    |

| POWER REQUIREME                | NTS             |                                                                                                                                  |      | -                   |      |        |                     |              |       |

| Positive Supply Range          | V <sub>DD</sub> |                                                                                                                                  | 4.75 |                     | 5.25 | 4.75   |                     | 5.25         | V     |

| Negative Supply<br>Range       | V <sub>SS</sub> |                                                                                                                                  | 0    |                     | -5.5 | -4.5   |                     | -5.5         | V     |

| Positve Supply<br>Current      | loo             | DIN = CLK = 0V,<br>CS = SHDN = 5V                                                                                                |      | 0.3                 | 1.0  |        | 5.5                 | 9.0          | mA    |

| Negative Supply<br>Current     | Iss             | DIN = CLK = 0V,<br>CS = SHDN = 5V                                                                                                |      | 0.1                 | 0.5  |        | 5.5                 | 9.0          | mA    |

| IDD at Shutdown                | I <sub>DD</sub> | SHDN = low                                                                                                                       | •    |                     | 50   |        |                     | 50           | μА    |

| Iss at Shutdown                | Iss             | SHDN = low                                                                                                                       |      |                     | 50   |        |                     | 50           | μΑ    |

| DYNAMIC PERFORMA               | ANCE (Note      | 7)                                                                                                                               |      | -                   |      | ·      |                     |              |       |

| V <sub>OUT</sub> Settling Time |                 | To $\pm 1/2$ LSB; C <sub>LOAD</sub> = $20$ pF, from rising edge of CS                                                            |      | 1                   | 3    |        | 0.6                 | 2.0          | μs    |

| Digital Coupling               |                 | Serial input: 1MHz<br>CLK, DIN alternating<br>1s and 0s (0.5MHz),<br>C <sub>L</sub> = 20pF, 0V to 5V<br>input levels at CLK, DIN |      | 20                  |      |        | 20                  |              | mVp-p |

| Crosstalk                      |                 | Full-scale output transition on all <u>7 other</u> channels (CS high)                                                            |      | 40                  |      |        | 20                  |              | nV-s  |

|                                |                 | 1LSB output transition<br>on all 7 other channels<br>(CS high)                                                                   |      | 2                   |      |        | 10                  |              | 110-5 |

# **DIGITAL AND SWITCHING CHARACTERISTICS - MAX529**

$(V_{DD} = +5V, V_{SS} = -5V, REFH = +2.5V, REFL = -2.5V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                        | SYMBOL           | CONDITIONS                               | MIN      | TYP | MAX | UNITS |

|----------------------------------|------------------|------------------------------------------|----------|-----|-----|-------|

| DIGITAL INPUTS DIN, CLK, CS, SI  | IDN              | SHDI                                     | N        |     |     |       |

| Input High Voltage               | V <sub>INH</sub> | DIN, CLK, CS                             | 2.4      |     |     | V     |

| Input Low Voltage                | VINL             | DIN, CLK, CS                             |          |     | 0.8 | V     |

| Input High Voltage               | V <sub>INH</sub> | SHDN                                     | 3.0      |     |     | V     |

| Input Low Voltage                | VINL             | SHDN                                     |          |     | 0.5 | V     |

| Input Hysteresis                 |                  | DIN, CLK, CS                             |          | 0.1 |     | V     |

| Input Leakage Current            |                  | V <sub>IN</sub> = 0V or V <sub>DD</sub>  |          |     | ±1  | μА    |

| Input Capacitance (Note 7)       |                  |                                          |          |     | 10  | pF    |

| DIGITAL OUTPUT, DOUT, open drai  | n output, 1.3l   | cΩ pull-up resistor to +5V               | <u> </u> |     | _   |       |

| Output Low Voltage               | VOL              | I <sub>SINK</sub> = 3.5mA                |          |     | 0.4 | V     |

| Output High Leakage              | I <sub>LKG</sub> | V <sub>OUT</sub> = 0V to V <sub>DD</sub> |          |     | ±10 | μА    |

| Output High Capacitance (Note 7) | Соит             |                                          |          |     | 15  | pF    |

6 \_\_\_\_\_\_ /VIXI/VI

# **DIGITAL AND SWITCHING CHARACTERISTICS - MAX529 (continued)**

(VDD = +5V, VSS = -5V, REFH = +2.5V, REFL = -2.5V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                                      | SYMBOL          | CONDITIONS                                      | MIN            | TYP MAX | UNITS |

|------------------------------------------------|-----------------|-------------------------------------------------|----------------|---------|-------|

| SWITCHING CHARACTERISTICS                      |                 |                                                 | ,              |         |       |

| CLK Pulse Width High                           | tсн             |                                                 | 125            |         | ns    |

| CLK Pulse Width Low                            | toL             |                                                 | 125            |         | ns    |

| DIN to CLK High Setup                          | tDS             |                                                 | 50             |         | ns    |

| DIN to CLK High Hold                           | tDH             |                                                 | 20             |         | ns    |

| CS Low to CLK High Setup                       | tcsso           |                                                 | 50             |         | ns    |

| CS High to CLK High Setup                      | tcss1           |                                                 | 50             |         | ns    |

| Delay, CLK Low to Low CS                       | tcs+10          |                                                 | 0              |         | ns    |

| Delay, CLK High to High $\overline{\text{CS}}$ | tCSH1           |                                                 | 50             |         | ns    |

| CS Pulse Width                                 | tcsw            |                                                 | 300            |         | ns    |

| CLK High to DOUT Data Valid (Note 9)           | t <sub>DO</sub> | $C_{LOAD}$ = 20pF, Rpullup = 1k $\Omega$ to 5V  | 20<br>(Note 7) | 200     | ns    |

| CS Low to DOUT Enable (Note 10)                | tDV             | $C_{LOAD} = 20$ pF, Rpullup = 1k $\Omega$ to 5V |                | 120     | ns    |

| CS High to DOUT Disable (Note 10)              | t <sub>TR</sub> | $C_{LOAD} = 20$ pF, Rpullup = 1k $\Omega$ to 5V |                | 120     | ns    |

Unbuffered mode - buffers disabled. No output load.

Note 1: Unbuffered mode – buffers disabled. No output load.

Note 2: Full-buffered mode – buffers enabled; bipolar output mode; R<sub>LOAD</sub> = 5kΩ.

Note 3: Relative accuracy in unbuffered mode guaranteed by relative accuracy test in full-buffered mode.

Note 4: Specification in Unbuffered Mode column guaranteed by design only. Not subject to test.

Note 5: Gain error with full-buffered mode enabled = no-load gain error - (DAC output resistance/R<sub>LOAD</sub>). Example: -0.2% typ noload error - (55Ω/5kΩ) = -1.3% typ error for 5kΩ load.

Note 6: PSRR tested over supply range specified under power requirements; PSRR = (V<sub>OUT1</sub> - V<sub>OUT2</sub>)/(V<sub>SUPPLY1</sub> - V<sub>SUPPLY2</sub>).

Note 7: Guaranteed by design, not subject to test.

Note 8: Input resistance tested only under Unbuffered Mode conditions in Note1 above.

Note 9: V<sub>OH</sub> = 2.4V, V<sub>OL</sub> = 0.8V.

Note 10: tpy and t<sub>TR</sub> are defined as the time required for DOUT to change 0.5V.

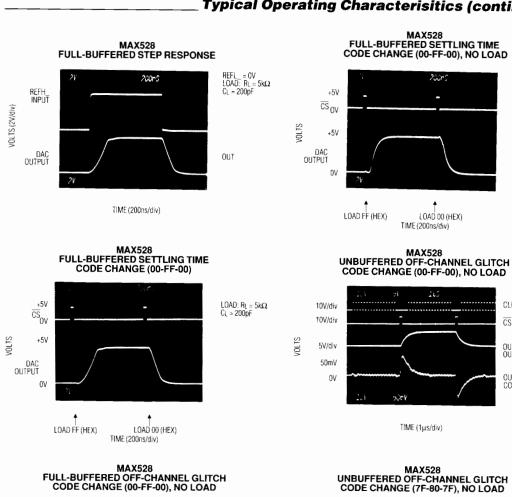

# **Typical Operating Characterisitics**

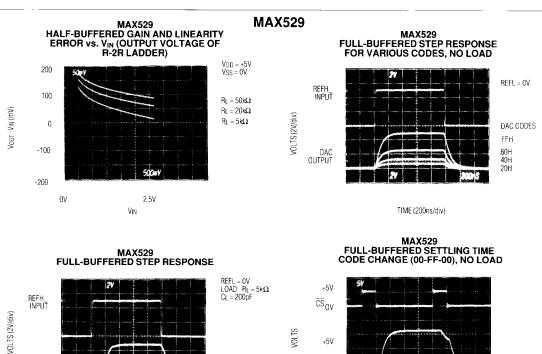

#### **MAX528 MAX528** HALF-BUFFERED GAIN AND LINEARITY ERROR vs. V<sub>IN</sub> (OUTPUT VOLTAGE OF R-2R LADDER) MAX528 FULL-BUFFERED STEP RESPONSE FOR VARIOUS CODES, NO LOAD $V_{DD} = +12V$ $V_{SS} = 0V$ 200 REFL\_ - 0V 100 $R_L = 50k\Omega$ Vour -Vin (mV) VOLTS (2V/div) DAC CODES R<sub>L</sub> = 20kΩ 0 DAC OUTPUT 80H -100 $R_L = 5k\Omega$ 40H 20H -200 0٧ 9٧ TIME (200ns/div) Vin

# MAX528/MAX529

# **Octal 8-Bit Serial DACs** with Output Buffer

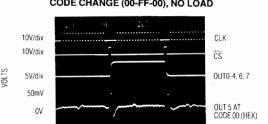

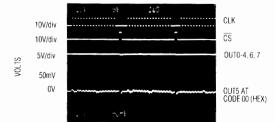

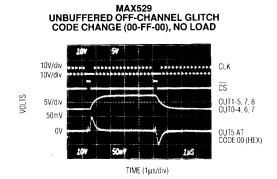

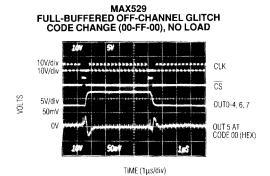

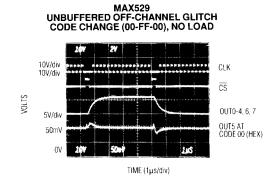

# **Typical Operating Characterisitics (continued)**

CLK

$\overline{\text{CS}}$

OUT1-5, 7, 8 OUT0-4, 6, 7

OUT5 AT CODE 00 (HEX)

ノレノノメノノレ

# **Typical Operating Characteristics (continued)**

# **Typical Operating Characteristics (continued)**

TIME (2µs/div)

# Pin Description

|                 | PIN |                  |                 |                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|-----------------|-----|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| SSOP            | DIP | so               | NAME            | FUNCTION                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 5, 7,<br>18, 20 | -   | 1, 12,<br>13, 24 | N.C.            | No Connect. These pins are not internally connected.                                                                                                                                                              |  |  |  |  |  |  |  |

| 1               | 1   | 2                | REFL1           | Reference 1 Input Low. Must be more negative than REFH1 and more positive than Vss.                                                                                                                               |  |  |  |  |  |  |  |

| 2               | 2   | 3                | REFH1           | Reference 1 Input High. Must be more positive than REFL1 and more negative than VDD.                                                                                                                              |  |  |  |  |  |  |  |

| 3               | 3   | 4                | ОИТО            | Output Voltage 0. The product of the digital code for channel 0 and (REFH1 - REFL1), referenced to REFL1.                                                                                                         |  |  |  |  |  |  |  |

| 4               | 4   | 5                | OUT1            | Output Voltage 1. The product of the digital code for channel 1 and (REFH1 - REFL1), referenced to REFL1.                                                                                                         |  |  |  |  |  |  |  |

| 6               | 5   | 6                | OUT2            | Output Voltage 2. The product of the digital code for channel 2 and (REFH1 - REFL1), referenced to REFL1.                                                                                                         |  |  |  |  |  |  |  |

| 8               | 6   | 7                | ОИТЗ            | Output Voltage 3. The product of the digital code for channel 3 and (REFH1 - REFL1), referenced to REFL1.                                                                                                         |  |  |  |  |  |  |  |

| 9               | 7   | 8                | V <sub>DD</sub> | Positive Analog and Digital Supply.                                                                                                                                                                               |  |  |  |  |  |  |  |

| 10              | 8   | 9                | DIN             | Digital Input. CMOS and TTL compatible serial programming input.                                                                                                                                                  |  |  |  |  |  |  |  |

| 11              | 9   | 10               | CLK             | Clock Input. CMOS and TTL compatible clock input.                                                                                                                                                                 |  |  |  |  |  |  |  |

| 12              | 10  | 11               | DOUT            | Digital Output. Open-drain, N-channel, FET output, requires external pull-up resistor; serial data output, shifted 16 bits from DIN.                                                                              |  |  |  |  |  |  |  |

| 13              | 11  | 14               | GND             | Digital Ground. Connect to 0V. (Analog signals are referenced to their respective REFL voltage, not GND).                                                                                                         |  |  |  |  |  |  |  |

| 14              | 12  | 15               | CS              | CHIP SELECT. Connect to logic low to program serially. Connect to logic high to latch data and turn off internal shift register. Rising edge of CS transfers new data into data registers and changes DAC output. |  |  |  |  |  |  |  |

| 15              | 13  | 16               | SHDN            | SHUTDOWN. Connect to logic high for normal operation, to GND for shutdown mode.                                                                                                                                   |  |  |  |  |  |  |  |

| 16              | 14  | 17               | V <sub>SS</sub> | Negative Analog Supply. Connect to GND for single-supply operation. Connect to negative supply for bipolar DAC outputs.                                                                                           |  |  |  |  |  |  |  |

| 17              | 15  | 18               | OUT4            | Output Voltage 4. The product of the digital code for channel 4 and (REFH2 - REFL2), referenced to REFL2.                                                                                                         |  |  |  |  |  |  |  |

| 19              | 16  | 19               | OUT5            | Output Voltage 5. The product of the digital code for channel 5 and (REFH2 - REFL2), referenced to REFL2.                                                                                                         |  |  |  |  |  |  |  |

| 21              | 17  | 20               | OUT6            | Output Voltage 6. The product of the digital code for channel 6 and (REFH2 - REFL2), referenced to REFL2.                                                                                                         |  |  |  |  |  |  |  |

| 22              | 18  | 21               | OUT7            | Output Voltage 7. The product of the digital code for channel 7 and (REFH2 - REFL2), referenced to REFL2.                                                                                                         |  |  |  |  |  |  |  |

| 23              | 19  | 22               | REFH2           | Reference 2 Input High. Must be more positive than REFL2 and more negative than VDD.                                                                                                                              |  |  |  |  |  |  |  |

| 24              | 20  | 23               | REFL2           | Reference 2 Input Low. Must be more negative than REFH2 and more positive than Vss.                                                                                                                               |  |  |  |  |  |  |  |

# Detailed Description Circuit Operation

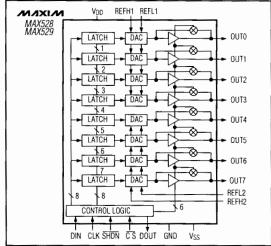

The MAX528/MAX529 contain 8 latched digital-to-analog converters (DACs), 8 buffer amplifiers, 2 reference inputs, and serial control logic. Buffer amplifiers may also be bypassed by internal switches, allowing three output modes: unbuffered, full-buffered, and half-buffered.

Any or all of the 8 voltage outputs can be programmed with 16 serial data bits.

## **DAC Output Range**

The MAX528/MAX529 provide 8 voltage outputs (OUT0-OUT7) from 2 reference inputs. Each reference voltage has 2 input pins, REFH and REFL. The OUT0-OUT3 output voltages are derived from REFH1 and REFL1 while OUT4-OUT7 are derived from REFH2 and REFL2. For each reference, REFH must be more positive than REFL A DAC output voltage is the product of its programmed 8-bit code and its reference input voltage. For example, the output voltage of OUT5 is:

OUT5 = (REFH2 - REFL2) (nn/256 + REFL2),

where nn = 8-bit code for OUT5, with a range of 0-255 (00 to FF hex.)

The reference inputs are independent of one another. REFH can range within 3V of VDD. REFL can be as low as VSS in unbuffered and half-buffered modes, but must be at least 1.5V above VSS in full-buffered mode. For the MAX528, VSS can be any negative voltage from -15V to 0V, provided that VDD-VSS is no more than 20V. For the MAX529, VSS can be any negative voltage from 0V to -5V. In all modes, REFH must be no more than 12V greater than REFL.

Although the MAX528/MAX529 have a digital ground (GND) pin, they contain no internal analog ground. The upper and lower limits of any DAC output are the voltages to which REFH and REFL are connected.

#### Shutdown

To conserve power, the MAX528/MAX529 can be shut down by pulling SHDN low. VCC and Vss supply currents drop to less than 50µA, but reference current will still be drawn. Reference current is code dependent and can be reduced to nearly 0 (leakage only) by writing 0s to all DACs.

Note: To ensure that register data is retained during shutdown, CS must be high when entering or leaving shutdown mode.

## **Buffer Output Modes**

DAC outputs can be programmed for one of three buffer modes: unbuffered, full-buffered, and half-buffered. Buffers must be activated in pairs, and full- or half-buffered mode must be selected in banks of four as shown in Table 1 (see *Digital Interface* section).

Table 1. Buffer Output-Mode Selection Codes (Address 00 hex, D6 = X, D7 = 1)

| Mode                  | OUT0, 1 | OUT2, 3 | OUT4, 5 | OUT5, 6 |

|-----------------------|---------|---------|---------|---------|

| Unbuffered (D0, D3=X) | D5 = 0  | D4 = 0  | D2 = 0  | D1 = 0  |

| Full-Buffered         | D5 = 1  | D4 = 1  | D2 = 1  | D1 = 1  |

| T dil-Danerea         | D3      | = 1     | D0      | = 1     |

| Half-Buffered         | D5 = 1  | D4 = 1  | D2 = 1  | D1 = 1  |

| nan-bunered           | D3      | = 0     | D0      | = 0     |

## Unbuffered Mode

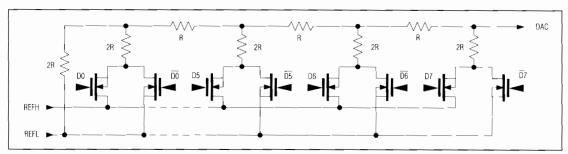

Unbuffered mode connects the internal  $20k\Omega$  R-2R DAC network (Figure 1) directly to OUT. Buffer circuitry is disabled, reducing power consumption as well as offset errors contributed by the internal buffer amplifier (see *Electrical Characteristics*). Driving high-resistance loads ( $1M\Omega$  and up) improves accuracy. Output range in unbuffered mode is from the negative supply rail (VSS) to VDD - 3V for the MAX528 (VSS to VDD -2.25V for MAX529).

Figure 1. R-2R Inverted Ladder DAC Structure

Unbuffered mode also operates effectively with lower resistance loads, but output loading may generate gain (full-scale) error. This will not affect linearity because DAC output resistance (between  $8.5 \mathrm{k}\Omega$  and  $20 \mathrm{k}\Omega$ ) does not change with code. The magnitude of the expected gain error is the ratio of the DAC output impedance (typically  $13 \mathrm{k}\Omega$ ) to the DC load resistance at the output.

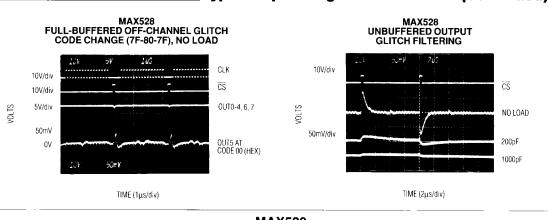

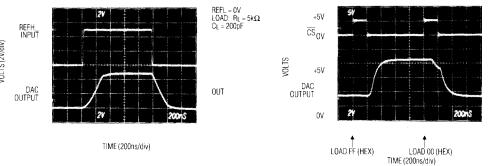

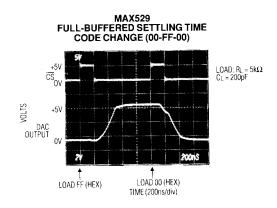

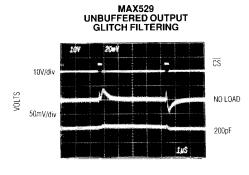

Another advantage of unbuffered operation is that output filtering uses small capacitors and no resistors. The Unbuffered Output Glitch Filtering photos in the *Typical Operating Characteristics* show the feedthrough effect of changing all channels but one from full-scale to zero. On the rising edge of  $\overline{\text{CS}}$  (top trace), energy is coupled into the unchanged channel (2nd trace, unfiltered), producing a 70mV, 1 $\mu$ s pulse for the MAX528, and a 40mV, 5 $\mu$ s pulse for the MAX529. The third and fourth traces of the MAX528 photo show how this pulse is suppressed using 200pF and 1000pF load capacitors with the MAX528. The third trace of the MAX529 photo shows this pulse suppression using a 200pF load capacitor with the MAX529.

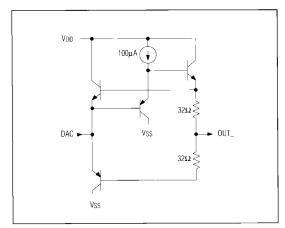

#### **Full-Buffered Mode**

Full-buffered mode (Figure 2) activates both sections of the buffer amplifer, lowering the output impedance to typically  $55\Omega$  and allowing +5mA/-2mA output currents to be supplied. The buffer amplifier output swing is from Vss + 1.5V to Vdd - 3V (Vss = +1.5V to Vdd - 2.25V for MAX529). The key advantage of this mode is that changes in load current cause minimal output change.

### **Half-Buffered Mode**

Half-buffered mode (Figure 3) activates only the top half of the output stage, and therefore sources current only. Its advantage is that it maintains output swing to VSS while

100μA 32Ω Vss VDD 32Ω VSS VDD 100μA

Figure 2. Simplifed Full-Buffered Output Circuit

providing a buffered output. Output swing is from VSS to  $V_{DD}$  - 3V (VSS = +1.5V to  $V_{DD}$  - 2.25V for MAX529). Current consumption is reduced to typically 1.7mA (compared to 5.5mA for full-buffered) if all buffers use half-buffered mode.

# Using an AC Reference with the MAX528

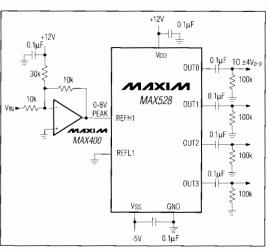

In applications where the reference has AC signal components, the MAX528 has multiplying capability within the REFH and REFL specifications. Figure 4 shows a technique for attenuating an AC signal by superimposing it on a DC voltage prior to REFH. As the DAC code changes, the AC output changes, as does the DC level. The output DC level is removed by capacitively coupling to the next stage. Note that the peak negative voltage at REFH must not swing below REFL.

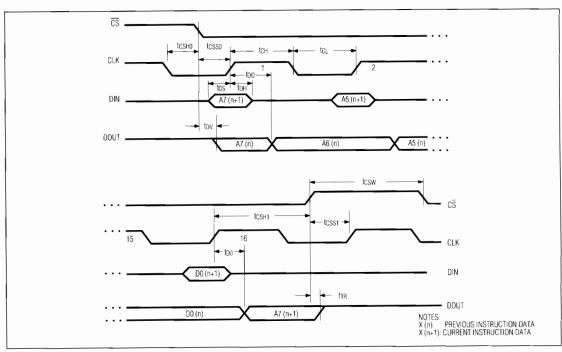

# Digital Interface Serial Interface

Serial data at DIN is clocked in on the rising edge of CLK, while  $\overline{\text{CS}}$  is low and  $\overline{\text{SHDN}}$  is high (Figure 5). Data can be loaded at clock rates up to 6.25MHz (4MHz for MAX529). Logic inputs are CMOS and TTL compatible. The serial output DOUT is an open-drain N-channel FET that sinks up to 5mA and requires an external pull-up resistor (typically  $4.7 \text{k}\Omega$ ) to VDD. Output data changes on the rising edge of CLK.

Any number of MAX528s or MAX529s can be daisy-chained by connecting the DOUT pin of one device (with pullup resistor) to the  $\overline{\text{DIN}}$  pin of the following device in the chain. CLK and  $\overline{\text{CS}}$  are bussed together. Clock period and tCSS0 ( $\overline{\text{CS}}$  low to CLK high) must be increased to account for data delays between devices.

Figure 3. Simplifed Half-Buffered Output Circuit

Figure 4. Using an AC Reference with the MAX528

If capacitive loading at the DOUT-to-DIN junction between two devices is 50pF or less, then the required tcsso becomes the sum of tpv (enable) and tps (setup times), which is 130ns (90ns + 40ns) for MAX528 and tcsso 170ns (120ns + 50ns) for the MAX529.

Maximum clock rate is influenced by pullup resistor size as well as capacitive loading: fCLKmax = 1/(tDO + tDS + 0.65tRC), where tDO = 130ns, tDS = 40ns, and tRC is the pullup resistor and capacitive load product. So for a 1k $\Omega$  pullup and 50pF load, the MAX528 fCLKmax is 4.7MHz; for a 4.7k $\Omega$  pullup with 50pF load, fCLKmax drops to 2.8MHz. A similar calculation can be made for the MAX529, using tDO = 200ns, and tDS = 50ns.

#### **DAC Programming**

The MAX528/MAX529 are programmed by 16 data bits in two 8-bit bytes, the address pointer bits (A7-A0) followed by the data byte (D7-D0). These bits enter a shift register serially through DIN: A7 first, and D0 last. The data exits DOUT 16 clock cycles later in the same order.

Data at DIN is shifted into the first register (while all 16 register bits shift forward one stage) on a rising CLK edge, while holding  $\overline{CS}$  low and  $\overline{SHDN}$  high. This must occur 16 times to load all data bits into the shift registers. On the rising edge of  $\overline{CS}$ , data in the 16 shift registers is transferred as addressed and CLK is disabled.

There are three types of instructions: NOP, SET DAC, and set buffer modes.

#### No Operation

No Operation (NOP) is implemented when all 8 address pointer bits (A7-A0) and data bit D7 are logic 0. Data in D6-D0 is ignored. When this instruction is clocked in, no registers are updated and the outputs remain unchanged. NOP is a place-saver when multiple MAX528/MAX529s are daisy-chained.

#### SET DAC

SET DAC is implemented when at least one of the 8 address pointer bits (A7-A0) is logic 1. SET DAC updates the digital code of any or all DAC registers (and their corresponding DAC outputs) to a single new value. The new value is contained in the data byte (D7-D0). Each address pointer bit (A7-A0) selects a DAC output. Any combination of outputs can be updated simultaneously with one 16-bit instruction. Remember that address 0000 0000 is reserved for NOP and set buffer modes.

SET DAC does not change the buffer modes.

#### **Set Buffer Modes**

Set buffer modes is implemented when all 8 address pointer bits (A7-A0) are logic 0 and data bit D7 is 1. (see Table 1). Data in D6 is ignored. When this instruction is issued, data bits D5-D0 are transferred to the mode registers only; the DAC registers are unchanged.

Enabling and disabling the 8 buffers is done in four pairs by data bits D1, D2, D4, and D5. D1 controls buffers 6 and 7, D2 controls buffers 4 and 5, D4 controls buffers 2 and 3, and D5 controls buffers 0 and 1. A logic 1 enables a buffer pair (full-buffered or half-buffered mode); a logic 0 disables a buffer pair (unbuffered mode).

Full-buffered and half-buffered modes are set by two data bits, D0 and D3. D0 controls OUT4 through OUT7; D3 controls OUT0 through OUT3. A logic 1 enables full-buffered mode; a logic 0 enables half-buffered mode. These data bits apply only when buffer output pairs are enabled by a 1 in D1, D2, D4, or D5.

The set buffer modes instruction does not update the DAC registers.

**Programming Data**

### Table 2. Programming NOP

| Data Direction: | First: | >  |    |         |          |      |    |    |           |    |    |     |    |    |      | > Last   |  |  |

|-----------------|--------|----|----|---------|----------|------|----|----|-----------|----|----|-----|----|----|------|----------|--|--|

|                 |        |    | Ad | dress F | ointer l | 3its |    |    | Data Byte |    |    |     |    |    |      |          |  |  |

| Function        | A7     | A6 | A5 | A4      | А3       | A2   | A1 | A0 | D7        | D6 | D5 | D4_ | D3 | D2 | _D1  | _D0_     |  |  |

| NOP             | 0      | 0  | 0  | 0       | 0        | 0    | 0  | 0  | 0         | X  | X  | X   | X  | X  | _X _ | <u> </u> |  |  |

X = Don't Care

## Table 3. Programming SET DAC Outputs

|                 |        |                                                      | Ad | dress F | ointer E | 3its |    |    |    |    |    | Data | Byte |      |           |      |

|-----------------|--------|------------------------------------------------------|----|---------|----------|------|----|----|----|----|----|------|------|------|-----------|------|

| Function        | A7     | A6                                                   | A5 | A4      | АЗ       | A2   | A1 | A0 | D7 | D6 | D5 | D4   | D3   | _D2_ | _D1_      | D0 _ |

| SET DAC Outputs | A7     | A6                                                   | A5 | A4      | АЗ       | A2   | A1 | A0 | D7 | D6 | D5 | D4   | _D3_ | D2_  | <u>D1</u> | D0   |

| DAC 0000 0000   | 10 111 | 1111 1111 (00 Hov through FE Hov) D7 - MSR: D0 - LSR |    |         |          |      |    |    |    |    |    |      |      |      |           |      |

DAC code, 0000 0000 to 1111 1111 (00 Hex through FF Hex) D7 = MSB; D0 = LSB.

AX = set DAC register X to digital value D7-D0. A7 = OUT7...A0 = OUT0. Logic 1 sets the DAC register to new DAC code in D7-D0; logic 0 ignores D7-D0 code and keeps previous code. At least one of theses 8 bits must be 1 (A7-A0 = 01 hex to FF hex).

## Table 4. Programming Set Buffer Modes

|                  |    |             | Ad | dress F | ointer f | Bits |    |    | Data Byte |    |     |     |     |     |     |     |  |

|------------------|----|-------------|----|---------|----------|------|----|----|-----------|----|-----|-----|-----|-----|-----|-----|--|

| Function         | A7 | A6          | A5 | A4      | АЗ       | A2   | A1 | Α0 | D7        | D6 | D5  | D4  | D3  | D2  | D1  | D0  |  |

| Set Buffer Modes | 0  | 0 0 0 0 0 0 |    |         |          |      |    |    |           | X  | 0&1 | 2&3 | 0/3 | 4&5 | 6&7 | 4/7 |  |

X = Don't Care (D6)

0&1 (D5) = buffer enable for OUT0 and OUT1. Logic 1 = buffers enabled, 0 = buffers disabled (unbuffered mode). Similar remarks apply to 2&3 (D4), 4&5 (D2), and 6&7 (D1).

0/3 (D3) = buffer modes for OUT0-3. Logic 1 = full-buffered mode, 0 = half-buffered mode. D3 has no meaning when D4 and D5 are both 0.

4/7 (D0) = buffer modes for OUT4-7. Logic 1 = full-buffered mode, 0 = half-buffered mode. D0 has no meaning when D1 and D2 are both 0.

## **Programming Examples**

Example 1: Set OUT0, OUT2, OUT7 to binary value 0100 1110 (4E hex). Leave OUT1, OUT3, OUT4, OUT5, and OUT6 unchanged, and leave buffer states unchanged.

| Data Direction: | First | >  |    |    |    |    |    |    |    |    |    |    |      |        |    | > Last |

|-----------------|-------|----|----|----|----|----|----|----|----|----|----|----|------|--------|----|--------|

|                 | A7    | A6 | A5 | A4 | А3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | _D3_ | _ D2 _ | D1 | D0 .   |

| Example 1       | 1     | 0  | 0  | 0  | 0  | 1  | 0  | _1 | 0  | _1 | 0  | 0  | 1    | 1      | 1_ | 0      |

Example 2: Set all DACs except OUT6 to binary value 0000 0000 (00 hex). Leave OUT6 unchanged, and leave buffer states unchanged.

|           | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | _D1_ | _D0_ |  |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|------|--|

| Example 2 | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    |  |

# Example 3: Disable all buffers (unbuffered mode). Leave DAC data unchanged.

|                |   |    | ,  |    |    | ,  |    |    |    | _  |    |    |    |    |     |      |

|----------------|---|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|------|

|                |   | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1_ | D0 _ |

| Example 3      | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | X  | 0  | 0  | X  | 0  | 0   | X    |

| X = Don't Care |   |    |    |    |    |    |    |    |    |    |    |    |    |    |     |      |

Example 4: (1) Enable OUT0 and OUT1 buffers in full-buffered mode; put OUT2 and OUT3 in unbuffered mode. (2) Enable OUT6 and OUT7 buffers in half-buffered mode; put OUT4 and OUT5 in unbuffered mode. Leave DAC data unchanged.

| •         |    |    |    |    |    |    |    |    |    |    |     |    |    |    |     |        |

|-----------|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|-----|--------|

|           | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5  | D4 | D3 | D2 | D1_ | _ D0 _ |

| Example 4 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1_ | X  | _1_ | 0  | 1  | 0  | 1   | 0      |

X = Don't Care

Figure 5. Timing Diagram

# \_Ordering Information (continued)

| PART      | TEMP. RANGE     | PIN-PACKAGE    |

|-----------|-----------------|----------------|

| MAX529CPP | 0°C to +70°C    | 20 Plastic DIP |

| MAX529CWG | 0°C to +70°C    | 24 Wide SO     |

| MAX529CAG | 0°C to +70°C    | 24 SSOP        |

| MAX529C/D | 0°C to +70°C    | Dice*          |

| MAX529EPP | -40°C to +85°C  | 20 Plastic DIP |

| MAX529EWG | -40°C to +85°C  | 24 Wide SO     |

| MAX529EAG | -40°C to +85°C  | 24 SSOP        |

| MAX529MJP | -55°C to +125°C | 20 CERDIP**    |

- \* Contact factory for dice specifications.

- \*\* Contact factory for availability and processing to MIL-STD-883.

# Functional Diagram

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

# Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А