LTC4266A/LTC4266C

## Quad PoE/PoE+/LTPoE++ PSE Controller

### FEATURES

- Four Independent PSE Channels

- Compliant with IEEE 802.3at Type 1 and 2

- Low Power Dissipation

- **0.25**Ω Sense Resistance Per Channel

- Very High Reliability 4-Point PD Detection

- 2-Point Forced Voltage

- 2-Point Forced Current

- High Capacitance Legacy Device Detection

- 1MHz I<sup>2</sup>C Compatible Serial Control Interface

- Midspan Backoff Timer

- Supports 2-Pair and 4-Pair Output Power

- Available in Multiple Power Grades

- LTC4266A-1: LTPoE++<sup>TM</sup> 38.7W

- LTC4266A-2: LTPoE++ 52.7W

- LTC4266A-3: LTPoE++ 70W

- LTC4266A-4: LTPoE++ 90W

- LTC4266C: PoE 13W

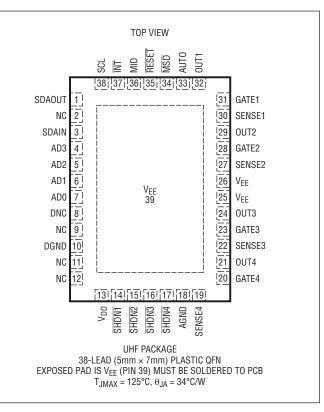

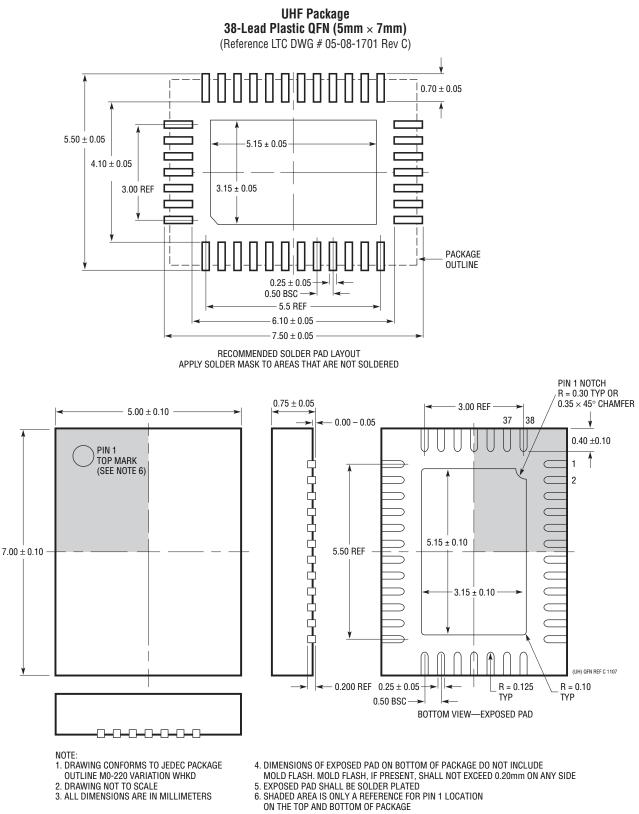

- Available in 38-Lead 5mm × 7mm QFN Package

### **APPLICATIONS**

- LTPoE++ PSE Switches/Routers

- LTPoE++ PSE Midspans

- IEEE 802.3at Type 1 PSE Switches/Routers

- IEEE 802.3at Type 1 PSE Midspans

### DESCRIPTION

The LTC<sup>®</sup>4266A is a quad power sourcing equipment (PSE) controller capable of delivering up to 90W of LTPoE++ power to a compatible LTPoE++ powered device (PD). A proprietary detection/classification scheme allows mutual identification between a LTPoE++ PSE and LTPoE++ PD while remaining compatible and interoperable with existing Type 1 (13W) and Type 2 (25.5W) PDs. The LTC4266A feature set is a superset of the popular LTC4266. These PSE controllers feature low R<sub>ON</sub> external MOSFETs and 0.25 $\Omega$  sense resistors which are especially important at the LTPoE++ current levels to maintain the lowest possible heat dissipation.

The LTC4266C targets fully automatic PSE systems powering Type 1 (up to 13W) PDs.

Advanced power management features include: 14-bit current monitoring ADCs, DAC-programmable current limit, and versatile quick shutdown of preselected ports. Advanced power management host software is available under a no-cost license. PD discovery uses a proprietary dual-mode 4-point detection mechanism ensuring excellent immunity from false PD detection. The LTC4266 includes an I<sup>2</sup>C serial interface operable up to 1MHz.

The LTC4266 is available in multiple power grades allowing delivered PD power of 13W, 25.5W, 38.7W, 52.7W, 70W and 90W. These controllers are available in a 38-lead 5mm  $\times$  7mm QFN package.

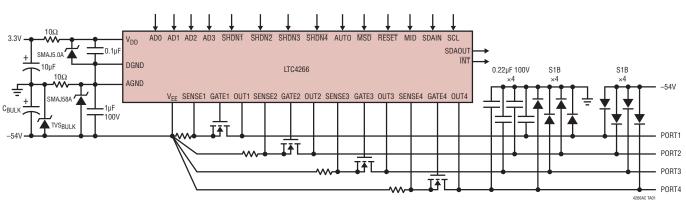

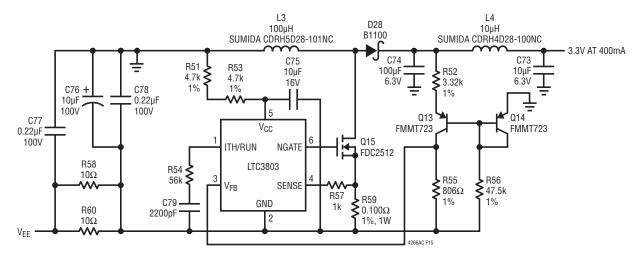

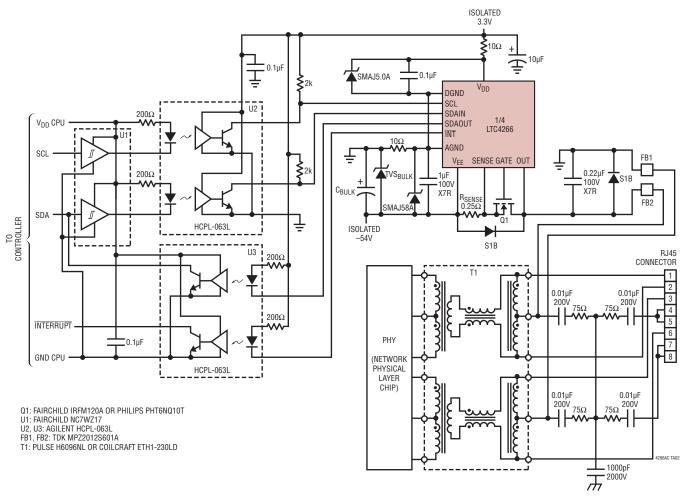

# TYPICAL APPLICATION

Complete 4-Port Ethernet High Power Source

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltages (Note 1)                              |

|-------------------------------------------------------|

| AGND – V <sub>EE</sub> –0.3V to 80V                   |

| DGND – V <sub>EE</sub> –0.3V to 80V                   |

| V <sub>DD</sub> – DGND –0.3V to 5.5V                  |

| Digital Pins                                          |

| SCL, SDAIN, SDAOUT, INT, SHDNn, MSD, ADn,             |

| RESET, AUTO, MID DGND –0.3V to V <sub>DD</sub> + 0.3V |

| Analog Pins                                           |

| GATEn, SENSEn, OUTn $V_{EE}$ –0.3V to $V_{EE}$ + 80V  |

| Operating Temperature Range                           |

| LTC4266I–40°C to 85°C                                 |

| Junction Temperature (Note 2) 125°C                   |

| Storage Temperature Range65°C to 150°C                |

| Lead Temperature (Soldering, 10 sec)                  |

## PIN CONFIGURATION

### ORDER INFORMATION http://www.linear.com/product/LTC4266A#orderinfo

| LEAD FREE FINISH   | TAPE AND REEL        | PART MARKING* | PACKAGE DESCRIPTION             | MAX PWR | TEMPERATURE RANGE |

|--------------------|----------------------|---------------|---------------------------------|---------|-------------------|

| LTC4266CIUHF#PBF   | LTC4266CIUHF#TRPBF   | 4266C         | 38-Lead (5mm × 7mm) Plastic QFN | 13W     | -40°C to 85°C     |

| LTC4266AIUHF-1#PBF | LTC4266AIUHF-1#TRPBF | 4266A1        | 38-Lead (5mm × 7mm) Plastic QFN | 38.7W   | -40°C to 85°C     |

| LTC4266AIUHF-2#PBF | LTC4266AIUHF-2#TRPBF | 4266A2        | 38-Lead (5mm × 7mm) Plastic QFN | 52.7W   | -40°C to 85°C     |

| LTC4266AIUHF-3#PBF | LTC4266AIUHF-3#TRPBF | 4266A3        | 38-Lead (5mm × 7mm) Plastic QFN | 70W     | -40°C to 85°C     |

| LTC4266AIUHF-4#PBF | LTC4266AIUHF-4#TRPBF | 4266A4        | 38-Lead (5mm × 7mm) Plastic QFN | 90W     | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C. AGND –  $V_{EE} = 54V$ , AGND = DGND, and  $V_{DD}$  – DGND = 3.3V unless otherwise noted. (Notes 3, 4)

| SYMBOL             | PARAMETER                                 | CONDITIONS                                                                                                                     |                         | MIN                                 | ТҮР                           | MAX                                 | UNITS                |

|--------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------|-------------------------------|-------------------------------------|----------------------|

| V <sub>EE</sub>    | Main PoE Supply Voltage                   | AGND – V <sub>EE</sub><br>For IEEE Type 1 Compliant Output<br>For IEEE Type 2 Compliant Output<br>For LTPoE++ Compliant Output | ● 45<br>● 51<br>● 54.75 |                                     |                               | 57<br>57<br>57                      | V<br>V<br>V          |

|                    | Undervoltage Lockout                      | AGND – V <sub>EE</sub>                                                                                                         |                         | 20                                  | 25                            | 30                                  | V                    |

| V <sub>DD</sub>    | V <sub>DD</sub> Supply Voltage            | V <sub>DD</sub> – DGND                                                                                                         |                         | 3.0                                 | 3.3                           | 4.3                                 | V                    |

|                    | Undervoltage Lockout                      |                                                                                                                                |                         |                                     | 2.2                           |                                     | V                    |

|                    | Allowable Digital Ground Offset           | DGND – V <sub>EE</sub>                                                                                                         |                         | 25                                  |                               | 57                                  | V                    |

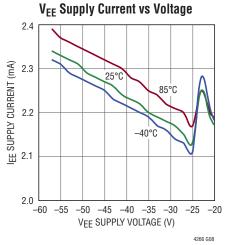

| I <sub>EE</sub>    | V <sub>EE</sub> Supply Current            | $(AGND - V_{EE}) = 55V$                                                                                                        |                         |                                     | -2.4                          | -5                                  | mA                   |

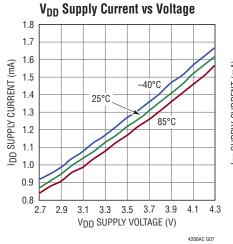

| I <sub>DD</sub>    | V <sub>DD</sub> Supply Current            | $(V_{DD} - DGND) = 3.3V$                                                                                                       |                         |                                     | 1.1                           | 3                                   | mA                   |

| Detection          | ·                                         |                                                                                                                                |                         |                                     |                               |                                     |                      |

|                    | Detection Current – Force Current         | First Point, AGND – V <sub>OUTn</sub> = 9V<br>Second Point, AGND – V <sub>OUTn</sub> = 3.5V                                    | •                       | 220<br>140                          | 240<br>160                    | 260<br>180                          | μA<br>μA             |

|                    | Detection Voltage – Force Voltage         | $\begin{array}{l} AGND-V_{OUTn},  5\mu A \leq I_{OUTn} \leq 500 \mu A \\ First Point \\ Second Point \end{array}$              | •                       | 7<br>3                              | 8<br>4                        | 9<br>5                              | V<br>V               |

|                    | Detection Current Compliance              | $AGND - V_{OUTn} = 0V$                                                                                                         |                         |                                     | 0.8                           | 0.9                                 | mA                   |

| V <sub>OC</sub>    | Detection Voltage Compliance              | AGND – V <sub>OUTn</sub> , Open Port                                                                                           |                         |                                     | 10.4                          | 12                                  | V                    |

|                    | Detection Voltage Slew Rate               | AGND – $V_{OUTn}$ , $C_{PORT} = 0.15 \mu F$                                                                                    |                         |                                     |                               | 0.01                                | V/µs                 |

|                    | Minimum Valid Signature Resistance        |                                                                                                                                |                         | 15.5                                | 17                            | 18.5                                | kΩ                   |

|                    | Maximum Valid Signature Resistance        |                                                                                                                                |                         | 27.5                                | 29.7                          | 32                                  | kΩ                   |

| Classificat        | tion                                      |                                                                                                                                |                         |                                     |                               |                                     |                      |

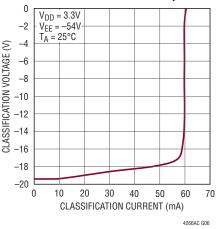

| V <sub>CLASS</sub> | Classification Voltage                    | $AGND - V_{OUTn}, 0mA \le I_{CLASS} \le 50mA$                                                                                  |                         | 16.0                                |                               | 20.5                                | V                    |

|                    | Classification Current Compliance         | V <sub>OUTn</sub> = AGND                                                                                                       |                         | 53                                  | 61                            | 67                                  | mA                   |

|                    | Classification Threshold Current          | Class 0 – 1<br>Class 1 – 2<br>Class 2 – 3<br>Class 3 – 4<br>Class 4 – Overcurrent                                              | •<br>•<br>•             | 5.5<br>13.5<br>21.5<br>31.5<br>45.2 | 6.5<br>14.5<br>23<br>33<br>48 | 7.5<br>15.5<br>24.5<br>34.9<br>50.8 | mA<br>mA<br>mA<br>mA |

| V <sub>MARK</sub>  | Classification Mark State Voltage         | $AGND - V_{OUTn}, 0.1mA \le I_{CLASS} \le 10mA$                                                                                |                         | 7.5                                 | 9                             | 10                                  | V                    |

|                    | Mark State Current Compliance             | V <sub>OUTn</sub> = AGND                                                                                                       |                         | 53                                  | 61                            | 67                                  | mA                   |

| Gate Drive         | er en |                                                                                                                                |                         |                                     |                               |                                     |                      |

|                    | GATE Pin Pull-Down Current                | Port Off, $V_{GATEn} = V_{EE} + 5V$<br>Port Off, $V_{GATEn} = V_{EE} + 1V$                                                     | •                       | 0.4<br>0.08                         | 0.12                          |                                     | mA<br>mA             |

|                    | GATE Pin Fast Pull-Down Current           | V <sub>GATEn</sub> = V <sub>EE</sub> + 5V                                                                                      |                         |                                     | 30                            |                                     | mA                   |

|                    | GATE Pin On Voltage                       | $V_{GATEn} - V_{EE}$ , $I_{GATEn} = 1 \mu A$                                                                                   |                         | 8                                   | 12                            | 14                                  | V                    |

| Output Vol         | ltage Sense                               |                                                                                                                                |                         |                                     |                               |                                     |                      |

| V <sub>PG</sub>    | Power Good Threshold Voltage              | V <sub>OUTn</sub> – V <sub>EE</sub>                                                                                            |                         | 2                                   | 2.4                           | 2.8                                 | V                    |

|                    | OUT Pin Pull-Up Resistance to AGND        | $0V \le (AGND - V_{OUTn}) \le 5V$                                                                                              |                         | 300                                 | 500                           | 700                                 | kΩ                   |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. AGND –  $V_{EE} = 54V$ , AGND = DGND, and  $V_{DD}$  – DGND = 3.3V unless otherwise noted. (Notes 3, 4)

| SYMBOL           | PARAMETER                                         | CONDITIONS                                                                                                                                                                                                                                                                                                                                           |             | MIN                   | ТҮР                   | MAX                   | UNITS                |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|-----------------------|-----------------------|----------------------|

| Current Se       | ense                                              |                                                                                                                                                                                                                                                                                                                                                      |             |                       |                       |                       |                      |

| V <sub>CUT</sub> | Overcurrent Sense Voltage                         | $V_{SENSEn} - V_{EE}$<br>hpen = 0Fh, cutn[5:0] $\geq$ 4 (Note 12)<br>cutrng = 0<br>cutrng = 1                                                                                                                                                                                                                                                        | •           | 9<br>4.5              | 9.38<br>4.69          | 9.75<br>4.88          | mV/LSB<br>mV/LSB     |

|                  | Overcurrent Sense in AUTO Pin Mode                | Class 0, Class 3<br>Class 1<br>Class 2<br>Class 4                                                                                                                                                                                                                                                                                                    | •<br>•<br>• | 90<br>26<br>49<br>152 | 94<br>28<br>52<br>159 | 98<br>30<br>55<br>166 | mV<br>mV<br>mV<br>mV |

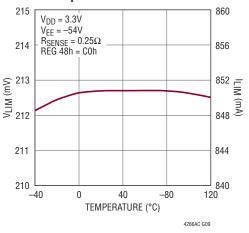

| V <sub>LIM</sub> | Active Current Limit in 802.3af Compliant<br>Mode | $\label{eq:VSENSEN} \begin{array}{l} V_{SENSEn} - V_{EE}, \ hpen = 0Fh, \ limn = 80h, \\ V_{EE} = 55V \ (Note \ 12) \\ V_{EE} < V_{OUT} < AGND - 29V \\ AGND - V_{OUT} = 0V \end{array}$                                                                                                                                                             | •           | 102<br>20             | 106                   | 110<br>50             | mV<br>mV             |

| V <sub>LIM</sub> | Active Current Limit in High Power Mode           | $\label{eq:hpen} \begin{array}{l} \text{hpen} = \text{OFh, limn} = \text{COh, } \text{V}_{\text{EE}} = 55\text{V} \\ \text{V}_{\text{OUT}} - \text{V}_{\text{EE}} = 0\text{V to } 10\text{V} \\ \text{V}_{\text{EE}} + 23\text{V} < \text{V}_{\text{OUT}} < \text{AGND} - 29\text{V} \\ \text{AGND} - \text{V}_{\text{OUT}} = 0\text{V} \end{array}$ | •           | 204<br>100<br>20      | 212<br>106            | 221<br>113<br>50      | mV<br>mV<br>mV       |

| V <sub>LIM</sub> | Active Current Limit in AUTO Pin Mode             | V <sub>OUT</sub> – V <sub>EE</sub> = 0V to 10V, V <sub>EE</sub> = 55V<br>Class 0 to Class 3<br>Class 4                                                                                                                                                                                                                                               | •           | 102<br>204            | 106<br>212            | 110<br>221            | mV<br>mV             |

| V <sub>MIN</sub> | DC Disconnect Sense Voltage                       | $V_{SENSEn} - V_{EE}$ , rdis = 0<br>$V_{SENSEn} - V_{EE}$ , rdis = 1                                                                                                                                                                                                                                                                                 | •           | 2.6<br>1.3            | 3.8<br>1.9            | 4.8<br>2.41           | mV<br>mV             |

| V <sub>SC</sub>  | Short-Circuit Sense                               | $V_{SENSEn} - V_{EE} - V_{LIM}$ , rdis = 0<br>$V_{SENSEn} - V_{EE} - V_{LIM}$ , rdis = 1                                                                                                                                                                                                                                                             | •           | 160<br>75             | 200<br>100            | 255<br>135            | mV<br>mV             |

| Port Curre       | ent ReadBack                                      |                                                                                                                                                                                                                                                                                                                                                      |             |                       |                       |                       |                      |

|                  | Resolution                                        | No Missing Codes, fast_iv = 0                                                                                                                                                                                                                                                                                                                        |             |                       | 14                    |                       | Bits                 |

|                  | LSB Weight                                        | V <sub>SENSEn</sub> – V <sub>EE</sub>                                                                                                                                                                                                                                                                                                                |             |                       | 30.5                  |                       | μV/LSB               |

|                  | 50Hz to 60Hz Noise Rejection                      | (Note 7)                                                                                                                                                                                                                                                                                                                                             |             |                       | 30                    |                       | dB                   |

| Port Volta       | ge ReadBack                                       |                                                                                                                                                                                                                                                                                                                                                      |             |                       |                       |                       |                      |

|                  | Resolution                                        | No Missing Codes, fast_iv = 0                                                                                                                                                                                                                                                                                                                        |             |                       | 14                    |                       | bits                 |

|                  | LSB Weight                                        | AGND – V <sub>OUTn</sub>                                                                                                                                                                                                                                                                                                                             |             |                       | 5.835                 |                       | mV/LSB               |

|                  | 50Hz to 60Hz Noise Rejection                      | (Note 7)                                                                                                                                                                                                                                                                                                                                             |             |                       | 30                    |                       | dB                   |

| Digital Int      | erface                                            |                                                                                                                                                                                                                                                                                                                                                      |             |                       |                       |                       | ·                    |

| V <sub>ILD</sub> | Digital Input Low Voltage                         | ADn, RESET, MSD, SHDNn, AUTO, MID<br>(Note 6)                                                                                                                                                                                                                                                                                                        | •           |                       |                       | 0.8                   | V                    |

|                  | I <sup>2</sup> C Input Low Voltage                | SCL, SDAIN (Note 6)                                                                                                                                                                                                                                                                                                                                  |             |                       |                       | 0.8                   | V                    |

| V <sub>IHD</sub> | Digital Input High Voltage                        | (Note 6)                                                                                                                                                                                                                                                                                                                                             | •           | 2.2                   |                       |                       | V                    |

|                  | Digital Output Low Voltage                        | $I_{SDAOUT} = 3mA, I_{\overline{INT}} = 3mA$<br>$I_{SDAOUT} = 5mA, I_{\overline{INT}} = 5mA$                                                                                                                                                                                                                                                         | •           |                       |                       | 0.4<br>0.7            | V<br>V               |

|                  | Internal Pull-Up to V <sub>DD</sub>               | ADn, SHDNn, RESET, MSD                                                                                                                                                                                                                                                                                                                               |             |                       | 50                    |                       | kΩ                   |

|                  | Internal Pull-Down to DGND                        | AUTO, MID                                                                                                                                                                                                                                                                                                                                            |             |                       | 50                    |                       | kΩ                   |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. AGND –  $V_{EE} = 54V$ , AGND = DGND, and  $V_{DD}$  – DGND = 3.3V unless otherwise noted. (Notes 3, 4)

| SYMBOL                 | PARAMETER                                              | CONDITIONS                                                                               |   | MIN | ТҮР  | MAX | UNITS |  |  |

|------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|---|-----|------|-----|-------|--|--|

| Timing Characteristics |                                                        |                                                                                          |   |     |      |     |       |  |  |

| t <sub>DET</sub>       | Detection Time                                         | Beginning to End of Detection (Note 7)                                                   | • | 270 | 290  | 310 | ms    |  |  |

| t <sub>DETDLY</sub>    | Detection Delay                                        | From PD Connected to Port to Detection<br>Complete (Note 7)                              | • | 300 |      | 470 | ms    |  |  |

| t <sub>CLE</sub>       | Class Event Duration                                   | (Note 7)                                                                                 |   |     | 12   |     | ms    |  |  |

| t <sub>CLEON</sub>     | Class Event Turn-On Duration                           | C <sub>PORT</sub> = 0.6µF (Note 7)                                                       | • |     |      | 0.1 | ms    |  |  |

| t <sub>ME</sub>        | Mark Event Duration                                    | (Notes 7, 11)                                                                            |   |     | 8.6  |     | ms    |  |  |

| t <sub>MEL</sub>       | Last Mark Event Duration                               | (Notes 7, 11)                                                                            | • | 16  | 22   |     | ms    |  |  |

| t <sub>PON</sub>       | Power On Delay in AUTO Pin Mode                        | From End of Valid Detect to Application of<br>Power to Port (Note 7)                     | • |     |      | 60  | ms    |  |  |

|                        | Turn On Rise Time                                      | (AGND – $V_{OUT}$ ): 10% to 90% of (AGND – $V_{EE}),$ $C_{PORT}$ = 0.15 $\mu F$ (Note 7) | • | 15  | 24   |     | μs    |  |  |

|                        | Turn On Ramp Rate                                      | $C_{PORT} = 0.15 \mu F$ (Note 7)                                                         |   |     |      | 10  | V/µs  |  |  |

|                        | Fault Delay                                            | From I <sub>CUT</sub> Fault to Next Detect                                               | • | 1.0 | 1.1  |     | S     |  |  |

|                        | Midspan Mode Detection Backoff                         | Rport = $15.5k\Omega$ (Note 7)                                                           |   | 2.3 | 2.5  | 2.7 | S     |  |  |

|                        | Power Removal Detection Delay                          | From Power Removal After t <sub>DIS</sub> to Next<br>Detect (Note 7)                     | • | 1.0 | 1.3  | 2.5 | S     |  |  |

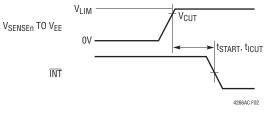

| t <sub>START</sub>     | Maximum Current Limit Duration During Port Start-Up    | (Note 7)                                                                                 | • | 52  | 62.5 | 66  | ms    |  |  |

| t <sub>LIM</sub>       | Maximum Current Limit Duration After Port<br>Start-Up  | t <sub>LIM</sub> Enable = 1 (Notes 7, 12)                                                | • |     | 11.9 |     | ms    |  |  |

| t <sub>CUT</sub>       | Maximum Overcurrent Duration After Port<br>Start-Up    | (Note 7)                                                                                 | • | 52  | 62.5 | 66  | ms    |  |  |

|                        | Maximum Overcurrent Duty Cycle                         | (Note 7)                                                                                 | • | 5.8 | 6.3  | 6.7 | %     |  |  |

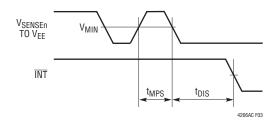

| t <sub>MPS</sub>       | Maintain Power Signature (MPS) Pulse Width Sensitivity | Current Pulse Width to Reset Disconnect<br>Timer (Notes 7, 8)                            | • | 1.6 |      | 3.6 | ms    |  |  |

| t <sub>DIS</sub>       | Maintain Power Signature (MPS) Dropout Time            | (Note 7)                                                                                 |   | 320 | 350  | 380 | ms    |  |  |

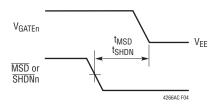

| t <sub>MSD</sub>       | Masked Shut Down Delay                                 | (Note 7)                                                                                 | • |     |      | 6.5 | μs    |  |  |

| t <sub>SHDN</sub>      | Port Shut Down Delay                                   | (Note 7)                                                                                 | • |     |      | 6.5 | μs    |  |  |

|                        | I <sup>2</sup> C Watchdog Timer Duration               |                                                                                          | • | 1.5 | 2    | 3   | S     |  |  |

|                        | Minimum Pulse Width for Masked Shut Down               | (Note 7)                                                                                 | • | 3   |      |     | μs    |  |  |

|                        | Minimum Pulse Width for SHDN                           | (Note 7)                                                                                 |   | 3   |      |     | μs    |  |  |

|                        | Minimum Pulse Width for RESET                          | (Note 7)                                                                                 |   | 4.5 |      |     | μs    |  |  |

### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. AGND - V<sub>EE</sub> = 54V, AGND = DGND, and V<sub>DD</sub> - DGND = 3.3V unless otherwise noted. (Notes 3, 4)

| SYMBOL                  | PARAMETER                     | CONDITIONS                                               |   | MIN | ТҮР | MAX | UNITS    |

|-------------------------|-------------------------------|----------------------------------------------------------|---|-----|-----|-----|----------|

| I <sup>2</sup> C Timing |                               |                                                          |   | 1   |     |     |          |

|                         | Clock Frequency               | (Note 7)                                                 | • |     |     | 1   | MHz      |

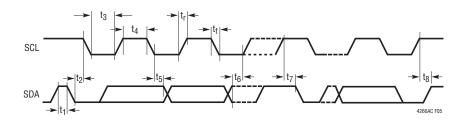

| t <sub>1</sub>          | Bus Free Time                 | Figure 5 (Notes 7, 9)                                    | • | 480 |     |     | ns       |

| t <sub>2</sub>          | Start Hold Time               | Figure 5 (Notes 7, 9)                                    | • | 240 |     |     | ns       |

| t <sub>3</sub>          | SCL Low Time                  | Figure 5 (Notes 7, 9)                                    | • | 480 |     |     | ns       |

| t <sub>4</sub>          | SCL High Time                 | Figure 5 (Notes 7, 9)                                    | • | 240 |     |     | ns       |

| t <sub>5</sub>          | Data Hold Time                | Figure 5 (Notes 7, 9) Data into Chip<br>Data Out of Chip | • | 60  |     | 120 | ns<br>ns |

| t <sub>6</sub>          | Data Set-Up Time              | Figure 5 (Notes 7, 9)                                    | • | 80  |     |     | ns       |

| t <sub>7</sub>          | Start Set-Up Time             | Figure 5 (Notes 7, 9)                                    | • | 240 |     |     | ns       |

| t <sub>8</sub>          | Stop Set-Up Time              | Figure 5 (Notes 7, 9)                                    | • | 240 |     |     | ns       |

| t <sub>r</sub>          | SCL, SDAIN Rise Time          | Figure 5 (Notes 7, 9)                                    | • |     |     | 120 | ns       |

| t <sub>f</sub>          | SCL, SDAIN Fall Time          | Figure 5 (Notes 7, 9)                                    | • |     |     | 60  | ns       |

|                         | Fault Present to INT Pin Low  | (Notes 7, 9, 10)                                         | • |     |     | 150 | ns       |

|                         | Stop Condition to INT Pin Low | (Notes 7, 9, 10)                                         | • |     |     | 1.5 | μs       |

|                         | ARA to INT Pin High Time      | (Notes 7, 9)                                             | • |     |     | 1.5 | μs       |

|                         | SCL Fall to ACK Low           | (Notes 7, 9)                                             | • |     |     | 120 | ns       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 140°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 3: All currents into device pins are positive; all currents out of device pins are negative.

Note 4: The LTC4266A/LTC4266C operates with a negative supply voltage (with respect to ground). To avoid confusion, voltages in this data sheet are referred to in terms of absolute magnitude.

Note 5: t<sub>DIS</sub> is the same as t<sub>MPDO</sub> defined by IEEE 802.3at.

Note 6: The LTC4266A/LTC4266C digital interface operates with respect to DGND. All logic levels are measured with respect to DGND.

Note 7: Guaranteed by design, not subject to test.

Note 8: The IEEE 802.3af specification allows a PD to present its Maintain Power Signature (MPS) on an intermittent basis without being disconnected. In order to stay powered, the PD must present the MPS for  $t_{\text{MPS}}$  within any  $t_{\text{MPDO}}$  time window.

Note 9: Values measured at  $V_{ILD(MAX)}$  and  $V_{IHD(MIN)}$ .

**Note 10:** If fault condition occurs during an  $I^2C$  transaction, the INT pin will not be pulled down until a stop condition is present on the I<sup>2</sup>C bus. Note 11: Load Characteristic of the LTC4266A/LTC4266C during Mark:

$7V < (AGND - V_{OUTn}) < 10V \text{ or } I_{OUT} < 50 \mu A$

Note 12: See the LTC4266A/LTC4266C Software Programming documentation for information on serial bus usage and device configuration and status registers.

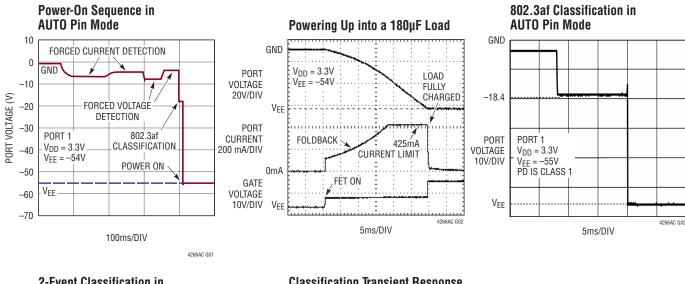

### **TYPICAL PERFORMANCE CHARACTERISTICS**

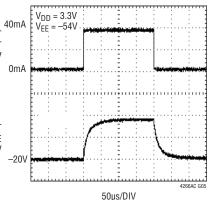

Classification Transient Response to 40mA Load Step

**Classification Current Compliance**

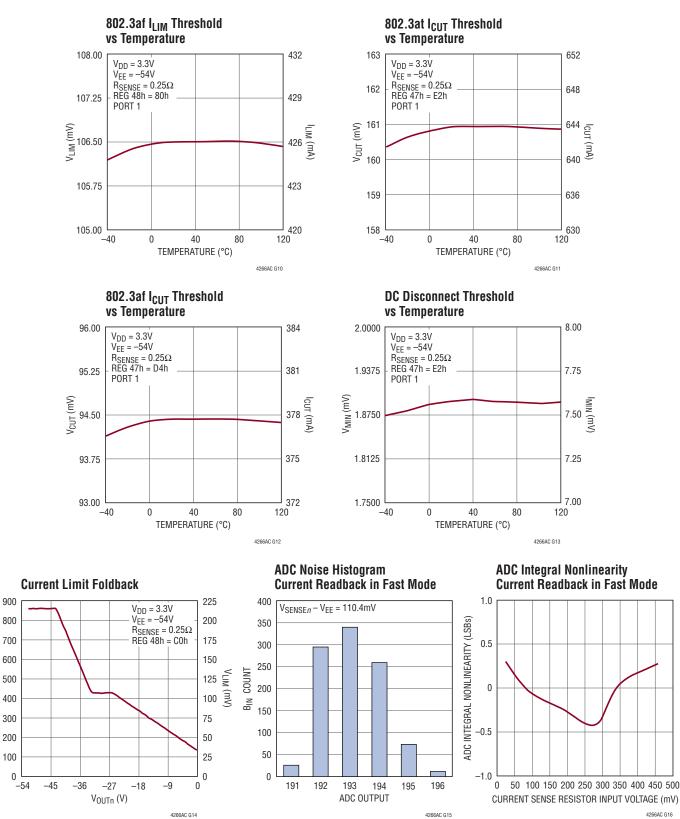

802.3at I<sub>LIM</sub> Threshold vs Temperature

4266acfe

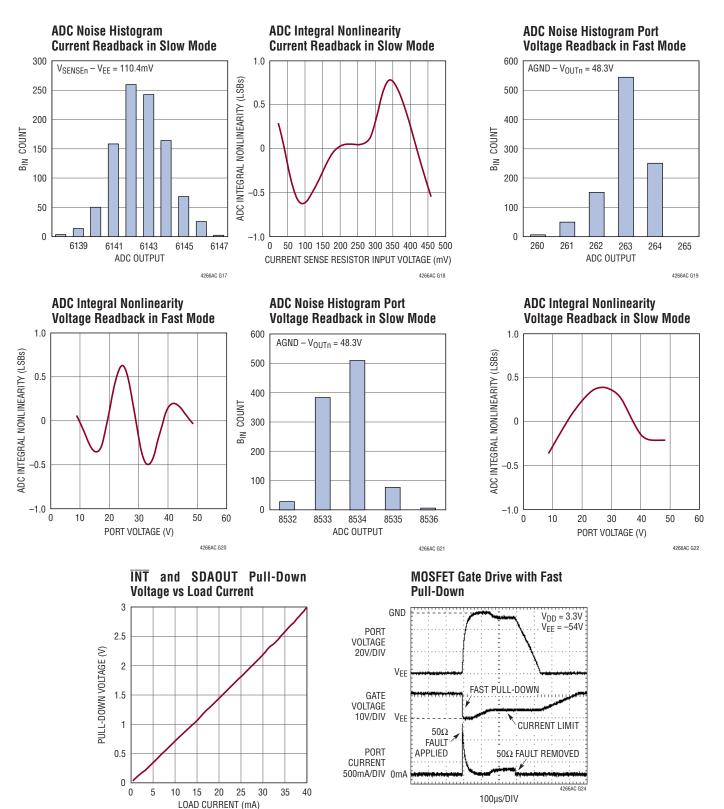

### **TYPICAL PERFORMANCE CHARACTERISTICS**

4266acfe

900

ILIM (mA)

### **TYPICAL PERFORMANCE CHARACTERISTICS**

4266AC G23

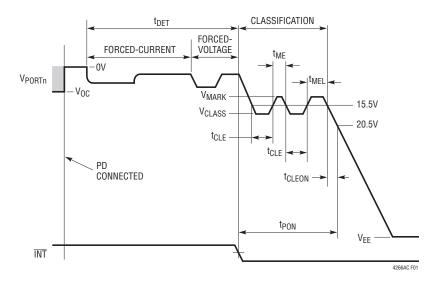

# **TEST TIMING DIAGRAMS**

Figure 1. Detect, Class and Turn-On Timing in AUTO Pin or Semi-Auto Modes

Figure 3. DC Disconnect Timing

### **TEST TIMING DIAGRAMS**

Figure 5. I<sup>2</sup>C Interface Timing

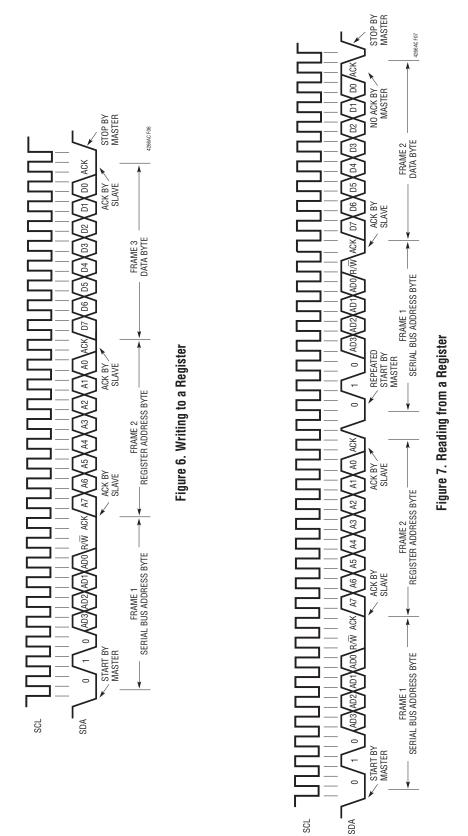

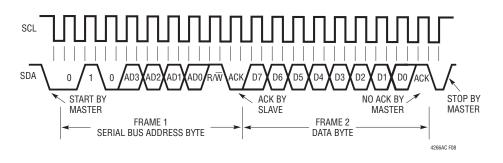

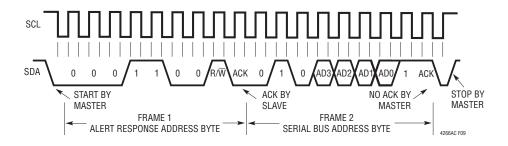

# I<sup>2</sup>C TIMING DIAGRAMS

# I<sup>2</sup>C TIMING DIAGRAMS

Figure 8. Reading the Interrupt Register (Short Form)

Figure 9. Reading from Alert Response Address

4266acfe

### PIN FUNCTIONS

**RESET:** Chip Reset, Active Low. When the RESET pin is low, the LTC4266A/LTC4266C is held inactive with all ports off and all internal registers reset to their powerup states. When RESET is pulled high, the LTC4266A/ LTC4266C begins normal operation. RESET can be connected to an external capacitor or RC network to provide a power turn-on delay. Internal filtering of the RESET pin prevents glitches less than 1µs wide from resetting the LTC4266A/LTC4266C. Internally pulled up to V<sub>DD</sub>.

**MID:** Midspan Mode Input. When high, the LTC4266A/ LTC4266C acts as a midspan device. Internally pulled down to DGND.

**INT**: Interrupt Output, Open Drain. **INT** will pull low when any one of several events occur in the LTC4266A/ LTC4266C. It will return to a high impedance state when bits 6 or 7 are set in the Reset PB register (1Ah). The **INT** signal can be used to generate an interrupt to the host processor, eliminating the need for continuous software polling. Individual **INT** events can be disabled using the Int Mask register (01h). See the LTC4266A/LTC4266C Software Programming documentation for more information. The **INT** pin is only updated between I<sup>2</sup>C transactions.

**SCL:** Serial Clock Input. High impedance clock input for the I<sup>2</sup>C serial interface bus. SCL must be tied high if not used.

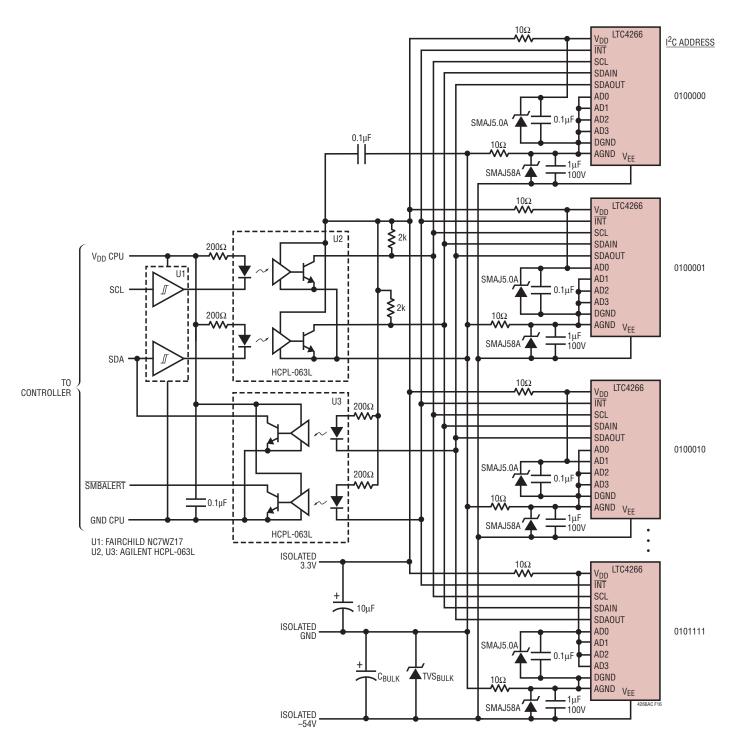

**SDAOUT:** Serial Data Output, Open Drain Data Output for the I<sup>2</sup>C Serial Interface Bus. The LTC4266A/LTC4266C uses two pins to implement the bidirectional SDA function to simplify opto-isolation of the I<sup>2</sup>C bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. SDAOUT should be grounded or left floating if not used. See the Applications Information section for more information.

**SDAIN:** Serial Data Input. High impedance data input for the  $I^2C$  serial interface bus. The LTC4266A/LTC4266C uses two pins to implement the bidirectional SDA function to simplify opto-isolation of the  $I^2C$  bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. SDAIN must be tied high if not used. See the Applications Information section for more information. **AD3:** Address Bit 3. Tie the address pins high or low to set the  $I^2C$  serial address to which the LTC4266A/LTC4266C responds. This address will be  $010A_3A_2A_1A_0b$ . Internally pulled up to  $V_{DD}$ .

AD2: Address Bit 2. See AD3.

AD1: Address Bit 1. See AD3.

ADO: Address Bit 0. See AD3.

**NC, DNC:** All pins identified with "NC" or "DNC" must be left unconnected.

**DGND:** Digital Ground. DGND is the return for the  $V_{\text{DD}}$  supply.

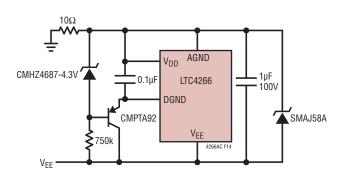

$V_{DD}$ : Logic Power Supply. Connect to a 3.3V power supply relative to DGND.  $V_{DD}$  must be bypassed to DGND near the LTC4266A/LTC4266C with at least a 0.1µF capacitor.

**SHDN1**: Shutdown Port 1, Active Low. When pulled low, SHDN1 shuts down port 1, regardless of the state of the internal registers. Pulling SHDN1 low is equivalent to setting the Reset Port 1 bit in the Reset Pushbutton register (1Ah). Internal filtering of the SHDN1 pin prevents glitches less than 1 $\mu$ s wide from resetting the port. Internally pulled up to V<sub>DD</sub>.

**SHDN2**: Shutdown Port 2, Active Low. See SHDN1.

**SHDN3**: Shutdown Port 3, Active Low. See SHDN1.

**SHDN4:** Shutdown Port 4, Active Low. See SHDN1.

**AGND:** Analog Ground. AGND is the return for the  $\mathsf{V}_{\mathsf{EE}}$  supply.

**SENSE4:** Port 4 Current Sense Input. SENSE4 monitors the external MOSFET current via a  $0.5\Omega$  or  $0.25\Omega$  sense resistor between SENSE4 and V<sub>EE</sub>. Whenever the voltage across the sense resistor exceeds the overcurrent detection threshold V<sub>CUT</sub>, the current limit fault timer counts up. If the voltage across the sense resistor reaches the current limit threshold V<sub>LIM</sub>, the GATE4 pin voltage is lowered to maintain constant current in the external MOSFET. See the Applications Information section for further details. If the port is unused, the SENSE4 pin must be tied to V<sub>EE</sub>.

### PIN FUNCTIONS

**GATE4:** Port 4 Gate Drive. GATE4 should be connected to the gate of the external MOSFET for port 4. When the MOSFET is turned on, the gate voltage is driven to 12V (typ) above  $V_{EE}$ . During a current limit condition, the voltage at GATE4 will be reduced to maintain constant current through the external MOSFET. If the fault timer expires, GATE4 is pulled down, turning the MOSFET off and recording a t<sub>CUT</sub> or t<sub>START</sub> event. If the port is unused, float the GATE4 pin.

**OUT4:** Port 4 Output Voltage Monitor. OUT4 should be connected to the output port. A current limit foldback circuit limits the power dissipation in the external MOSFET by reducing the current limit threshold when the drain-to-source voltage exceeds 10V. The port 4 Power Good bit is set when the voltage from OUT4 to  $V_{EE}$  drops below 2.4V (typ). A 500k resistor is connected internally from OUT4 to AGND when the port is idle. If the port is unused, OUT4 pin must be floated.

**SENSE3:** Port 3 Current Sense Input. See SENSE4.

GATE3: Port 3 Gate Drive. See GATE4.

**OUT3:** Port 3 Output Voltage Monitor. See OUT4.

$V_{EE}$ : Main Supply Input. Connect to a -45V to -57V supply, relative to AGND.

SENSE2: Port 2 Current Sense Input. See SENSE4.

GATE2: Port 2 Gate Drive. See GATE4.

**OUT2:** Port 2 Output Voltage Monitor. See OUT4.

**SENSE1:** Port 1 Current Sense Input. See SENSE4.

GATE1: Port 1 Gate Drive. See GATE 4.

**OUT1:** Port 1 Output Voltage Monitor. See OUT4.

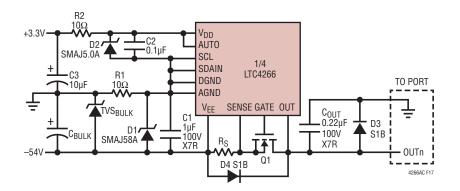

**AUTO:** AUTO Pin Mode Input. AUTO pin mode allows the LTC4266A/LTC4266C to detect and power up a PD even if there is no host controller present on the  $I^2C$ bus. The voltage of the AUTO pin determines the state of the internal registers when the LTC4266A/LTC4266C is reset or comes out of V<sub>DD</sub> UVLO (see the LTC4266A/ LTC4266C Software Programming documentation). The states of these register bits can subsequently be changed via the  $I^2C$  interface. The real-time state of the AUTO pin is read at bit 0 in the Pin Status register (11h). Internally pulled down to DGND. Must be tied locally to either V<sub>DD</sub> or DGND.

**MSD**: Maskable Shutdown Input. Active low. When pulled low, all ports that have their corresponding mask bit set in the Misc Config register (17h) will be reset, equivalent to pulling the SHDN pin low. Internal filtering of the MSD pin prevents glitches less than 1µs wide from resetting ports. Internally pulled up to V<sub>DD</sub>.

# OPERATION

#### Overview

Power over Ethernet, or PoE, is a standard protocol for sending DC power over copper Ethernet data wiring. The IEEE group that administers the 802.3 Ethernet data standards added PoE powering capability in 2003. This original PoE spec, known as 802.3af, allowed for 48V DC power at up to 13W. This initial spec was widely popular, but 13W was not adequate for some requirements. In 2009, the IEEE released a new standard, known as 802.3at or PoE+, increasing the voltage and current requirements to provide 25W of power.

The IEEE standard also defines PoE terminology. A device that provides power to the network is known as a PSE, or power sourcing equipment, while a device that draws power from the network is known as a PD, or powered device. PSEs come in two types: Endpoints (typically network switches or routers), which provide data and power; and Midspans, which provide power but pass through data. Midspans are typically used to add PoE capability to existing non-PoE networks. PDs are typically IP phones, wireless access points, security cameras, and similar devices.

#### PoE++ Evolution

Even during the process of creating the IEEE PoE+ 25.5W specification, it became clear that there was a significant and increasing need for more than 25.5W of delivered power. The LTC4266A family responds to this market by allowing a reliable means of providing up to 90W of delivered power to a LTPoE++ PD. The LTPoE++ specification provides reliable detection and classification extensions to the existing IEEE PoE technique that are backward compatible and interoperable with existing Type 1 and Type 2 PDs. Unlike other proprietary PoE++ solutions, Linear's LTPoE++ solution provides mutual identification between the PSE and PD. This ensures that the LTPoE++ PD knows it may use the requested power at start-up because it has detected a LTPoE++ PSE. LTPoE++ PSEs can differentiate between a LTPoE++ PD and all other types of IEEE compliant PDs allowing LTPoE++ PSEs to remain compliant and interoperable with existing equipment.

### LTC4266 Product Family

The LTC4266 is a third-generation quad PSE controller that implements four PSE ports in either an end-point or midspan design. Virtually all necessary circuitry is included to implement an IEEE 802.3at compliant PSE design, requiring only an external power MOSFET and sense resistor per channel; these minimize power loss compared to alternative designs with on-board MOSFETs and increase system reliability in the event a single channel fails.

The LTC4266 comes in three grades which support different PD power levels.

The A-grade LTC4266 extends PoE power delivery capabilities to LTPoE++ levels. LTPoE++ is a Linear Technology proprietary specification allowing for the delivery of up to 90W to LTPoE++ compliant PDs. The LTPoE++ architecture extends the IEEE physical power negotiation to include 38.7W, 52.7W, 70W and 90W power levels. The A-grade LTC4266 also incorporates all B- and C-grade features.

The B-grade LTC4266 is a fully IEEE-compliant Type 2 PSE supporting autonomous detection, classification and powering of Type 1 and Type 2 PDs. The B-grade LTC4266 also incorporates all C-grade features. The B-grade LTC4266 is marketed and numbered without the B suffix for legacy reasons; the absence of power grade suffix infers a B-grade part.

The C-grade LTC4266 is a fully autonomous 802.3at Type 1 PSE solution. Intended for use only in AUTO pin mode, the C-grade chipset autonomously supports detection, classification and powering of Type 1 PDs. As a Type 1 PSE, 2-event classification is prohibited and Class 4 PDs are automatically treated as Class 0 PDs.

### **PoE Basics**

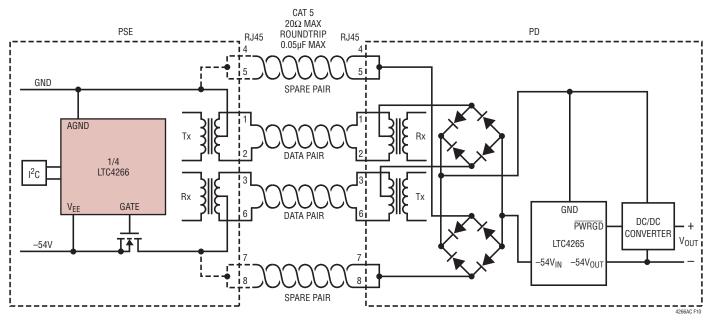

Common Ethernet data connections consist of two or four twisted pairs of copper wire (commonly known as CAT-5 cable), transformer-coupled at each end to avoid ground loops. PoE systems take advantage of this coupling arrangement by applying voltage between the center-taps of the data transformers to transmit power from the PSE

### OPERATION

Figure 10. Power Over Ethernet System Diagram

to the PD without affecting data transmission. Figure 10 shows a high-level PoE system schematic.

To avoid damaging legacy data equipment that does not expect to see DC voltage, the PoE spec defines a protocol that determines when the PSE may apply and remove power. Valid PDs are required to have a specific 25k common-mode resistance at their input. When such a PD is connected to the cable, the PSE detects this signature resistance and turns on the power. When the PD is later disconnected, the PSE senses the open circuit and turns power off. The PSE also turns off power in the event of a current fault or short-circuit.

When a PD is detected, the PSE optionally looks for a classification signature that tells the PSE the maximum power the PD will draw. The PSE can use this information to allocate power among several ports, police the current consumption of the PD, or to reject a PD that will draw more power that the PSE has available. For a 802.3af PSE, the classification step is optional; if a PSE chooses not to classify a PD, it must assume that the PD is a 13W (full 802.3af power) device.

#### New in 802.3at

The newer 802.3at standard supersedes 802.3af and brings several new features:

- A PD may draw as much as 25.5W. Such PDs (and the PSEs that support them) are known as Type 2. Older 13W 802.3af equipment is classified as Type 1. Type 1 PDs will work with all PSEs; Type 2 PDs may require Type 2 PSEs to work properly. The LTC4266A/ LTC4266C is designed to work in both Type 1 and Type 2 PSE designs, and also supports non-standard configurations at higher power levels.

- The Classification protocol is expanded to allow Type 2 PSEs to detect Type 2 PDs, and to allow Type 2 PDs to determine if they are connected to a Type 2 PSE. Two versions of the new Classification protocol are available: an expanded version of the 802.3af Class Pulse protocol, and an alternate method integrated with the existing LLDP protocol (using the Ethernet data path). The LTC4266A/LTC4266C fully supports the new Class Pulse protocol (which is implemented in the data communications layer, not in the PoE circuitry).

4266acfe

# OPERATION

• Fault protection current levels and timing are adjusted to reduce peak power in the MOSFET during a fault; this allows the new 25.5W power levels to be reached using the same MOSFETs as older 13W designs.

#### Extended Power LTPoE++

The LTC4266A adds the capability to autonomously deliver up to 90W of power to the PD. LTPoE++ PDs may forgo 802.3 LLDP support and rely solely on the LTPoE++ Physical Classification to negotiate power with LTPoE++ PSEs; this greatly simplifies high-power PD implementations.

LTPoE++ classification may be optionally enabled for the LTC4266A by setting both the High Power Enable and LTPoE++ Enable bits.

The higher levels of LTPoE++ delivery impose additional layout and component selection constraints. The LTC4266A is offered in 4 power levels (-1, -2, -3, and -4) which allows the AUTO pin mode LTC4266A to autonomously power up to supported power levels. If the AUTO pin is high, internal circuitry determines the maximum deliverable power. PDs requesting more than the available power limits are not powered.

# Table 1. LTPoE++ Auto Pin Mode Maximum Delivered Power Capabilities

| PART       | PAIRS | PD POWER |

|------------|-------|----------|

| LTC4266A-1 | 4     | 38.7W    |

| LTC4266A-2 | 4     | 52.7W    |

| LTC4266A-3 | 4     | 70W      |

| LTC4266A-4 | 4     | 90W      |

#### **Operating Modes**

The LTC4266A/LTC4266C include four independent ports, each of which can operate in one of four modes: manual, semi-auto, AUTO pin, or shutdown.

| MODE      | AUTO<br>Pin | OPMD | DETECT/<br>CLASS     | POWER-UP        | AUTOMATIC<br>I <sub>cut</sub> /I <sub>lim</sub><br>Assignment |

|-----------|-------------|------|----------------------|-----------------|---------------------------------------------------------------|

| AUTO Pin  | 1           | 11b  | Enabled at<br>Reset  | Automatically   | Yes                                                           |

| Reserved  | 0           | 11b  | N/A                  | N/A             | N/A                                                           |

| Semi-auto | 0           | 10b  | Host<br>Enabled      | Upon<br>Request | No                                                            |

| Manual    | 0           | 01b  | Once Upon<br>Request | Upon<br>Request | No                                                            |

| Shutdown  | 0           | 00b  | Disabled             | Disabled        | No                                                            |

- In manual mode, the port waits for instructions from the host system before taking any action. It runs a single detection or classification cycle when commanded to by the host, and reports the result in its Port Status register. The host system can command the port to turn on or off the power at any time. This mode should only be used for diagnostic and test purposes.

- In semi-auto mode, the port repeatedly attempts to detect and classify any PD attached to it. It reports the status of these attempts back to the host, and waits for a command from the host before turning on power to the port. The host must enable detection (and optionally classification) for the port before detection will start.

- AUTO pin mode operates the same as semi-auto mode except that it will automatically turn on the power to the port if detection is successful. In AUTO pin mode, I<sub>CUT</sub> and I<sub>LIM</sub> values are set automatically by the LTC4266A/LTC4266C. This operational mode is only valid if the AUTO pin is high at reset or powerup and remains high during operation.

- In shutdown mode, the port is disabled and will not detect or power a PD.

Regardless of which mode it is in, the LTC4266A/ LTC4266C will remove power automatically from any port that generates a current limit fault. It will also automatically remove power from any port that generates a disconnect event if disconnect detection is enabled. The host controller may also command the port to remove power at any time.

#### **Reset and the AUTO/MID Pins**

The initial LTC4266A/LTC4266C configuration depends on the state of the AUTO and MID pins during reset. Reset occurs at power-up, or whenever the RESET pin is pulled low or the global Reset All bit is set. Changing the state of AUTO or MID after power-up will not properly change the port behavior of the LTC4266A/LTC4266C until a reset occurs.

Although typically used with a host controller, the LTC4266A/LTC4266C can also be used in a standalone mode with no connection to the serial interface. If there is no host present, the AUTO pin must be tied high so that, at reset, all ports will be configured to operate automatically. Each port will detect and classify repeatedly until a PD is discovered, set  $I_{CUT}$  and  $I_{LIM}$  according to the classification results, apply power after successful detection, and remove power when a PD is disconnected.

Table 3 shows the  $I_{CUT}$  and  $I_{LIM}$  values that will be automatically set in standalone (AUTO pin) mode, based on the discovered class.

| Table 3. I <sub>CUT</sub> and I <sub>LIM</sub> | Values in Standalone | AUTO Pin Mode |

|------------------------------------------------|----------------------|---------------|

|------------------------------------------------|----------------------|---------------|

| CLASS              | I <sub>CUT</sub> | I <sub>LIM</sub> |

|--------------------|------------------|------------------|

| Class 1            | 112mA            | 425mA            |

| Class 2            | 206mA            | 425mA            |

| Class 3 or Class 0 | 375mA            | 425mA            |

| Class 4            | 638mA            | 850mA            |

The automatic setting of the  $I_{CUT}$  and  $I_{LIM}$  values only occurs if the LTC4266A/LTC4266C is reset with the AUTO pin high.

If the standalone application is a midspan, the MID pin must be tied high to enable correct midspan detection timing.

#### DETECTION

#### **Detection Overview**

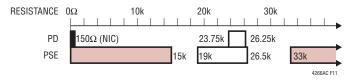

To avoid damaging network devices that were not designed to tolerate DC voltage, a PSE must determine whether the connected device is a real PD before applying power. The IEEE specification requires that a valid PD have a common-mode resistance of  $25k \pm 5\%$  at any port voltage below 10V. The PSE must accept resistances that fall between 19k and 26.5k, and it must reject resistances above 33k or below 15k (shaded regions in Figure 11). The PSE may choose to accept or reject resistances in

Figure 11. IEEE 802.3af Signature Resistance Ranges

the undefined areas between the must-accept and mustreject ranges. In particular, the PSE must reject standard computer network ports, many of which have  $150\Omega$  common-mode termination resistors that will be damaged if power is applied to them (the black region at the left of Figure 11).

### 4-Point Detection

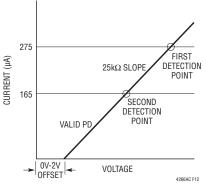

The LTC4266A/LTC4266C uses a 4-point detection method to discover PDs. False-positive detections are minimized by checking for signature resistance with both forcedcurrent and forced-voltage measurements. Initially, two test currents are forced onto the port (via the OUTn pin) and the resulting voltages are measured. The detection

Figure 12. PD Detection

circuitry subtracts the two V-I points to determine the resistive slope while removing offset caused by series diodes or leakage at the port (see Figure 12). If the forcedcurrent detection yields a valid signature resistance, two test voltages are then forced onto the port and the resulting currents are measured and subtracted. Both methods must report valid resistances for the port to report a valid detection. PD signature resistances between 17k and 29k (typically) are detected as valid and reported as Detect Good in the corresponding Port Status register. Values outside this range, including open and short-circuits, are also reported. If the port measures less than 1V at the first forced-current test, the detection cycle will abort and Short Circuit will be reported. Table 4 shows the possible detection results.

| MEASURED PD SIGNATURE        | DETECTION RESULT                  |  |

|------------------------------|-----------------------------------|--|

| Incomplete or Not Yet Tested | Detect Status Unknown             |  |

| <2.4k                        | Short Circuit                     |  |

| Capacitance > 2.7µF          | C <sub>PD</sub> Too High          |  |

| 2.4k < R <sub>PD</sub> < 17k | R <sub>SIG</sub> Too Low          |  |

| 17k < R <sub>PD</sub> < 29k  | Detect Good                       |  |

| >29k                         | R <sub>SIG</sub> Too High         |  |

| >50k                         | Open Circuit                      |  |

| Voltage > 10V                | Port Voltage Outside Detect Range |  |

|                              |                                   |  |

#### **More On Operating Modes**

The port's operating mode determines when the LTC4266A/LTC4266C runs a detection cycle. In manual mode, the port will idle until the host orders a detect cycle. It will then run detection, report the results, and return to idle to wait for another command.

In semi-auto mode, the LTC4266A/LTC4266C autonomously polls a port for PDs, but it will not apply power until commanded to do so by the host. The Port Status register is updated at the end of each detection cycle. If a valid signature resistance is detected and classification is enabled, the port will classify the PD and report that result as well. The port will then wait for at least 100ms (or 2 seconds if midspan mode is enabled), and will repeat the detection cycle to ensure that the data in the Port Status register is up-to-date.

4266acfe

If the port is in semi-auto mode and high power operation is enabled, the port will not turn on in response to a power-on command unless the current detect result is Detect Good. Any other detect result will generate a  $t_{START}$ fault if a power-on command is received. If the port is not in high power mode, it will ignore the detection result and apply power when commanded, maintaining backwards compatibility with the LTC4259A.

Behavior in AUTO pin mode is similar to semi-auto; however, after Detect Good is reported and the port is classified (if classification is enabled), it is automatically powered on without further intervention. In standalone (AUTO pin) mode, the I<sub>CUT</sub> and I<sub>LIM</sub> thresholds are automatically set; see the Reset and the AUTO/MID Pin section for more information.

The signature detection circuitry is disabled when the port is initially powered up with the AUTO pin low, in shutdown mode, or when the corresponding Detect Enable bit is cleared.

#### **Detection of Legacy PDs**

Proprietary PDs that predate the original IEEE 802.3af standard are commonly referred to today as legacy devices. One type of legacy PD uses a large common-mode capacitance (>10 $\mu$ F) as the detection signature. Note that PDs in this range of capacitance are defined as invalid, so a PSE that detects legacy PDs is technically noncompliant with the IEEE spec.

The LTC4266A/LTC4266C can be configured to detect this type of legacy PD. Legacy detection is disabled by default, but can be manually enabled on a per-port basis. When enabled, the port will report Detect Good when it sees either a valid IEEE PD or a high-capacitance legacy PD. With legacy mode disabled, only valid IEEE PDs will be recognized.

### CLASSIFICATION

#### 802.3af Classification

A PD can optionally present a classification signature to the PSE to indicate the maximum power it will draw while operating. The IEEE specification defines this signature as

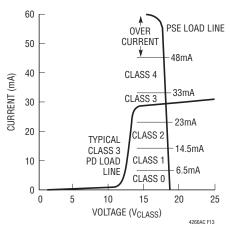

Figure 13. PD Classification

a constant current draw when the PSE port voltage is in the V<sub>CLASS</sub> range (between 15.5V and 20.5V), with the current level indicating one of 5 possible PD classes. Figure 13 shows a typical PD load line, starting with the slope of the 25k $\Omega$  signature resistor below 10V, then transitioning to the classification signature current (in this case, Class 3) in the V<sub>CLASS</sub> range. Table 5 shows the possible classification values.

| Table 5. | Classification | Values |

|----------|----------------|--------|

|----------|----------------|--------|

| CLASS   | RESULT                                         |  |

|---------|------------------------------------------------|--|

| Class 0 | No Class Signature Present; Treat Like Class 3 |  |

| Class 1 | 3W                                             |  |

| Class 2 | 7W                                             |  |

| Class 3 | 13W                                            |  |

| Class 4 | 25.5W (Type 2)                                 |  |

If classification is enabled, the port will classify the PD immediately after a successful detection cycle in semiauto or AUTO pin modes, or when commanded to in manual mode. It measures the PD classification signature by applying 18V for 12ms (both values typical) to the port via the OUTn pin and measuring the resulting current; it then reports the discovered class in the Port Status register. If the LTC4266A/LTC4266C is in AUTO pin mode, it will additionally use the classification result to set the I<sub>CUT</sub> and I<sub>LIM</sub> thresholds. See the Reset and the AUTO/MID Pin section for more information.

The classification circuitry is disabled when the port is initially powered up with the AUTO pin low, in shutdown

mode, or when the corresponding Class Enable bit is cleared.

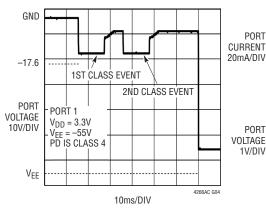

#### 802.3at 2-Event Classification

The 802.3at specification defines two methods of classifying a Type 2 PD. The LTC4266A supports 802.3at 2-event classification. The LTC4266C does not support 2-event classification.

One method adds extra fields to the Ethernet LLDP data protocol; although the LTC4266A/LTC4266C is compatible with this classification method, it cannot perform classification directly since it doesn't have access to the data path. LLDP classification requires the PSE to power the PD as a standard 802.3af (Type 1) device. It then waits for the host to perform LLDP communication with the PD and update the PSE port data. The LTC4266A/LTC4266C supports changing the  $I_{LIM}$  and  $I_{CUT}$  levels on the fly, allowing the host to complete LLDP classification.

The second 802.3at classification method, known as 2-event classification or ping-pong, is supported by the LTC4266A. A Type 2 PD that is requesting more than 13W will indicate Class 4 during normal 802.3af classification. If the LTC4266A sees Class 4, it forces the port to a specified lower voltage (called the mark voltage, typically 9V), pauses briefly, and then re-runs classification to verify the Class 4 reading (Figure 1). It also sets a bit in the High Power Status register to indicate that it ran the second classification cycle. The second cycle alerts the PD that it is connected to a Type 2 PSE which can supply Type 2 power levels.

2-event ping-pong classification is enabled by setting a bit in the port's High Power Mode register. Note that a pingpong enabled port only runs the second classification cycle when it detects a Class 4 device; if the first cycle returns Class 0 to 3, the port assumes it is connected to a Type 1 PD and does not run the second classification cycle.

#### **Invalid Type 2 Class Combinations**

The 802.3at specification defines a Type 2 PD class signature as two consecutive Class 4 results; a Class 4 followed by a Class 0-3 is not a valid signature. In AUTO pin mode, the LTC4266A will power a detected PD regardless of the classification results, with one exception: if the PD presents an invalid Type 2 signature (Class 4 followed by Class 0 to 3), the LTC4266A will not provide power and will restart the detection process. To aid in diagnosis, the Port Status register will always report the results of the last class pulse, so, for example, an invalid Class 4–Class 2 combination would report a second class pulse was run in the High Power Status register (which implies that the first cycle found Class 4), and Class 2 in the Port Status register.

### **POWER CONTROL**

#### **External MOSFET, Sense Resistor Summary**

The primary function of the LTC4266A/LTC4266C is to control the delivery of power to the PSE port. It does this by controlling the gate drive voltage of an external power MOSFET while monitoring the current via an external sense resistor and the output voltage at the OUT pin. This circuitry serves to couple the raw  $V_{EE}$  input supply to the port in a controlled manner that satisfies the PD's power needs while minimizing power dissipation in the MOSFET and disturbances on the  $V_{EE}$  backplane.

The LTC4266A/LTC4266C is designed to use  $0.25\Omega$  sense resistors to minimize power dissipation. It also supports  $0.5\Omega$  sense resistors, which are the default when LTC4258/LTC4259A compatibility is desired.

#### **Inrush Control**

Once the command has been given to turn on a port, the LTC4266A/LTC4266C ramps up the GATE pin of that port's external MOSFET in a controlled manner. Under normal power-up circumstances, the MOSFET gate will rise until the port current reaches the inrush current limit level (typically 450mA), at which point the GATE pin will be servoed to maintain the specified  $I_{INRUSH}$  current. During this inrush period, a timer ( $t_{START}$ ) runs. When output charging is complete, the port current will fall and the GATE pin will be allowed to continue rising to fully enhance the MOSFET and minimize its on-resistance. The final V<sub>GS</sub> is nominally 12V. The inrush period is maintained until the  $t_{START}$  timer expires. At this time if the inrush current limit level is still exceeded the port will be turned back off and a  $t_{START}$  fault reported.

#### **Current Limit**

Each LTC4266A/LTC4266C port includes two current limiting thresholds ( $I_{CUT}$  and  $I_{LIM}$ ), each with a corresponding timer ( $t_{CUT}$  and  $t_{LIM}$ ). Setting the  $I_{CUT}$  and  $I_{LIM}$  thresholds depends on several factors: the class of the PD, the voltage of the main supply ( $V_{EE}$ ), the type of PSE (Type 1 or Type 2), the sense resistor (0.5 $\Omega$  or 0.25 $\Omega$ ), the SOA of the MOSFET, and whether or not the system is required to implement class enforcement.

Per the IEEE specification, the LTC4266A/LTC4266C will allow the port current to exceed  $I_{CUT}$  for a limited period of time before removing power from the port, whereas it will actively control the MOSFET gate drive to keep the port current below  $I_{LIM}$ . The port does not take any action to limit the current when only the  $I_{CUT}$  threshold is exceeded, but does start the  $t_{CUT}$  timer. If the current drops below the  $I_{CUT}$  current threshold before its timer expires, the  $t_{CUT}$  timer counts back down, but at 1/16 the rate that it counts up. If the  $t_{CUT}$  timer reaches 60ms (typical) the port is turned off and the port  $t_{CUT}$  fault is set. This allows the current limit circuitry to tolerate intermittent overload signals with duty cycles below about 6%; longer duty cycle overloads will turn the port off.

The I<sub>LIM</sub> current limiting circuit is always enabled and actively limiting port current. The t<sub>LIM</sub> timer is enabled only when the programmable t<sub>LIMn</sub> field is non-zero. This allows t<sub>LIM</sub> to be set to a shorter value than t<sub>CUT</sub> to provide more aggressive MOSFET protection and turn off a port before MOSFET damage can occur. The t<sub>LIM</sub> timer starts when the I<sub>LIM</sub> threshold is exceeded. When the t<sub>LIMn</sub> field the port is turned off and the port t<sub>LIM</sub> fault is set. When the t<sub>LIMn</sub> field is zero, t<sub>LIM</sub> behaviors are tracked by the t<sub>CUT</sub> timer, which counts up during both I<sub>LIM</sub> and I<sub>CUT</sub> events.

$I_{CUT}$  is typically set to a lower value than  $I_{LIM}$  to allow the port to tolerate minor faults without current limiting.

Per the IEEE specification, the LTC4266A/LTC4266C will automatically set I<sub>LIM</sub> to 425mA (shown in bold in Table 6) during inrush at port turn-on, and then switch to the programmed I<sub>LIM</sub> setting once inrush has completed. To maintain IEEE compliance, I<sub>LIM</sub> should be kept at

425mA for all Type 1 PDs, and 850mA if a Type 2 PD is detected.  $\rm I_{LIM}$  is automatically reset to 425mA when a port turns off.

#### I<sub>LIM</sub> Foldback

The LTC4266A/LTC4266C features a two-stage foldback circuit that reduces the port current if the port voltage falls below the normal operating voltage. This keeps MOSFET power dissipation at safe levels for typical 802.3af MOSFETs, even at extended 802.3at power levels. Current limit and foldback behavior are programmable on a perport basis. Table 6 gives examples of recommended I<sub>LIM</sub> register settings.

#### Table 6. Example Current Limit Settings

|                       | INTERNAL REGISTER SETTING (hex) |                          |  |

|-----------------------|---------------------------------|--------------------------|--|

| I <sub>LIM</sub> (mA) | $R_{SENSE} = 0.5\Omega$         | $R_{SENSE} = 0.25\Omega$ |  |

| 53                    | 88                              |                          |  |

| 106                   | 08                              | 88                       |  |

| 159                   | 89                              |                          |  |

| 213                   | 80                              | 08                       |  |

| 266                   | 8A                              |                          |  |

| 319                   | 09                              | 89                       |  |

| 372                   | 8B                              |                          |  |

| 425                   | 00                              | 80                       |  |

| 478                   | 8E                              |                          |  |

| 531                   | 92                              | 8A                       |  |

| 584                   | СВ                              |                          |  |

| 638                   | 10                              | 90                       |  |

| 744                   | D2                              | 9A                       |  |

| 850                   | 40                              | CO                       |  |

| 956                   | 4A                              | CA                       |  |

| 1063                  | 50                              | DO                       |  |

| 1169                  | 5A                              | DA                       |  |

| 1275                  | 60                              | E0                       |  |

| 1488                  | 52                              | 49                       |  |

| 1700                  |                                 | 40                       |  |

| 1913                  |                                 | 4A                       |  |

| 2125                  |                                 | 50                       |  |

| 2338                  |                                 | 5A                       |  |

| 2550                  |                                 | 60                       |  |

| 2975                  |                                 | 52                       |  |

The LTC4266A/LTC4266C will support current levels well beyond the maximum values in the 802.3at specification. The shaded areas in Table 6 indicate settings that may require a larger external MOSFET, additional heat sinking, or enabling  $t_{LIM}$ .

### **MOSFET Fault Detection**

LTC4266A/LTC4266C PSE ports are designed to tolerate significant levels of abuse, but in extreme cases it is possible for the external MOSFET to be damaged. A failed MOSFET may short source to drain, which will make the port appear to be on when it should be off; this condition may also cause the sense resistor to fuse open, turning off the port but causing the LTC4266A/LTC4266C SENSE pin to rise to an abnormally high voltage. A failed MOSFET may also short from gate to drain, causing the LTC4266A/LTC4266C GATE pin to rise to an abnormally high voltage. The LTC4266A/LTC4266C OUT, SENSE and GATE pins are designed to tolerate up to 80V faults without damage.