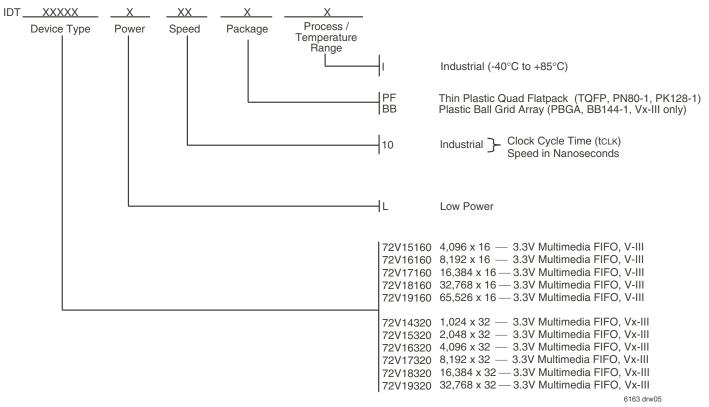

| 3.3V MULTIMED<br>16 BIT V-III, 32 B<br>UP TO 1 Mb DE                                                                                                                                                                                                                                                                                                                  | BIT Vx-III FAMILY                                                                                                                                                                                                                                                                                                  | IDT72V15160<br>IDT72V16160<br>IDT72V17160<br>IDT72V18160<br>IDT72V19160                                                                                                                                                                                                            | IDT72V14320<br>IDT72V15320<br>IDT72V16320<br>IDT72V17320<br>IDT72V18320<br>IDT72V19320 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| V-III         Vx-III           IDT72V15160 - 4,096 x 16         IDT72V14320 - 1,024 x 3           IDT72V15160 - 8,192 x 16         IDT72V15320 - 2,048 x 3           IDT72V17160 - 16,384 x 16         IDT72V16320 - 4,096 x 3           IDT72V18160 - 32,768 x 16         IDT72V17320 - 8,192 x 3           IDT72V19160 - 65,536 x 16         IDT72V18320 - 16,384 x | <ul> <li>Empty, Full and Half-Fu</li> <li>Programmable Almost-E</li> <li>default to one of eight  </li> <li>Program programmable</li> <li>Output enable puts data</li> <li>JTAG port, provided for</li> <li>Available in a 80-pin (V-</li> <li>Thin Quad Flat Pack (TC</li> <li>Array (PBGA) (with addi</li> </ul> | a, but retains programma<br>ill flags signal FIFO statu<br>Empty and Almost-Full fla<br>preselected offsets<br>e flags through serial input<br>a outputs into high imper<br>Boundary Scan function<br>-III) Thin Quad Flat Pack<br>QFP) or a 144-pin (Vx-III)<br>itional features) | us<br>ags, each flag can<br>ut<br>edance state<br>n (PBGA Only)<br>c, 128-pin(Vx-III)  |

| <ul> <li>Up to 100 MHz Operation of the Clocks</li> <li>5V input tolerant</li> <li>Auto power down minimizes standby power consumption</li> </ul>                                                                                                                                                                                                                     | <ul> <li>Industrial temperature r</li> <li>High-performance subn</li> </ul>                                                                                                                                                                                                                                        | • •                                                                                                                                                                                                                                                                                | y                                                                                      |

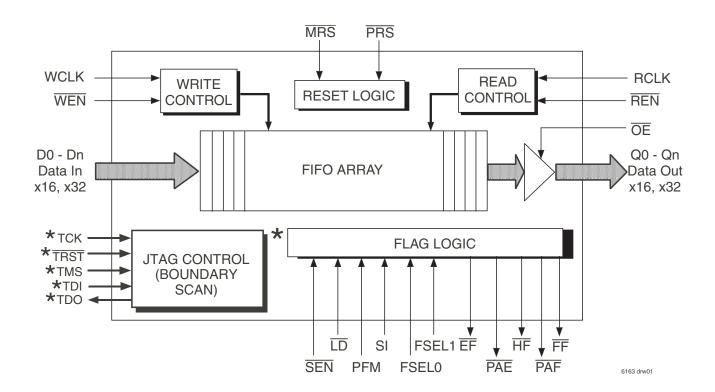

# **FUNCTIONAL BLOCK DIAGRAM**

\*Available on the Vx-III PBGA package only.

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

## INDUSTRIAL TEMPERATURE RANGE

## **DESCRIPTION:**

The IDT V-III and Vx-III Multimedia FIFOs are exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memories with independent clocked read and write controls and high density offerings up to 1 Mbit.

Each FIFO has a data input port (Dn) and a data output port (Qn). The frequencies of both the RCLK (read port clock) and the WCLK (write port clock) signals may vary from 0 to fs(MAX) with complete independence. There are no restrictions on the frequency of the one clock input with respect to the other.

These FIFOs have five flag pins,  $\overline{\text{EF}}$  (Empty Flag),  $\overline{\text{FF}}$  (Full Flag),  $\overline{\text{HF}}$  (Halffull Flag),  $\overline{\text{PAE}}$  (Programmable Almost-Empty flag) and  $\overline{\text{PAF}}$  (Programmable Almost-Full flag). PAE and PAF can be programmed independently to switch at any point in memory. Programmable offsets determine the flag switching threshold and can be loaded with the serial interface to any user desired value or by default values. Eight default offset settings are provided, so that PAE can be set to switch at a predefined number of locations from the empty boundary and the PAF threshold can also be set at similar predefined values from the full boundary. The default offset values are set during Master Reset by the state of the FSEL0, FSEL1, and LD pins.

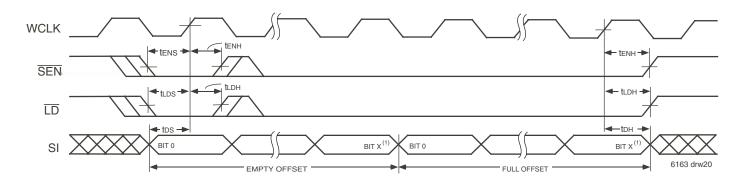

For serial programming,  $\overline{SEN}$  together with  $\overline{LD}$  on each rising edge of WCLK, are used to load the offset registers via the Serial Input (SI).

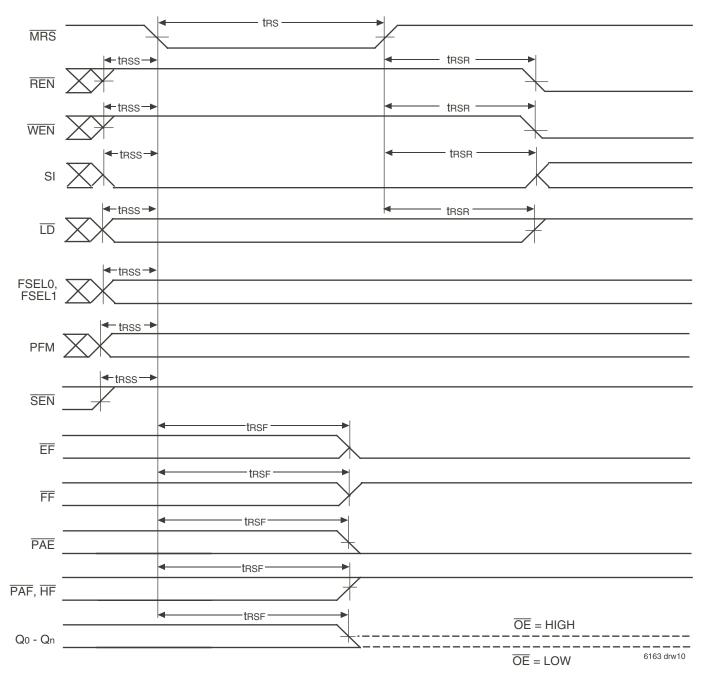

During Master Reset (MRS) the read and write pointers are set to the first location of the FIFO.

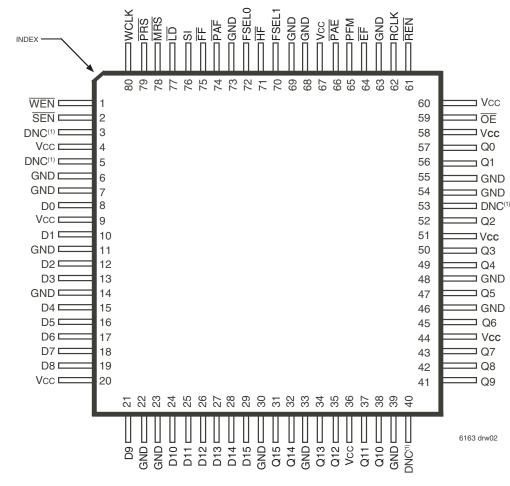

## PIN CONFIGURATIONS (16-BIT V-III FAMILY)

NOTE: 1. DNC = Do Not Connect.

TQFP (PN80-1, order code: PF) TOP VIEW

#### IDT72V15160/16160/17160/18160/19160 - 3.3V 16-BIT V-III MULTIMEDIA FIFO IDT72V14320/15320/16320/17320/18320/19320 - 3.3V 32-BIT VX-III MULTIMEDIA FIFO

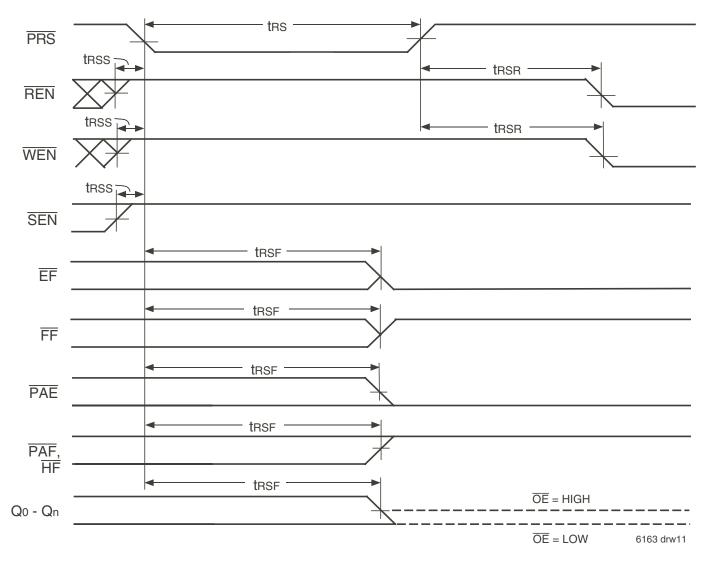

The Partial Reset (PRS) also sets the read and write pointers to the first location of the memory. However, the programmable flag settings existing before Partial Reset remain unchanged. PRS is useful for resetting a device in midoperation, when reprogramming programmable flags would be undesirable.

It is also possible to select the timing mode of the PAE (Programmable Almost-Empty flag) and PAF (Programmable Almost-Full flag) outputs. The timing modes can be set to be either asynchronous or synchronous for the PAE and PAF flags.

If asynchronous PAE/PAF configuration is selected, the PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-to-HIGH transition of WCLK. Similarly, the PAF is asserted LOW on the LOW-to-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK.

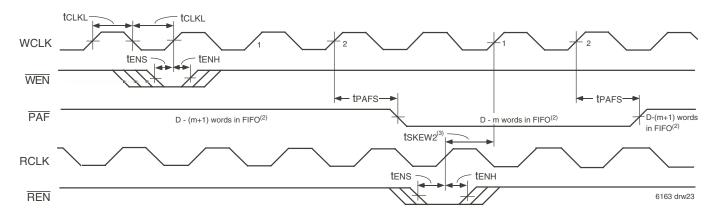

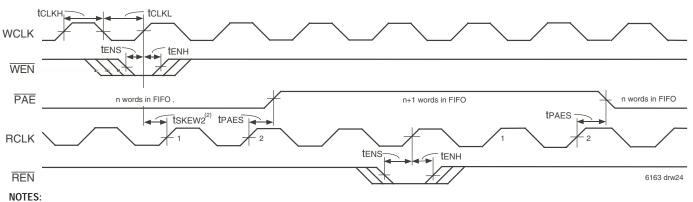

If synchronous PAE/PAF configuration is selected, the PAE is asserted and updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only and not RCLK. The mode desired is configured during Master Reset by the state of the Programmable Flag Mode (PFM) pin.

If, at any time, the FIFO is not actively performing an operation, the chip will automatically power down. Once in the power down state, the standby supply current consumption is minimized. Initiating any operation (by activating control inputs) will immediately take the device out of the power down state.

The IDT V-III and Vx-III family of FIFOs are fabricated using IDT's high speed submicron CMOS technology.

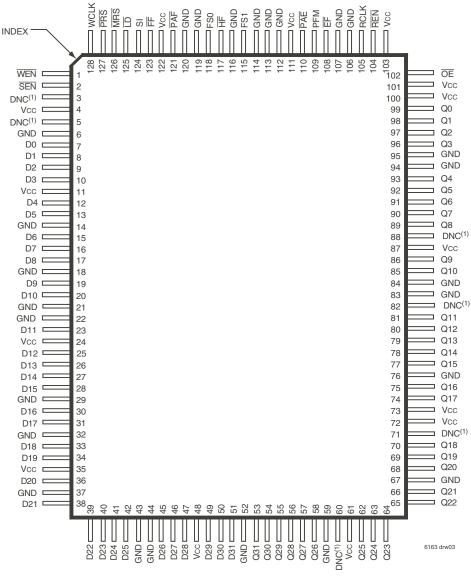

## **PIN CONFIGURATIONS (32-BIT Vx-III FAMILY)**

NOTE: 1. DNC - Do Not Connect.

> TQFP: (PK128-1, order code: PF) TOP VIEW

## **PIN CONFIGURATIONS-CONTINUED (32-BIT VX-III FAMILY)**

|   | ×                      | /— А     | 1 BALL F        | PAD CO         | RNER            |          |          |          |           |          |          |                          |

|---|------------------------|----------|-----------------|----------------|-----------------|----------|----------|----------|-----------|----------|----------|--------------------------|

| Α | O<br>Vcc               | O<br>WEN | O<br>wclk       | O<br>PAF       | O<br>FF         |          | O<br>GND |          | O<br>RCLK |          |          | 0<br>Q0                  |

| в | $\frac{O}{\text{SEN}}$ | O<br>GND | $\frac{O}{PRS}$ | $\frac{O}{LD}$ | $\frac{O}{MRS}$ | O<br>FS0 | O<br>FS1 | O<br>Vcc | O<br>GND  | O<br>PFM | O<br>Vcc | O<br>Q1                  |

| С | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | ()       | O                        |

|   | D0                     | D1       | D2              | si             | GND             | Vcc      | Vcc      | GND      | PAE       | GND      | Q3       | Q2                       |

| D | O                      | O        | O               | O              | O               | O        | O        | O        | O         | ()       | O        | O                        |

|   | D3                     | D4       | D5              | Vcc            | Vcc             | GND      | GND      | Vcc      | Vcc       | Q6       | Q5       | Q4                       |

| Е | O                      | O        | O               | O              | O               | O        | O        | O        | O         | ()       | 0        | 0                        |

|   | D6                     | D7       | D8              | Vcc            | GND             | GND      | GND      | GND      | Vcc       | Q9       | Q8       | Q7                       |

| F | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | O        | O                        |

|   | D9                     | D10      | D11             | Vcc            | GND             | GND      | GND      | GND      | Vcc       | Q12      | Q11      | Q10                      |

| G | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | O        | O                        |

|   | D14                    | D13      | D12             | Vcc            | GND             | GND      | GND      | GND      | Vcc       | Q13      | Q14      | Q15                      |

| н | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | O        | O                        |

|   | D17                    | D16      | D15             | Vcc            | GND             | GND      | GND      | GND      | Vcc       | Q16      | Q17      | Q18                      |

| J | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | O        | O                        |

|   | D20                    | D19      | D18             | Vcc            | Vcc             | GND      | GND      | Vcc      | Vcc       | Q19      | Q20      | Q21                      |

| к | O                      | O        | O               | O              | O               | O        | O        | O        | O         | O        | O        | O                        |

|   | D23                    | D22      | D21             | D28            | D31             | Vcc      | Vcc      | tdo      | Q29       | Q22      | Q23      | DNC                      |

| L | O                      | O        | O               | O              | O               | О        | О        | O        | O         | O        | O        | O                        |

|   | gnd                    | GND      | D25             | D27            | D30             | тмs      | тск      | Q31      | Q28       | Q26      | dnc      | dnc                      |

| М | O                      | O        | O               | O              | O               | O        | O        | O        | 0         | O        | O        | O                        |

|   | GND                    | GND      | D24             | D26            | D29             | TRST     | tdi      | Q30      | Q27       | Q25      | Q24      | DNC                      |

|   | 1                      | 2        | 3               | 4              | 5               | 6        | 7        | 8        | 9         | 10       | 11       | <b>12</b><br>6163 drw03b |

NOTE: 1. DNC - Do Not Connect.

> PBGA: 1mm pitch, 13mm x 13mm (BB144-1, order code: BB) TOP VIEW

## **PIN DESCRIPTION**

| Symbol               | Name                              | I/O | Description                                                                                                                                                                                                                                                                                                    |

|----------------------|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Do–Dn                | Data Inputs                       | Ι   | Data inputs for a 16 or 32-bit bus                                                                                                                                                                                                                                                                             |

| ĒF                   | Empty Flag                        | 0   | EF indicates the FIFO memory is empty. See Table 2.                                                                                                                                                                                                                                                            |

| FF                   | Full Flag                         | 0   | FF indicates the FIFO memory is full. See Table 2.                                                                                                                                                                                                                                                             |

| FSEL0 <sup>(1)</sup> | Flag Select Bit 0                 | Ι   | During Master Reset, this input along with FSEL1 and the $\overline{\text{LD}}$ pin, will select the default offset values for the programmable flags PAE and PAF. There are up to eight possible settings available.                                                                                          |

| FSEL1 <sup>(1)</sup> | Flag Select Bit 1                 | Ι   | During Master Reset, this input along with FSEL0 and the $\overline{\text{LD}}$ pin will select the default offset values for the programmable flags PAE and PAF. There are up to eight possible settings available.                                                                                           |

| ĦF                   | Half-Full Flag                    | 0   | $\overline{\text{HF}}$ indicates the FIFO memory is more than half-full. $\overline{\text{HF}}$ is asserted when the number of words written into the FIFO reaches N÷2+1, where N is the total depth of the FIFO. See Table 2.                                                                                 |

| LD                   | Load                              | I   | During Master Reset, the state of the LD input along with FSEL0 and FSEL1, determines one of eight default offset values for the PAE and PAF flags and serial programming mode. After Master Reset, LD must be high and should only toggle LOW together with SEN to start serial loading of the flag offsets.  |

| MRS                  | Master Reset                      | I   | MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Master Reset, the FIFO is configured for one of eight programmable flag default settings, serial programming of the offset settings and synchronous versus asynchronous programmable flag timing modes. |

| ŌĒ                   | Output Enable                     | Ι   | OE controls the output line drivers.                                                                                                                                                                                                                                                                           |

| PAE                  | Programmable<br>Almost-Empty Flag | 0   | PAE goes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the Empty Offset register. PAE goes HIGH if the number of words in the FIFO memory is greater than or equal to offset n.                                                                                      |

| PAF                  | Programmable<br>Almost-Full Flag  | 0   | PAF goes HIGH if the number of free locations in the FIFO memory is more than offset m, which is stored in the Full Offset register. PAF goes LOW if the number of free locations in the FIFO memory is less than or equal to m.                                                                               |

| PFM <sup>(1)</sup>   | Programmable<br>Flag Mode         | I   | During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on PFM will select Synchronous Programmable flag timing mode.                                                                                                                                                 |

| PRS                  | Partial Reset                     | I   | PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Partial Reset, the serial programming method or programmable flag settings are all retained.                                                                                                            |

| Q0–Qn                | Data Outputs                      | 0   | Data outputs for an 16 or 32-bit bus. Outputs are not 5V tolerant regardless of the state of $\overline{OE}$ .                                                                                                                                                                                                 |

| RCLK                 | Read Clock                        | Ι   | When enabled by $\overline{\text{REN}}$ , the rising edge of RCLK reads data from the FIFO memory.                                                                                                                                                                                                             |

| REN                  | Read Enable                       | Ι   | REN enables RCLK for reading data from the FIFO memory.                                                                                                                                                                                                                                                        |

| SEN                  | Serial Enable                     | Ι   | SEN enables serial loading of programmable flag offsets. SEN must be high during Master Reset and should only toggle LOW together with LD to start serial loading of the flag offsets.                                                                                                                         |

| SI                   | Serial In                         | Ι   | At Maser Reset this pin is LOW. After Master Reset, this pin functions as a serial input for loading offset registers.                                                                                                                                                                                         |

| WCLK                 | Write Clock                       | Ι   | Enabled by WEN, the rising edge of WCLK writes data into the FIFO.                                                                                                                                                                                                                                             |

| WEN                  | Write Enable                      | Ι   | WEN enables WCLK for writing data into the FIFO memory.                                                                                                                                                                                                                                                        |

| Vcc                  | +3.3V Supply                      | Ι   | These are Vcc supply inputs and must be connected to the 3.3V supply rail.                                                                                                                                                                                                                                     |

| GND                  | Ground                            | Ι   | Ground Pins.                                                                                                                                                                                                                                                                                                   |

NOTE:

1. Inputs should not change state after Master Reset.

\*\*Please continue to next page for more Pin descriptions for PBGA package.

# PIN DESCRIPTION (32-BIT VX-III PBGA PACKAGE ONLY)

| Symbol              | Name                     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK <sup>(1)</sup>  | JTAG Clock               | -   | Clock input for JTAG function. One of four terminals required by IEEE Standard 1149.1-1990. Test operations of the device are synchronous to TCK. Data from TMS and TDI are sampled on the rising edge of TCK and outputs change on the falling edge of TCK. If the JTAG function is not used this signal needs to be tied to GND.                                                                                                                                                                                                                                                                             |

| TDI <sup>(1)</sup>  | JTAG Test Data<br>Input  | Ι   | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded via the TDI on the rising edge of TCK to either the Instruction Register, ID Register and Bypass Register. An internal pull-up resistor forces TDI HIGH if left unconnected.                                                                                                                                                                                                                                                                                                   |

| TDO <sup>(1)</sup>  | JTAG Test Data<br>Output | 0   | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded output via the TDO on the falling edge of TCK from either the Instruction Register, ID Register and Bypass Register. This output is high impedance except when shifting, while in SHIFT-DR and SHIFT-IR controller states.                                                                                                                                                                                                                                                     |

| TMS <sup>(1)</sup>  | JTAG Mode Select         | I   | TMS is a serial input pin. One of four terminals required by IEEE Standard 1149.1-1990. TMS directs the device through its TAP controller states. An internal pull-up resistor forces TMS HIGH if left unconnected.                                                                                                                                                                                                                                                                                                                                                                                            |

| TRST <sup>(1)</sup> | JTAG Reset               | I   | TRST is an asynchronous reset pin for the JTAG controller. The JTAG TAP controller does not automatically reset upon power-up, thus it must be reset by either this signal or by setting TMS= HIGH for five TCK cycles. If the TAP controller is not properly reset then the FIFO outputs will always be in high-impedance. If the JTAG function is used but the user does not want to use TRST, then TRST can be tied with MRS to ensure proper FIFO operation. If the JTAG function is not used then this signal needs to be tied to GND. An internal pull-up resistor forces TRST HIGH if left unconnected. |

NOTE:

1. These pins are for the JTAG port. Please refer to pages 15-19 and Figures 2-4.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol               | Rating                                  | Industrial   | Unit |

|----------------------|-----------------------------------------|--------------|------|

| Vterm <sup>(2)</sup> | Terminal Voltage<br>with respect to GND | -0.5 to +4.5 | V    |

| Tstg                 | Storage<br>Temperature                  | –55 to +125  | °C   |

| Ιουτ                 | DC Output Current                       | -50 to +50   | mA   |

#### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Vcc terminal only.

## RECOMMENDED DC OPERATING CONDITIONS

| Symbol             | Parameter                        | Min. | Тур. | Мах. | Unit |

|--------------------|----------------------------------|------|------|------|------|

| VCC <sup>(1)</sup> | Supply Voltage Industrial        | 3.15 | 3.3  | 3.45 | V    |

| GND                | Supply Voltage Industrial        | 0    | 0    | 0    | V    |

| VIH <sup>(2)</sup> | Input High Voltage Industrial    | 2.0  |      | 5.5  | V    |

| VIL <sup>(3)</sup> | Input Low Voltage Industrial     | _    | _    | 0.8  | V    |

| Ta                 | Operating Temperature Industrial | -40  | _    | 85   | °C   |

NOTES:

1. VCC =  $3.3V \pm 0.15V$ , JEDEC JESD8-A compliant.

2. Outputs are not 5V tolerant.

3. 1.5V undershoots are allowed for 10ns once per cycle.

# **DC ELECTRICAL CHARACTERISTICS**

(Industrial: VCC =  $3.3V \pm 0.15V$ , TA =  $-40^{\circ}C$  to  $+85^{\circ}C$ ; JEDEC JESD8-A compliant)

|                         |                                       | IDT72V15160,<br>IDT72V16160,<br>IDT72V17160,<br>IDT72V18160,<br>IDT72V19160,<br>IDT72V19160,<br>Indust |      |      |

|-------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|------|------|

| Symbol                  | Parameter                             | Min.                                                                                                   | Max. | Unit |

| LI <sup>(1)</sup>       | Input Leakage Current                 | -1                                                                                                     | 1    | μA   |

| LO <sup>(2)</sup>       | Output Leakage Current                | -10                                                                                                    | 10   | μA   |

| Vон                     | Output Logic "1" Voltage, IOH = –2 mA | 2.4                                                                                                    | —    | V    |

| Vol                     | Output Logic "0" Voltage, IOL = 8 mA  | _                                                                                                      | 0.4  | V    |

| ICC1 <sup>(3,4,5)</sup> | Active Power Supply Current           | —                                                                                                      | 40   | mA   |

| CC2 <sup>(3,6)</sup>    | Standby Current                       | —                                                                                                      | 15   | mA   |

#### NOTES:

- 1. Measurements with 0.4  $\leq$  ViN  $\leq$  Vcc.

- 2.  $\overline{\text{OE}} \ge \text{ViH}$ ,  $0.4 \le \text{Vout} \le \text{Vcc}$ .

- 3. Tested with outputs open (IOUT = 0).

- 4. RCLK and WCLK toggle at 20 MHz and data inputs switch at 10 MHz.

- 5. Typical  $I_{CC1} = 4.2 + 1.4^{*}f_{S} + 0.02^{*}CL^{*}f_{S}$  (in mA) with  $V_{CC} = 3.3V$ ,  $t_{A} = 25^{\circ}C$ ,  $f_{S} = WCLK$  frequency = RCLK frequency (in MHz, using TTL levels), data switching at fs/2, CL = capacitive load (in pF).

- 6. All Inputs = Vcc 0.2V or GND + 0.2V, except RCLK and WCLK, which toggle at 20 MHz.

#### CAPACITANCE (TA = +25°C, f = 1.0MHz) Symbol Parameter<sup>(1)</sup> Conditions Max. Unit CIN<sup>(2)</sup> $V_{IN} = 0V$ 10 Input pF Capacitance COUT<sup>(1,2)</sup> Output $V_{OUT} = 0V$ 10 pF Capacitance

## NOTES:

1. With output deselected, ( $\overline{OE} \ge V_{IH}$ ).

2. Characterized values, not currently tested.

## **AC ELECTRICAL CHARACTERISTICS**

(Industrial: Vcc =  $3.3V \pm 0.15V$ , TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C; JEDEC JESD8-A compliant)

|               |                                                          | Indus                                                                                                    | strial                                                                                                                     |      |

|---------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|

|               |                                                          | IDT72V15160L10<br>IDT72V16160L10<br>IDT72V17160L10<br>IDT72V17160L10<br>IDT72V18160L10<br>IDT72V19160L10 | IDT72V14320L10<br>IDT72V15320L10<br>IDT72V16320L10<br>IDT72V17320L10<br>IDT72V18320L10<br>IDT72V18320L10<br>IDT72V19320L10 |      |

| Symbol        | Parameter                                                | Min.                                                                                                     | Max                                                                                                                        | Unit |

| fS            | Clock Cycle Frequency                                    | —                                                                                                        | 100                                                                                                                        | Mhz  |

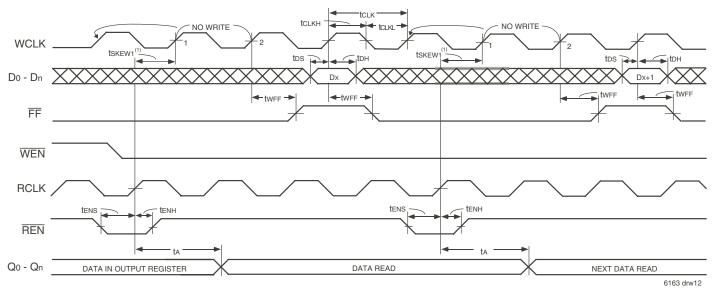

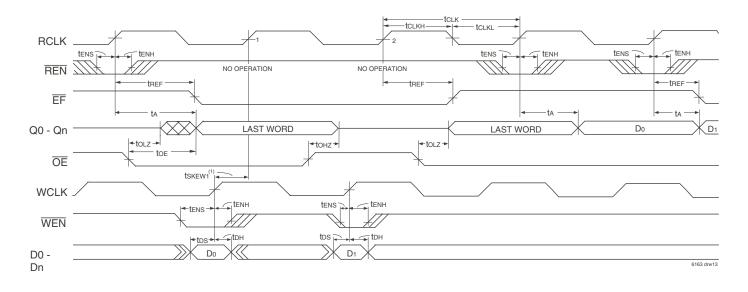

| tA            | Data Access Time                                         | 2                                                                                                        | 6.5                                                                                                                        | ns   |

| <b>t</b> CLK  | Clock Cycle Time                                         | 10                                                                                                       | —                                                                                                                          | ns   |

| <b>t</b> CLKH | Clock High Time                                          | 4.5                                                                                                      | —                                                                                                                          | ns   |

| <b>t</b> CLKL | Clock Low Time                                           | 4.5                                                                                                      | —                                                                                                                          | ns   |

| tDS           | Data Setup Time                                          | 3.5                                                                                                      | —                                                                                                                          | ns   |

| ťDH           | Data Hold Time                                           | 0.5                                                                                                      | _                                                                                                                          | ns   |

| tens          | Enable Setup Time                                        | 3.5                                                                                                      | —                                                                                                                          | ns   |

| <b>t</b> ENH  | Enable Hold Time                                         | 0.5                                                                                                      | _                                                                                                                          | ns   |

| tlds          | Load Setup Time                                          | 3.5                                                                                                      | _                                                                                                                          | ns   |

| tldh          | Load Hold Time                                           | 0.5                                                                                                      | _                                                                                                                          | ns   |

| tRS           | Reset Pulse Width <sup>(1)</sup>                         | 10                                                                                                       | —                                                                                                                          | ns   |

| tRSS          | Reset Setup Time                                         | 15                                                                                                       | —                                                                                                                          | ns   |

| tRSR          | Reset Recovery Time                                      | 10                                                                                                       | _                                                                                                                          | ns   |

| tRSF          | Reset to Flag and Output Time                            | —                                                                                                        | 15                                                                                                                         | ns   |

| tolz          | Output Enable to Output in Low Z <sup>(2)</sup>          | 0                                                                                                        | —                                                                                                                          | ns   |

| toe           | Output Enable to Output Valid                            | 2                                                                                                        | 6                                                                                                                          | ns   |

| tohz          | Output Enable to Output in High-Z <sup>(2)</sup>         | 2                                                                                                        | 6                                                                                                                          | ns   |

| twFF          | Write Clock to FF                                        | _                                                                                                        | 6.5                                                                                                                        | ns   |

| tref          | Read Clock to EF                                         | _                                                                                                        | 6.5                                                                                                                        | ns   |

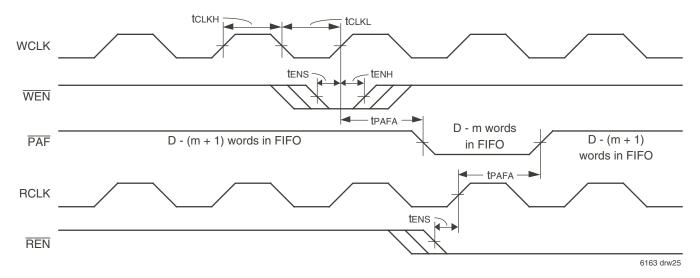

| <b>t</b> PAFA | Clock to Asynchronous Programmable Almost-Full Flag      | —                                                                                                        | 16                                                                                                                         | ns   |

| <b>t</b> PAFS | Write Clock to Synchronous Programmable Almost-Full Flag | _                                                                                                        | 6.5                                                                                                                        | ns   |

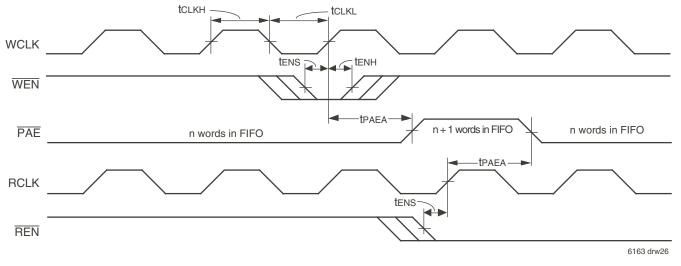

| <b>t</b> PAEA | Clock to Asynchronous Programmable Almost-Empty Flag     | _                                                                                                        | 16                                                                                                                         | ns   |

| <b>t</b> PAES | Read Clock to Synchronous Programmable Almost-Empty Flag |                                                                                                          | 6.5                                                                                                                        | ns   |

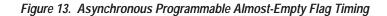

| tHF           | Clock to HF                                              | _                                                                                                        | 16                                                                                                                         | ns   |

| tskew1        | Skew time between RCLK and WCLK for EF and FF            | 7                                                                                                        | _                                                                                                                          | ns   |

| tskew2        | Skew time between RCLK and WCLK for PAE and PAF          | 10                                                                                                       | _                                                                                                                          | ns   |

NOTES:

1. Pulse widths less than minimum values are not allowed.

2. Values guaranteed by design, not currently tested.

#### - 3.3V 16-BIT V-III MULTIMEDIA FIFO IDT72V15160/16160/17160/18160/19160 IDT72V14320/15320/16320/17320/18320/19320 - 3.3V 32-BIT VX-III MULTIMEDIA FIFO

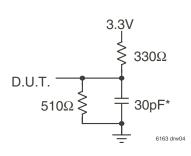

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V        |

|-------------------------------|--------------------|

| Input Rise/Fall Times         | 3ns <sup>(1)</sup> |

| Input Timing Reference Levels | 1.5V               |

| Output Reference Levels       | 1.5V               |

| Output Load for tCLK = 10ns   | See Figure 1       |

## **AC TEST LOADS**

INDUSTRIAL

**TEMPERATURE RANGE**

Figure 1. Output Load \* Includes jig and scope capacitances.

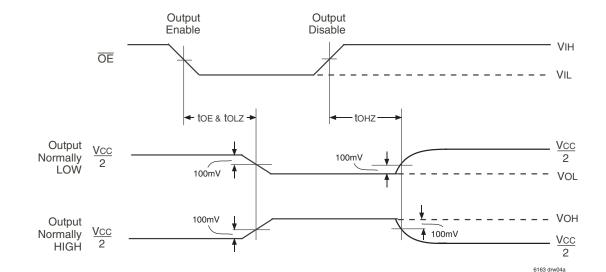

# **OUTPUT ENABLE & DISABLE TIMING**

NOTE: 1. REN is HIGH.

## **FUNCTIONAL DESCRIPTION**

To write data into to the FIFO, Write Enable (WEN) must be LOW. Data presented to the DATA IN lines will be clocked into the FIFO on subsequent transitions of the Write Clock (WCLK). After the first write is performed, the Empty Flag (EF) will go HIGH. Subsequent writes will continue to fill up the FIFO. The Programmable Almost-Empty flag (PAE) will go HIGH after n + 1 words have been loaded into the FIFO, where "n" is the empty offset value. The default setting for these values are stated in the footnote of Table 1. This parameter is also user programmable.

If one continued to write data into the FIFO, and we assumed no read operations were taking place, the Half-Full flag ( $\overline{HF}$ ) would toggle to LOW once D/2+1 (D= total number of words) was written into the FIFO. Continuing to write data into the FIFO will cause the Programmable Almost-Full flag (PAF) to go LOW. Again, if no reads are performed, the PAF will go LOW after (D-m). The offset "m" is the full offset value. The default setting for these values are stated in the footnote of Table 1. This parameter is also user programmable.

When the FIFO is full, the Full Flag (FF) will go LOW, inhibiting further write operations. If no reads are performed after a reset, FF will go LOW after D writes to the FIFO.

If the FIFO is full, the first read operation will cause  $\overline{FF}$  to go HIGH. Subsequent read operations will cause  $\overline{PAF}$  and  $\overline{HF}$  to go HIGH. If further read operations occur, without write operations,  $\overline{PAE}$  will go LOW when there are n words in the FIFO, where n is the empty offset value. Continuing read operations will cause the FIFO to become empty. When the last word has been read from the FIFO, the  $\overline{EF}$  will go LOW inhibiting further read operations.  $\overline{REN}$  is ignored when the FIFO is empty.

The EF and FF outputs are double register-buffered outputs.

#### **PROGRAMMING FLAG OFFSETS**

Full and Empty Flag offset values are user programmable. The IDT V-III and Vx-III FIFOs have internal registers for these offsets.

There are two ways to program the flag offset values. Selecting one of the eight pre-set values during master reset or serial programming.

#### DEFAULT FLAG OFFSETS

There are eight default offset values selectable during Master Reset. These offset values are shown in Table 1.

**Programming offsets with default values (** $\overline{LD}$ ,  $\overline{SEN}$  pins): With the  $\overline{LD}$  pin together with the FSEL0 and FSEL1 the user has the option to choose one of eight preset values for both offset registers. During master reset the  $\overline{LD}$  pin can be either HIGH or LOW depending on the selected value. After Master Reset,  $\overline{LD}$  must be high and should not change state. SEN should be high during and after Master Reset and should not change state.

#### SERIAL PROGRAMMING MODE

Offset values can also be programmed into the FIFO by serial loading method. The offset registers may be programmed (and reprogrammed) any time after Master Reset. Valid programming ranges are from 0 to D-1.

Serial programming of offset values (LD, SEN pins): In order to select serial programming the LD pin has to be HIGH during master. Both, LD and SEN pin have to toggle to LOW in order to initial the serial programming. LD should be high during normal FIFO operation.

If Serial Programming mode has been selected then programming of PAE and PAF values can be achieved by using a combination of the LD, SEN, WCLK and SI input pins. Programming PAE and PAF proceeds as follows: when LD and SEN are set LOW, data on the SI input are written, one bit for each WCLK rising edge, starting with the Empty Offset LSB and ending with the Full Offset MSB.

# TABLE 1 — DEFAULT PROGRAMMABLEFLAG OFFSETS

|    | IDT72V14320                       | <u>, 72V15360</u> |              |

|----|-----------------------------------|-------------------|--------------|

| ĪD | FSEL1                             | FSEL0             | Offsets n,m  |

| L  | Н                                 | L                 | 511          |

| L  | L                                 | Н                 | 255          |

| L  | L                                 | L                 | 127          |

| L  | Н                                 | Н                 | 63           |

| Н  | L                                 | L                 | 31           |

| Н  | Н                                 | L                 | 15           |

| Н  | L                                 | Н                 | 7            |

| Н  | Н                                 | Н                 | 3            |

|    | V16320, 72V173<br>/15160, 72V1610 |                   |              |

| LD | FSEL1                             | FSELO             | Offsets n,m  |

| Н  | L                                 | L                 | 1,023        |

| L  | Н                                 | L                 | 511          |

| L  | L                                 | Н                 | 255          |

| L  | L                                 | L                 | 127          |

| L  | Н                                 | Н                 | 63           |

| Н  | Н                                 | L                 | 31           |

| Н  | L                                 | Н                 | 15           |

| Н  | Н                                 | Н                 | 7            |

|    | IDT72                             | V19160            | -            |

| ĪD | FSEL1                             | FSEL0             | Offsets n,m  |

| Н  | L                                 | L                 | 1,023        |

| L  | Н                                 | L                 | 8,191        |

| L  | L                                 | Н                 | 16,383       |

| L  | L                                 | L                 | 127          |

| L  | Н                                 | Н                 | 4,095        |

| Н  | Н                                 | L                 | 511          |

| Н  | L                                 | Н                 | 2,047        |

| Н  | Н                                 | Н                 | 255          |

|    | All I                             | Devices           |              |

| LD | FSEL1                             | FSEL0             | Program Mode |

|    |                                   |                   |              |

NOTES:

1. n = empty offset for  $\overline{PAE}$ .

2. m = full offset for  $\overline{PAF}$ .

3. As well as selecting serial programming mode, one of the default values will also be loaded depending on the state of FSEL0 & FSEL1.

A total of

20 bits for the IDT72V14320 22 bits for the IDT72V15320 24 bits for the IDT72V15160, IDT72V16320 26 bits for the IDT72V16160, IDT72V17320 28 bits for the IDT72V17160, IDT72V18320 30 bits for the IDT72V18160, IDT72V19320 32 bits for the IDT72V19160 has to be loaded serial for the two (PAF, PAE) registers.

10

## TABLE 2 — STATUS FLAGS FOR IDT STANDARD MODE

|           |                       |                        | IDT72V15160            |    |     |    |     |    |

|-----------|-----------------------|------------------------|------------------------|----|-----|----|-----|----|

|           | IDT72V14320           | IDT72V15320            | IDT72V16320            | FF | PAF | HF | PAE | ĒĒ |

|           | 0                     | 0                      | 0                      | н  | н   | н  | L   | L  |

| Number of | 1 to n <sup>(1)</sup> | 1 to n <sup>(1)</sup>  | 1 to n <sup>(1)</sup>  | Н  | Н   | Н  | L   | Н  |

| Words in  | (n+1) to 512          | (n+1) to 1,024         | (n+1) to 2,048         | Н  | Н   | Н  | Н   | Н  |

| FIFO      | 513 to (1,024-(m+1))  | 1,025 to (2,048-(m+1)) | 2,049 to (4,096-(m+1)) | Н  | Н   | L  | Н   | Н  |

|           | (1,024-m) to 1,023    | (2,048-m) to 2,047     | (4,096m) to 4,095      | Н  | L   | L  | Н   | Н  |

|           | 1,024                 | 2,048                  | 4,096                  | L  | L   | L  | Н   | Н  |

|           | IDT72V16160            | IDT72V17160             | IDT72V18160              | IDT72V19160              |    |     |    |     |    |

|-----------|------------------------|-------------------------|--------------------------|--------------------------|----|-----|----|-----|----|

|           | IDT72V17320            | IDT72V18320             | IDT72V19320              |                          | FF | PAF | HF | PAE | ĒF |

|           | 0                      | 0                       | 0                        | 0                        | Н  | Н   | Н  | L   | L  |

| Number of | 1 to n <sup>(1)</sup>  | 1 to n <sup>(1)</sup>   | 1 to n <sup>(1)</sup>    | 1 to n <sup>(1)</sup>    | Н  | Н   | Н  | L   | Н  |

| Words in  | (n+1) to 4,096         | (n+1) to 8,192          | (n+1) to 16,384          | (n+1) to 32,768          | Н  | Н   | Н  | Н   | Н  |

| FIFO      | 4,097 to (8,192-(m+1)) | 8,193 to (16,384-(m+1)) | 16,385 to (32,768-(m+1)) | 32,769 to (65,536-(m+1)) | Н  | Н   | L  | Н   | Н  |

|           | (8,192-m) to 8,191     | (16,384-m) to 16,383    | (32,768-m) to 32,767     | (65,536-m) to 65,535     | Н  | L   | L  | Н   | Н  |

|           | 8,192                  | 16,384                  | 32,768                   | 65,536                   | L  | L   | L  | Н   | Н  |

NOTE:

1. See Table 1 for values for n, m.

6163 drw05

| LD | WEN | REN | SEN | WCLK | RCLK | Operation                                                                                                                       |  |

|----|-----|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 0  | 1   | 1   | 0   |      | Х    | Serial Flag Programming<br>1 bit for each rising WCLK edge<br>Starting with Empty Offset (LSB)<br>Ending with Full Offset (MSB) |  |

| 1  | 0   | Х   | Х   |      | Х    | Write Memory                                                                                                                    |  |

| 1  | Х   | 0   | Х   | Х    |      | Read Memory                                                                                                                     |  |

| X  | 1   | 1   | 1   | Х    | Х    | No Operation                                                                                                                    |  |

| 1  | 1   | 1   | Х   | Х    | Х    | No Operation                                                                                                                    |  |

| 0  | 0   | 1   | 1   |      | Х    | Invalid Operation                                                                                                               |  |

| 0  | 1   | 0   | 1   | Х    |      | Invalid Operation                                                                                                               |  |

# TABLE 3 — FLAG OFFSET PROGRAMMING, STATE OF $\overline{LD}$ ANDSEN AFTER MASTER RESET

6163 drw06

Using the serial method, individual registers cannot be programmed selectively.  $\overrightarrow{PAE}$  and  $\overrightarrow{PAF}$  can show a valid status only after the complete set of bits (for all offset registers) has been entered. The registers can be reprogrammed as long as the complete set of new offset bits is entered. When  $\overrightarrow{LD}$  is LOW and  $\overrightarrow{SEN}$  is HIGH, no serial write to the registers can occur.

Write operations to the FIFO are allowed before and during the serial programming sequence. In this case, the programming of all offset bits does not have to occur at once. A select number of bits can be written to the SI input and then, by bringing  $\overline{LD}$  and  $\overline{SEN}$  HIGH, data can be written to FIFO memory via Dn by toggling WEN. When WEN is brought HIGH with  $\overline{LD}$  and  $\overline{SEN}$  restored to a LOW, the next offset bit in sequence is written to the registers via SI. If an interruption of serial programming is desired, it is sufficient either to set  $\overline{LD}$  LOW and deactivate  $\overline{SEN}$  or to set  $\overline{SEN}$  LOW and deactivate  $\overline{LD}$ . Once  $\overline{LD}$  and  $\overline{SEN}$  are both restored to a LOW level, serial offset programming continues.

From the time serial programming has begun, neither programmable flag will be valid until the full set of bits required to fill all the offset registers has been written. Measuring from the rising WCLK edge that achieves the above criteria; PAF will be valid after two more rising WCLK edges plus tPAF, PAE will be valid after the next two rising RCLK edges plus tPAE plus tsKEW2.

Refer also to LD Signal description for more information on flag offset programming and state requirements for LD and SEN pins

# SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The IDT V-III and Vx-III can be configured during the Master Reset cycle with either synchronous or asynchronous timing for  $\overrightarrow{PAF}$  and  $\overrightarrow{PAE}$  flags by use of the PFM pin.

If synchronous PAF/PAE configuration is selected (PFM, HIGH during MRS), the PAF is asserted and updated on the rising edge of WCLK only and not RCLK. Similarly, PAE is asserted and updated on the rising edge of RCLK only and not WCLK.

If asynchronous PAF/PAE configuration is selected (PFM, LOW during MRS), the PAF is asserted LOW on the LOW-to-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK. Similarly, PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-to-HIGH transition of WCLK.

# SIGNAL DESCRIPTION

## **INPUTS:**

DATA IN (Do - Dn) Data inputs for 16 or 32-bit wide data.

# **CONTROLS:**

#### MASTER RESET (MRS)

A Master Reset is accomplished whenever the MRS input is taken to a LOW state. This operation sets the internal read and write pointers to the first location of the RAM array. PAE will go LOW, PAF will go HIGH, HF will go HIGH, EF will go LOW and FF will go HIGH.

SI is supposed to be LOW during master reset.

PFM control settings are defined during the Master Reset cycle.

During a Master Reset, the output register is initialized to all zeroes. A Master Reset is required after power up, before a write operation can take place. MRS is asynchronous.

#### PARTIAL RESET (PRS)

A Partial Reset is accomplished whenever the  $\overline{PRS}$  input is taken to a LOW state. As in the case of the Master Reset, the internal read and write pointers are set to the first location of the RAM array,  $\overline{PAE}$  goes LOW,  $\overline{PAF}$  goes HIGH,  $\overline{HF}$  goes HIGH,  $\overline{FF}$  will go HIGH and  $\overline{EF}$  will go LOW. The output register is initialized to all zeroes.  $\overline{PRS}$  is asynchronous.

A Partial Reset is useful for resetting the device during the course of operation, when reprogramming programmable flag offset settings may not be convenient.

#### SERIAL IN (SI)

At the time of Master Reset, SI must be LOW.

After Master Reset, SI acts as a serial input for loading  $\overline{PAE}$  and  $\overline{PAF}$  offsets into the programmable registers.

#### WRITE CLOCK (WCLK)

A write cycle is initiated on the rising edge of the WCLK input. Data setup and hold times must be met with respect to the LOW-to-HIGH transition of the WCLK. It is permissible to stop the WCLK. Note that while WCLK is idle, the  $\overline{FF}$ ,  $\overline{PAF}$  and  $\overline{HF}$  flags will not be updated. (Note that WCLK is only capable of updating  $\overline{HF}$  flag to LOW). The Write and Read Clocks can either be independent or coincident.

## WRITE ENABLE (WEN)

When the WEN input is LOW, data may be loaded into the FIFO array on the rising edge of every WCLK cycle if the device is not full. Data is stored in the FIFO array sequentially and independently of any ongoing read operation.

When WEN is HIGH, no new data is written in the FIFO array on each WCLK cycle.

To prevent data overflow,  $\overline{FF}$  will go LOW, inhibiting further write operations. Upon the completion of a valid read cycle,  $\overline{FF}$  will go HIGH allowing a write to occur. The  $\overline{FF}$  is updated by two WCLK cycles + tskEw after the RCLK cycle.

WEN is ignored when the FIFO is full.

## **READ CLOCK (RCLK)**

A read cycle is initiated on the rising edge of the RCLK input. Data can be read on the outputs, on the rising edge of the RCLK input. It is permissible to stop the RCLK. Note that while RCLK is idle, the  $\overline{\text{EF}}$ ,  $\overline{\text{PAE}}$  and  $\overline{\text{HF}}$  flags will not be updated. (Note that RCLK is only capable of updating the  $\overline{\text{HF}}$  flag to HIGH). The Write and Read Clocks can be independent or coincident.

The OE input is used to provide Asynchronous control of the three-state Qn outputs.

## READ ENABLE (REN)

When Read Enable is LOW, data is loaded from the FIFO array into the output register on the rising edge of every RCLK cycle if the device is not empty.

When the REN input is HIGH, the output register holds the previous data and no new data is loaded into the output register. The data outputs Qo-Qn maintain the previous data value.

Every word accessed at Qn, including the first word written to an empty FIFO, must be requested using  $\overline{REN}$ . When the last word has been read from the FIFO, the Empty Flag ( $\overline{EF}$ ) will go LOW, inhibiting further read operations.  $\overline{REN}$  is ignored when the FIFO is empty. Once a write is performed,  $\overline{EF}$  will go HIGH allowing a read to occur. The  $\overline{EF}$  flag is updated by two RCLK cycles + tskew after the valid WCLK cycle.

## SERIAL ENABLE ( SEN )

The  $\overline{\text{SEN}}$  input is an enable used only for serial programming of the offset registers. The serial programming method must be selected during Master Reset.  $\overline{\text{SEN}}$  is always used in conjunction with  $\overline{\text{LD}}$ . When these lines are both LOW, data at the SI input can be loaded into the program register one bit for each LOW-to-HIGH transition of WCLK.

When SEN is HIGH, the programmable registers retains the previous settings and no offsets are loaded. SEN functions the same way in both IDT.

Refer to LOAD (LD) pin and section "Programming Flag Offsets" for more information on offset programming.

## OUTPUT ENABLE ( OE)

When Output Enable is enabled (LOW), the parallel output buffers receive data from the output register. When  $\overline{OE}$  is HIGH, the output data bus (Qn) goes into a high impedance state.

## $LOAD(\overline{LD})$

This is a dual purpose pin. During Master Reset, the state of the  $\overline{\text{LD}}$  input, along with FSEL0 and FSEL1, determines one of eight default offset values for the PAE and PAF flags, along with the serial programming option for these offset registers (see Table 3).

After Master Reset, the  $\overline{\text{LD}}$  pin is used in conjunction with the  $\overline{\text{SEN}}$  pin to activate the programming process of the flag offset values  $\overline{\text{PAE}}$  and  $\overline{\text{PAF}}$ . Pulling  $\overline{\text{LD}}$  LOW will begin a serial loading of these offset values.

Depending on the default or serial programming option the state of  $\overline{\text{LD}}$  and  $\overline{\text{SEN}}$  have to be considered before and after master reset. Refer also to section "Programming Flag Offsets" for more information on offset programming.

**Programming offsets with default values:** With the  $\overline{LD}$  pin together with the FSEL0 and FSEL1 the user has the option to choose one of eight preset values for both offset registers. During master reset the  $\overline{LD}$  pin can be either HIGH or LOW depending on the selected value. After Master Reset,  $\overline{LD}$  must be high and should not change state. SEN should be high during and after Master Reset and should not change state.

Serial programming of offset values: In order to select serial programming the  $\overline{LD}$  pin has to be HIGH during master. Both,  $\overline{LD}$  and  $\overline{SEN}$  pin have to toggle to LOW in order to initial the serial programming.  $\overline{LD}$  should be high during normal FIFO operation.

#### PROGRAMMABLE FLAG MODE (PFM)

During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on PFM will select Synchronous Programmable flag timing mode. If asynchronous PAF/PAE configuration is selected (PFM, LOW during MRS), the PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-to-HIGH transition of WCLK. Similarly, the PAF is asserted LOW on the LOW-to-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK.

If synchronous PAE/PAF configuration is selected (PFM, HIGH during MRS), the PAE is asserted and updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only and not RCLK. The mode desired is configured during master reset by the state of the Programmable Flag Mode (PFM) pin.

## **OUTPUTS:**

#### FULL FLAG (FF)

When the FIFO is full,  $\overline{FF}$  will go LOW, inhibiting further write operations. When  $\overline{FF}$  is HIGH, the FIFO is not full. If no reads are performed after a reset (either MRS or PRS),  $\overline{FF}$  will go LOW after D writes to the FIFO (D = total number of words).

FF is synchronous and updated on the rising edge of WCLK. FF is a double register-buffered output.

#### EMPTY FLAG ( EF )

When the FIFO is empty,  $\overline{EF}$  will go LOW, inhibiting further read operations. When  $\overline{EF}$  is HIGH, the FIFO is not empty.

$\overline{\text{EF}}$  is synchronous and updated on the rising edge of RCLK.  $\overline{\text{EF}}$  is a double register-buffered output.

#### PROGRAMMABLE ALMOST-FULL FLAG (PAF)

The Programmable Almost-Full flag ( $\overline{PAF}$ ) will go LOW when the FIFO reaches the almost-full condition. If no reads are performed after reset ( $\overline{MRS}$ ),  $\overline{PAF}$  will go LOW after (D - m) words are written to the FIFO. (D=total number

of words, m = full offset value). The default setting for this value is stated in the footnote of Table 1.

If asynchronous PAF configuration is selected, the PAF is asserted LOW on the LOW-to-HIGH transition of the Write Clock (WCLK). PAF is reset to HIGH on the LOW-to-HIGH transition of the Read Clock (RCLK). If synchronous PAF configuration is selected, the PAF is updated on the rising edge of WCLK.

#### PROGRAMMABLE ALMOST-EMPTY FLAG (PAE)

The Programmable Almost-Emptyflag ( $\overrightarrow{PAE}$ ) will go LOW when the FIFO reaches the almost-empty condition.  $\overrightarrow{PAE}$  will go LOW when there are n words or less in the FIFO. The offset "n" is the empty offset value. The default setting for this value is stated in the footnote of Table 1.

If asynchronous PAE configuration is selected, the PAE is asserted LOW on the LOW-to-HIGH transition of the Read Clock (RCLK). PAE is reset to HIGH on the LOW-to-HIGH transition of the Write Clock (WCLK). If synchronous PAE configuration is selected, the PAE is updated on the rising edge of RCLK.

## HALF-FULL FLAG (HF)

This output indicates a half-full FIFO. The rising WCLK edge that fills the FIFO beyond half-full sets  $\overline{\text{HF}}$  LOW. The flag remains LOW until the difference between the write and read pointers becomes less than or equal to half of the total depth of the device; the rising RCLK edge that accomplishes this condition sets  $\overline{\text{HF}}$  HIGH.

If no reads are performed after reset ( $\overline{MRS}$  or  $\overline{PRS}$ ),  $\overline{HF}$  will go LOW after (D/2 + 1) writes to the FIFO, where D = total number of words available in the FIFO.

Because  $\overline{\text{HF}}$  is updated by both RCLK and WCLK, it is considered asynchronous.

## DATA OUTPUTS (Q0-Qn)

(Qo-Qn) are data outputs for 16-bit or 32-bit wide data.

#### IDT72V15160/16160/17160/18160/19160 - 3.3V 16-BIT V-III MULTIMEDIA FIFO IDT72V14320/15320/16320/17320/18320/19320 - 3.3V 32-BIT VX-III MULTIMEDIA FIFO

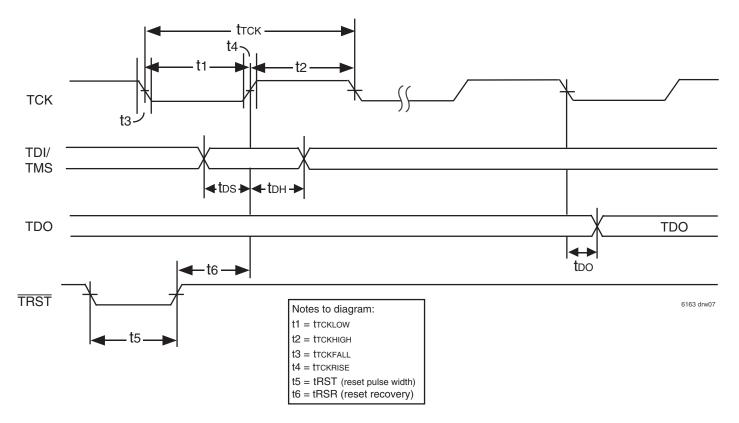

Figure 2. Standard JTAG Timing

## SYSTEM INTERFACE PARAMETERS

|                  |                    |                 | IDT72V14320<br>IDT72V15320<br>IDT72V16320<br>IDT72V17320<br>IDT72V18320<br>IDT72V18320<br>IDT72V19320 |      | 20<br>20<br>20<br>20<br>20 |

|------------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------|------|----------------------------|

| Parameter        | Symbol             | Test Conditions | Min.                                                                                                  | Max. | Units                      |

| Data Output      | tDO <sup>(1)</sup> |                 | -                                                                                                     | 20   | ns                         |

| Data Output Hold | tdoh(1)            |                 | 0                                                                                                     | -    | ns                         |

| Data Input       | tDS                | trise=3ns       | 10                                                                                                    | -    | ns                         |

|                  | tDH .              | tfall=3ns       | 10                                                                                                    | -    |                            |

NOTE:

1. 50pf loading on external output signals.

## JTAG AC ELECTRICAL CHARACTERISTICS

$(Vcc = 3.3V \pm 5\%; Tcase = 0^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter               | Symbol         | Test<br>Conditions |      |                  |       |

|-------------------------|----------------|--------------------|------|------------------|-------|

|                         |                | Conditions         | Min. | Max.             | Units |

| JTAG Clock Input Period | tтск           | -                  | 100  | -                | ns    |

| JTAG Clock HIGH         | tтскніgh       | -                  | 40   | -                | ns    |

| JTAG Clock Low          | <b>TCKLOW</b>  | -                  | 40   | -                | ns    |

| JTAG Clock Rise Time    | <b>TCKRISE</b> | -                  | -    | 5(1)             | ns    |

| JTAG Clock Fall Time    | <b>TCKFALL</b> | -                  | -    | 5 <sup>(1)</sup> | ns    |

| JTAG Reset              | trst           | -                  | 50   | -                | ns    |

| JTAG Reset Recovery     | trsr           | -                  | 50   | -                | ns    |

NOTE:

1. Guaranteed by design.

## **JTAG INTERFACE**

Five additional pins (TDI, TDO, TMS, TCK and TRST) are provided to support the JTAG boundary scan interface. The IDT72V14320/72V15320/72V16320/72V17320/72V19320 incorporates the necessary tap controller and modified pad cells to implement the JTAG facility.

Note that IDT provides appropriate Boundary Scan Description Language program files for these devices.

The Standard JTAG interface consists of four basic elements:

- Test Access Port (TAP)

- TAP controller

- Instruction Register (IR)

- Data Register Port (DR)

The following sections provide a brief description of each element. For a complete description refer to the IEEE Standard Test Access Port Specification (IEEE Std. 1149.1-1990).

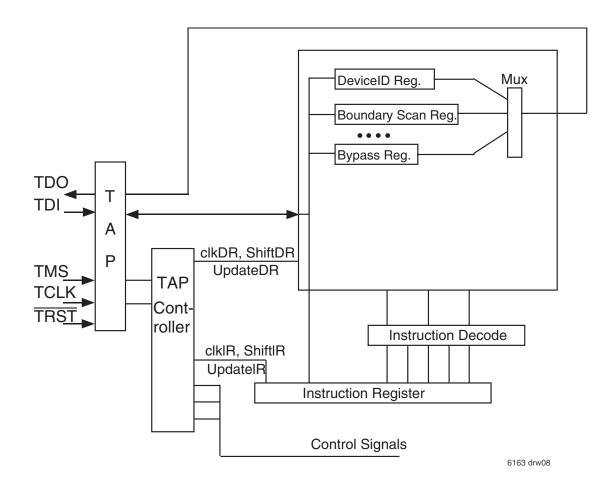

The Figure below shows the standard Boundary-Scan Architecture

Figure 3. Boundary Scan Architecture

#### **TEST ACCESS PORT (TAP)**

The Tap interface is a general-purpose port that provides access to the internal of the processor. It consists of four input ports (TCLK, TMS, TDI, TRST) and one output port (TDO).

#### **THE TAP CONTROLLER**

The Tap controller is a synchronous finite state machine that responds to TMS and TCLK signals to generate clock and control signals to the Instruction and Data Registers for capture and update of data.

#### NOTES:

1. Five consecutive TCK cycles with TMS = 1 will reset the TAP.

2. TAP controller does not automatically reset upon power-up. The user must provide a reset to the TAP controller (either by TRST or TMS).

3. TAP controller must be reset before normal FIFO operations can begin.

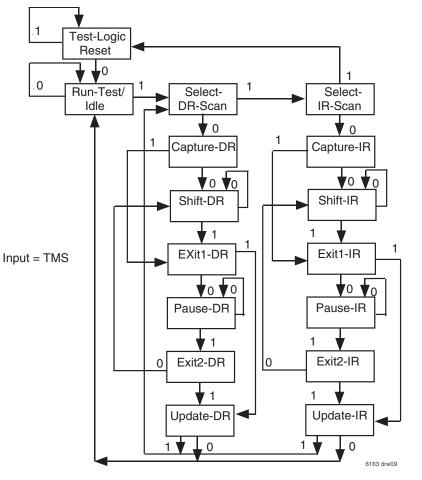

#### Figure 4. TAP Controller State Diagram

Refer to the IEEE Standard Test Access Port Specification (IEEE Std. 1149.1) for the full state diagram

All state transitions within the TAP controller occur at the rising edge of the TCLK pulse. The TMS signal level (0 or 1) determines the state progression that occurs on each TCLK rising edge. The TAP controller takes precedence over the FIFO memory and must be reset after power up of the device. See TRST description for more details on TAP controller reset.

Test-Logic-Reset All test logic is disabled in this controller state enabling the normal operation of the IC. The TAP controller state machine is designed in such a way that, no matter what the initial state of the controller is, the Test-Logic-Reset state can be entered by holding TMS at high and pulsing TCK five times. This is the reason why the Test Reset (TRST) pin is optional.

**Run-Test-Idle** In this controller state, the test logic in the IC is active only if certain instructions are present. For example, if an instruction activates the self test, then it will be executed when the controller enters this state. The test logic in the IC is idles otherwise.

**Select-DR-Scan** This is a controller state where the decision to enter the Data Path or the Select-IR-Scan state is made.

Select-IR-Scan This is a controller state where the decision to enter the Instruction Pathis made. The Controller can return to the Test-Logic-Reset state other wise.

**Capture-IR** In this controller state, the shift register bank in the Instruction Register parallel loads a pattern of fixed values on the rising edge of TCK. The last two significant bits are always required to be "01".

**Shift-IR** In this controller state, the instruction register gets connected between TDI and TDO, and the captured pattern gets shifted on each rising edge of TCK. The instruction available on the TDI pin is also shifted in to the instruction register.

**Exit1-IR** This is a controller state where a decision to enter either the Pause-IR state or Update-IR state is made.

**Pause-IR** This state is provided in order to allow the shifting of instruction register to be temporarily halted.

**Exit2-DR** This is a controller state where a decision to enter either the Shift-IR state or Update-IR state is made.

**Update-IR** In this controller state, the instruction in the instruction register is latched in to the latch bank of the Instruction Register on every falling edge of TCK. This instruction also becomes the current instruction once it is latched.

**Capture-DR** In this controller state, the data is parallel loaded in to the data registers selected by the current instruction on the rising edge of TCK.

Shift-DR, Exit1-DR, Pause-DR, Exit2-DR and Update-DR These controller states are similar to the Shift-IR, Exit1-IR, Pause-IR, Exit2-IR and Update-IR states in the Instruction path.

#### IDT72V15160/16160/17160/18160/19160 - 3.3V 16-BIT V-III MULTIMEDIA FIFO IDT72V14320/15320/16320/17320/18320/19320 - 3.3V 32-BIT VX-III MULTIMEDIA FIFO

#### THE INSTRUCTION REGISTER

The Instruction register allows an instruction to be shifted in serially into the processor at the rising edge of TCLK.

The Instruction is used to select the test to be performed, or the test data register to be accessed, or both. The instruction shifted into the register is latched at the completion of the shifting process when the TAP controller is at Update-IR state.

The instruction register must contain 4 bit instruction register-based cells which can hold instruction data. These mandatory cells are located nearest the serial outputs they are the least significant bits.

#### **TEST DATA REGISTER**

The Test Data register contains three test data registers: the Bypass, the Boundary Scan register and Device ID register.

These registers are connected in parallel between a common serial input and a common serial data output.

The following sections provide a brief description of each element. For a complete description, refer to the IEEE Standard Test Access Port Specification (IEEE Std. 1149.1-1990).

#### **TEST BYPASS REGISTER**

The register is used to allow test data to flow through the device from TDI to TDO. It contains a single stage shift register for a minimum length in serial path. When the bypass register is selected by an instruction, the shift register stage is set to a logic zero on the rising edge of TCLK when the TAP controller is in the Capture-DR state.

The operation of the bypass register should not have any effect on the operation of the device in response to the BYPASS instruction.

#### THE BOUNDARY-SCAN REGISTER

The Boundary Scan Register allows serial data TDI be loaded in to or read out of the processor input/output ports. The Boundary Scan Register is a part of the IEEE 1149.1-1990 Standard JTAG Implementation.

#### THE DEVICE IDENTIFICATION REGISTER

The Device Identification Register is a Read Only 32-bit register used to specify the manufacturer, part number and version of the processor to be determined through the TAP in response to the IDCODE instruction.

IDT JEDEC ID number is 0xB3. This translates to 0x33 when the parity is dropped in the 11-bit Manufacturer ID field.

For the IDT72V14320/72V15320/72V16320/72V17320/72V18320/ 72V19320, the Part Number field contains the following values:

| Device      | Part# Field |

|-------------|-------------|

| IDT72V14320 | 04E5        |

| IDT72V15320 | 04E4        |

| IDT72V16320 | 04E3        |

| IDT72V17320 | 04E2        |

| IDT72V18320 | 04E1        |

| IDT72V19320 | 04E0        |

| 31(MSB) 28       | 27 12                | 11 1                     | 0(LSB) |

|------------------|----------------------|--------------------------|--------|

| Version (4 bits) | Part Number (16-bit) | Manufacturer ID (11-bit) |        |

| 0X0              |                      | 0X33                     | 1      |

IDT72V14320/15320/16320/17320/18320/19320 JTAG Device Identification Register

#### JTAG INSTRUCTION REGISTER

The Instruction register allows instruction to be serially input into the device when the TAP controller is in the Shift-IR state. The instruction is decoded to perform the following:

- Select test data registers that may operate while the instruction is current. The other test data registers should not interfere with chip operation and the selected data register.

- Define the serial test data register path that is used to shift data between TDI and TDO during data register scanning.

The Instruction Register is a 4 bit field (i.e. IR3, IR2, IR1, IR0) to decode 16 different possible instructions. Instructions are decoded as follows.

| Hex<br>Value | Instruction    | Function                                 |

|--------------|----------------|------------------------------------------|

| 0x00         | FXTEST         | Select Boundary Scan Register            |

| 0x00<br>0x02 | IDCODE         | Select Chip Identification data register |

|              |                |                                          |

| 0x01         | SAMPLE/PRELOAD | Select Boundary Scan Register            |