# LTC4263

# FEATURES

- IEEE 802<sup>®</sup>.3af Compliant

- Operation from a Single 48V Supply

- Fully Autonomous Operation without Microcontroller

- Internal MOSFET with Thermal Protection

- Power Management Works Across Multiple Ports with Simple RC Network

- Precision Inrush Control with Internal Sense Resistor

- Powered Device (PD) Detection and Classification

- AC and DC Disconnect Sensing

- Robust Short-Circuit Protection

- Pin-Selectable Detection Backoff for Midspan PSEs

- Classification Dependent I<sub>CUT</sub> Current Threshold

- LED Driver Indicates Port On and Blinks Status Codes

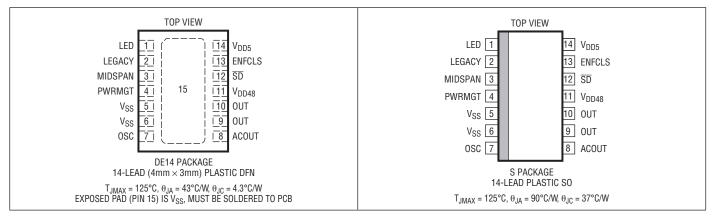

- Available in 14-Pin SO and 4mm × 3mm DFN Packages

# **APPLICATIONS**

- IEEE 802.3af Compliant Endpoint/Midspan PSEs

- Single-Port or Multi-Port Power Injectors

- Power Forwarders

- Low-Port Count PSEs

- Environment B PSEs

- Standalone PSEs

**Δ**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. Hot Swap and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## Single IEEE 802.3af Compliant PSE Controller with Internal Switch **DESCRIPTION**

The LTC<sup>®</sup>4263 is an autonomous single-channel PSE controller for use in IEEE 802.3af compliant Power over Ethernet systems. It includes an onboard power MOSFET, internal inrush, current limit, and short-circuit control, IEEE 802.3af compliant PD detection and classification circuitry, and selectable AC or DC disconnect sensing. Onboard control algorithms provide complete IEEE 802.3af compliant operation without the need of a microcontroller. The LTC4263 simplifies PSE implementation, needing only a single 48V supply and a small number of passive support components.

Programmable onboard power management circuitry permits multiple LTC4263s to allocate and share power in multi-port systems, allowing maximum utilization of the 48V power supply—all without the intervention of a host processor. The port current limit can be configured to automatically adjust to the detected PD class. Detection backoff timing is configurable for either Endpoint or Midspan operation. Built-in foldback and thermal protection provide comprehensive fault protection.

An LED pin indicates the state of the port controlled by the LTC4263. When run from a single 48V supply, the LED pin can operate as a simple switching current source to reduce power dissipation in the LED drive circuitry.

The LTC4263 is available in 14-pin 4mm  $\times$  3mm DFN and 14-pin SO packages.

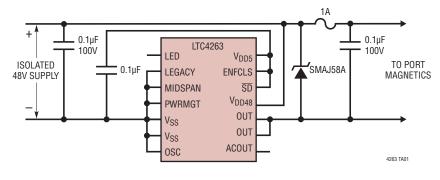

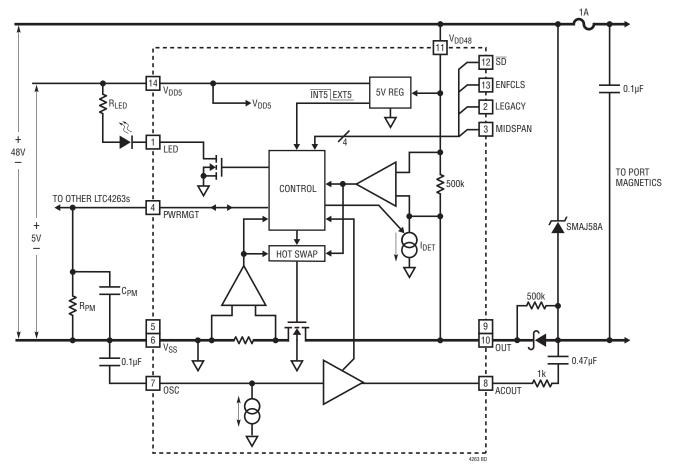

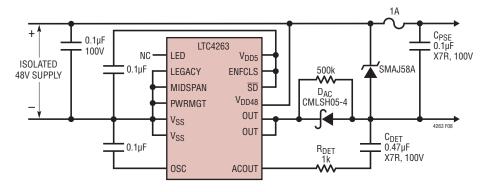

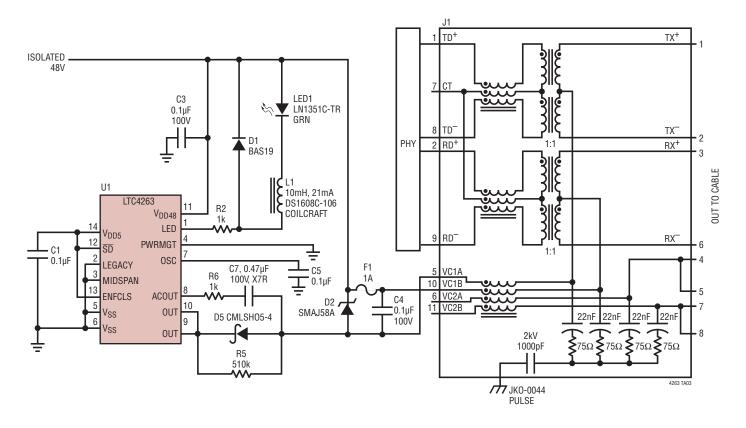

# TYPICAL APPLICATION

#### Single-Port Fully Autonomous PSE

# **ABSOLUTE MAXIMUM RATINGS**

#### Supply Voltages

| 80V |

|-----|

| 6V  |

|     |

|     |

| 6V  |

| 80V |

| 3)  |

|     |

#### (Notes 1, 2)

| Operating Ambient Temperature Range  |                |

|--------------------------------------|----------------|

| LTC4263C                             | 0°C to 70°C    |

| LTC42631                             | 40°C to 85°C   |

| Junction Temperature (Note 4)        | 125°C          |

| Storage Temperature Range            | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |                |

| S0                                   |                |

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC4263CDE#PBF   | LTC4263CDE#TRPBF | 4263          | 14-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4263IDE#PBF   | LTC4263IDE#TRPBF | 4263          | 14-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4263CS#PBF    | LTC4263CS#TRPBF  | 4263CS        | 14-Lead Plastic SO              | 0°C to 70°C       |

| LTC4263IS#PBF    | LTC4263IS#TRPBF  | 4263IS        | 14-Lead Plastic SO              | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DD48</sub> – V<sub>SS</sub> = 48V and V<sub>DD5</sub> not driven externally. All voltages are relative to V<sub>SS</sub> unless otherwise noted. (Notes 2, 5)

| SYMBOL                | PARAMETER             | CONDITIONS                                                               |   | MIN      | ТҮР | MAX      | UNITS  |

|-----------------------|-----------------------|--------------------------------------------------------------------------|---|----------|-----|----------|--------|

| Power Supp            | lies                  |                                                                          |   |          |     |          |        |

| V <sub>SUPPLY</sub>   | 48V Supply Voltage    | V <sub>DD48</sub> – V <sub>SS</sub><br>To Maintain IEEE Compliant Output | • | 33<br>46 | 48  | 66<br>57 | V<br>V |

| V <sub>UVL0_0FF</sub> | UVLO Turn-Off Voltage | V <sub>DD48</sub> – V <sub>SS</sub> Decreasing                           | • | 29       | 31  | 33       | V      |

| V <sub>UVLO_HYS</sub> | UVLO Hysteresis       |                                                                          | • | 0.1      |     | 1        | V      |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C.  $V_{DD48} - V_{SS} = 48V$  and  $V_{DD5}$  not driven externally. All voltages are relative to  $V_{SS}$  unless otherwise noted. (Notes 2, 5)

| SYMBOL                | PARAMETER                                       | CONDITIONS                                                                           |   | MIN                     | ТҮР                     | MAX                 | UNITS          |

|-----------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|---|-------------------------|-------------------------|---------------------|----------------|

| V <sub>OVLO_OFF</sub> | OVLO Turn-Off Voltage                           | V <sub>DD48</sub> – V <sub>SS</sub> Increasing                                       |   | 66                      | 70                      | 74                  | V              |

| V <sub>OVLO_HYS</sub> | OVLO Hysteresis                                 |                                                                                      |   | 0.2                     |                         | 2                   | V              |

| V <sub>DD5</sub>      | V <sub>DD5</sub> Supply Voltage                 | Driven Externally                                                                    |   | 4.5                     | 5                       | 5.5                 | V              |

|                       | V <sub>DD5</sub> Internal Supply                | Driven Internally                                                                    |   | 4.3                     | 4.4                     | 4.5                 | V              |

| I <sub>DD48</sub>     | V <sub>DD48</sub> Supply Current                | V <sub>DD5</sub> – V <sub>SS</sub> = 5V<br>Internal V <sub>DD5</sub>                 | • |                         | 1<br>2                  | 2<br>4              | mA<br>mA       |

| I <sub>DD5</sub>      | V <sub>DD5</sub> Supply Current                 | $V_{DD5} - V_{SS} = 5V$                                                              |   |                         | 1                       | 2                   | mA             |

| Power MOS             | SFET                                            |                                                                                      |   |                         |                         |                     |                |

| R <sub>ON</sub>       | On-Resistance                                   | I = 350mA, Measured From OUT to $V_{SS}$                                             | • |                         | 1.5                     | 2.4<br>3.0          | Ω<br>Ω         |

| I <sub>OUT_LEAK</sub> | OUT Pin Leakage                                 | $V_{OUT} - V_{SS} = V_{DD48} - V_{SS} = 57V$                                         |   |                         | 1                       | 10                  | μA             |

| R <sub>PU</sub>       | OUT Pin Pull-Up Resistance to V <sub>DD48</sub> | $0V \le (V_{DD48} - V_{OUT}) \le 5V$                                                 |   | 360                     | 500                     | 640                 | kΩ             |

| Current Co            | ntrol                                           |                                                                                      |   |                         |                         |                     |                |

| I <sub>CUT</sub>      | Overload Current Threshold                      | Class 0, Class 3, Class 4 (Note 6)<br>Class 2<br>Class 1                             | • | 355<br>165<br>95        | 375<br>175<br>100       | 395<br>185<br>105   | mA<br>mA<br>mA |

| I <sub>LIM</sub>      | Short-Circuit Current Limit                     | $V_{OUT} - V_{SS} = 5V$ $V_{DD48} - V_{OUT} = 30V$                                   | • | 405<br>405              | 425<br>425              | 445<br>445          | mA<br>mA       |

| I <sub>FB</sub>       | Foldback Current Limit                          | $V_{DD48} - V_{OUT} = 0V (Note 7)$<br>$V_{DD48} - V_{OUT} = 10V$                     | • | 30<br>110               | 60<br>140               | 120<br>180          | mA<br>mA       |

| I <sub>MIN</sub>      | DC Disconnect Current Threshold                 |                                                                                      |   | 5.2                     | 7.5                     | 9.8                 | mA             |

| I <sub>FAULT</sub>    | High Speed Fault Current Limit                  | (Note 8)                                                                             |   | 500                     | 650                     | 800                 | mA             |

| Detection             |                                                 |                                                                                      |   |                         |                         |                     |                |

| I <sub>DET</sub>      | Detection Current                               | First Point, $V_{DD48} - V_{OUT} = 10V$<br>Second Point, $V_{DD48} - V_{OUT} = 3.5V$ | • | 235<br>160              | 255<br>180              | 275<br>200          | μA<br>μA       |

| V <sub>DET</sub>      | Detection Voltage Compliance                    | $V_{DD48} - V_{OUT},$ Open Port $V_{DD48} - V_{SS} = 57V$                            | • |                         |                         | 21                  | V              |

| R <sub>DETMIN</sub>   | Minimum Valid Signature Resistance              |                                                                                      |   | 15.5                    | 17                      | 18.5                | kΩ             |

| R <sub>DETMAX</sub>   | Maximum Valid Signature Resistance              |                                                                                      |   | 27.5                    | 29.7                    | 32                  | kΩ             |

| R <sub>OPEN</sub>     | Open Circuit Threshold                          |                                                                                      |   | 500                     |                         | 2000                | kΩ             |

| Classificati          | ion                                             |                                                                                      |   |                         |                         |                     |                |

| V <sub>CLASS</sub>    | Classification Voltage                          | $V_{DD48} - V_{OUT}$ , $0mA \le I_{CLASS} \le 50mA$                                  |   | 16.5                    |                         | 20.5                | V              |

| I <sub>CLASS</sub>    | Classification Current Compliance               | $V_{OUT} = V_{DD48}$                                                                 |   | 55                      | 60                      | 75                  | mA             |

| I <sub>TCLASS</sub>   | Classification Threshold Current                | Class 0 – 1<br>Class 1 – 2<br>Class 2 – 3 (Note 9)                                   | • | 5.5<br>13.5<br>21.5     | 6.5<br>14.5<br>23       | 7.5<br>15.5<br>24.5 | mA<br>mA<br>mA |

| Power Mar             | nagement                                        |                                                                                      |   |                         |                         |                     |                |

| V <sub>PWRMGT</sub>   | Power Management Pin Threshold                  |                                                                                      |   | 0.98                    | 1                       | 1.02                | V              |

| I <sub>PWRMGT</sub>   | Power Management Pin Output Current             | Class 0, Class 3, Class 4<br>Class 1<br>Class 2                                      | • | -75.6<br>-19.6<br>-34.3 | -72.3<br>-18.8<br>-32.8 | 69<br>17.9<br>31.3  | μΑ<br>μΑ<br>μΑ |

| AC Disconr            | nect                                            |                                                                                      |   | 2.10                    | 02.0                    | 0.10                | P/1            |

| R <sub>OSC</sub>      | OSC Pin Input Impedance                         | $2V \le (V_{OSC} - V_{SS}) \le 3V$                                                   |   | 175                     | 250                     | 325                 | kΩ             |

| I <sub>OSC</sub>      | OSC Pin Output Current                          | $V_{OSC} - V_{SS} = 2V$                                                              |   | -140                    |                         | 140                 | μΑ             |

| f <sub>OSC</sub>      | OSC Pin Frequency                               | $\frac{V_{0SC} - V_{SS}}{V_{0SC} - V_{SS}} = 2V$                                     |   | 103                     | 110                     | 115                 | Hz             |

### ELECTRICAL CHARACTERISTICS

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{DD48} - V_{SS} = 48V$  and  $V_{DD5}$  not driven externally. All voltages are relative to V<sub>SS</sub> unless otherwise noted. (Notes 2, 5)

| SYMBOL              | PARAMETER                                                                           | CONDITIONS                                                                    |   | MIN        | ТҮР  | MAX        | UNITS    |

|---------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---|------------|------|------------|----------|

| A <sub>VACD</sub>   | Voltage Gain OSC to ACOUT                                                           | $2V \leq (V_{OSC} - V_{SS}) \leq 3V$                                          |   | 0.95       | 1.0  | 1.05       | V/V      |

| I <sub>ACDMAX</sub> | AC Disconnect Output Current                                                        | $V_{OSC} - V_{SS} = 2V, 0V \le (V_{ACOUT} - V_{SS}) \le 4V$                   |   | -1         |      | 1          | mA       |

| ACDMIN              | Remain Connected AC Pin Current                                                     | $V_{OSC} - V_{SS} = 2V$                                                       |   | 130        | 160  | 190        | μA       |

| V <sub>ACDEN</sub>  | AC Disconnect Enable Signal                                                         | V <sub>OSC</sub> – V <sub>SS</sub> , Port On                                  | ٠ | 1.5        |      |            | V        |

| Digital Inte        | erface (Note 10)                                                                    |                                                                               |   |            |      |            | <u> </u> |

| V <sub>OLED</sub>   | LED Output Low Voltage                                                              | I <sub>LED</sub> = 10mA                                                       |   |            | 1.1  | 2.2        | V        |

| V <sub>ILD</sub>    | Digital Input Low Voltage                                                           | MIDSPAN, PWRMGT, ENFCLS, SD LEGACY                                            | • |            |      | 0.8<br>0.4 | V<br>V   |

| V <sub>IHD</sub>    | Digital Input High Voltage                                                          | MIDSPAN, PWRMGT, ENFCLS, SD LEGACY                                            | • | 2.2<br>2.2 |      |            | V        |

| V <sub>OZ</sub>     | Voltage of Legacy Pin if Left Floating                                              |                                                                               |   | 1.1        | 1.25 | 1.4        | V        |

| I <sub>OLEG</sub>   | Current In/Out of Legacy Pin                                                        | $0V \le (V_{LEGACY} - V_{SS}) \le 5V$                                         | ٠ | -60        |      | 60         | μA       |

| I <sub>FLT</sub>    | Maximum Allowed Leakage of External Components at Legacy Pin in Force Power-On Mode |                                                                               | • | -10        |      | 10         | μA       |

| Timing Cha          | aracteristics                                                                       |                                                                               |   |            |      |            | <u> </u> |

| t <sub>DET</sub>    | Detection Time                                                                      | Beginning to End of Detection                                                 | • | 270        | 290  | 310        | ms       |

| t <sub>DETDLY</sub> | Detection Delay                                                                     | PD Insertion to Detection Complete                                            |   | 300        |      | 620        | ms       |

| t <sub>PDC</sub>    | Classification Duration                                                             |                                                                               |   | 34         | 37   | 39         | ms       |

| t <sub>PON</sub>    | Power Turn-On Delay                                                                 | End of Valid Detect to Application of Power                                   |   | 135        | 145  | 155        | ms       |

| t <sub>RISE</sub>   | Turn-On Rise Time                                                                   | V <sub>DD48</sub> – V <sub>OUT</sub> : 10% to 90%<br>C <sub>PSE</sub> = 0.1µF | • | 40         | 170  |            | μs       |

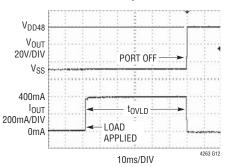

| t <sub>OVLD</sub>   | Overload/Short-Circuit Time Limit                                                   |                                                                               |   | 52         | 62   | 72         | ms       |

| t <sub>ED</sub>     | Error Delay                                                                         | I <sub>CUT</sub> Fault to Next Detect                                         | ٠ | 3.8        | 4.0  | 4.2        | S        |

| t <sub>MPD0</sub>   | Maintain Power Signature (MPS) Disconnect Delay                                     | PD Removal to Power Removal                                                   | ٠ | 320        | 350  | 380        | ms       |

| t <sub>MPS</sub>    | MPS Minimum Pulse Width                                                             | PD Minimum Current Pulse Width<br>Required to Stay Connected (Note 11)        | • |            |      | 20         | ms       |

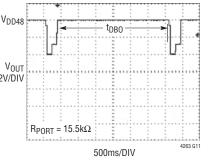

| t <sub>DBO</sub>    | Midspan Mode Detection Backoff                                                      | $R_{PORT} = 15.5 k\Omega$                                                     | ٠ | 3.0        | 3.2  | 3.4        | S        |

| tDISDLY             | Power Removal Detection Delay                                                       |                                                                               |   | 0.8        | 0.95 | 1.1        | s        |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to V<sub>SS</sub> unless otherwise specified.

Note 3: 80mA of current may be pulled from the OUT or ACOUT pin without damage whether the LTC4263 is powered or not. These pins will also withstand a positive voltage of V<sub>SS</sub> + 80V.

Note 4: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 5**: The LTC4263 operates with a negative supply voltage. To avoid confusion, voltages in this data sheet are referred to in terms of absolute magnitude.

Note 6: If the ENFCLS pin is high, I<sub>CUT</sub> depends on the result of classification. If ENFCLS pin is low,  $I_{CUT}$  reverts to its Class 0 specification. Note 7: In order to reduce power dissipated in the switch while charging the PD, the LTC4263 reduces the current limit when  $V_{OUT} - V_{SS}$  is large. Refer to the Typical Performance Characteristics for more information.

Note 8: The LTC4263 includes a high speed current limit circuit intended to protect against faults. The fault protection is activated for port current in excess of IFAULT. After the high speed current limit activates, the shortcircuit current limit (ILIM) engages and restricts current to IEEE 802.3af levels.

Note 9: Class 4 or higher classification current is treated as Class 3.

Note 10: The LTC4263 digital interface operates with respect to V<sub>SS</sub>. All logic levels are measured with respect to V<sub>SS</sub>.

Note 11: The IEEE 802.3af specification allows a PD to present its Maintain Power Signature (MPS) on an intermittent basis without being disconnected. In order to stay powered, the PD must present the MPS for t<sub>MPS</sub> within any t<sub>MPDO</sub> time window.

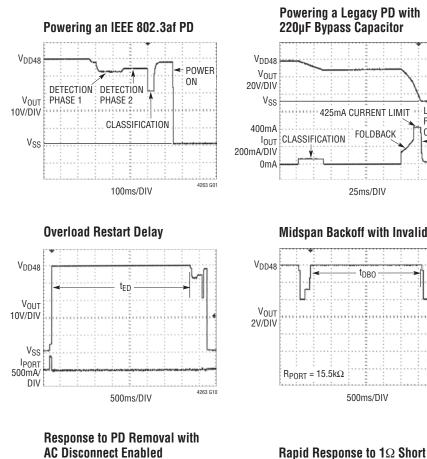

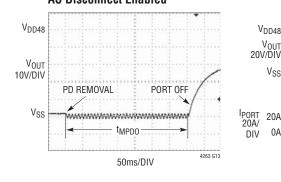

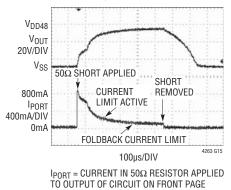

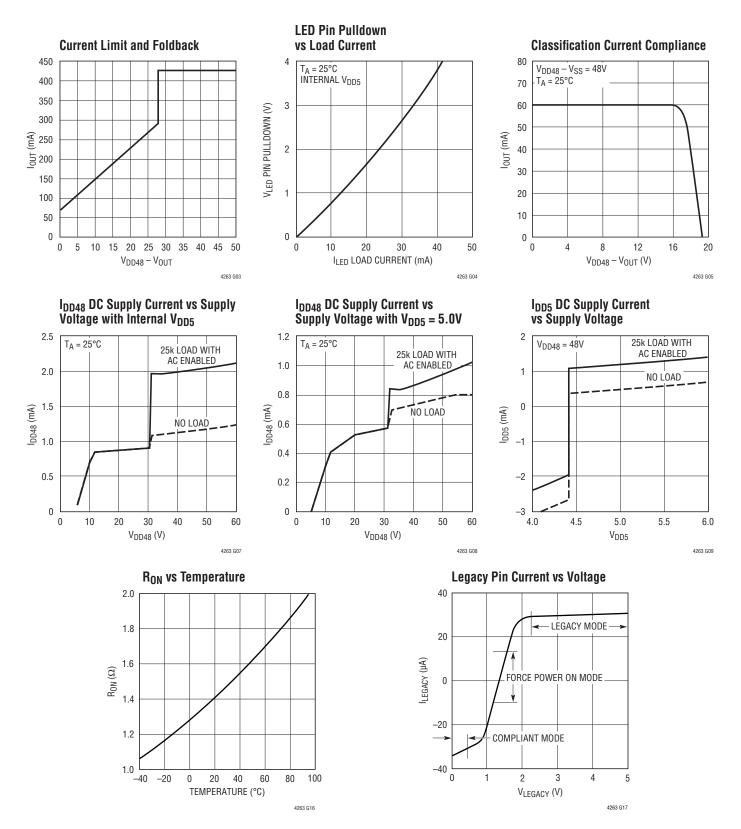

### **TYPICAL PERFORMANCE CHARACTERISTICS**

I<sub>PORT</sub> = CURRENT IN 1Ω RESISTOR APPLIED

TO OUTPUT OF CIRCUIT

4263 G14

ON FRONT PAGE

1µs/DIV

V<sub>DD48</sub>

Vss

0A

1Ω SHORT

APPLIED

V<sub>OUT</sub> 20V/DIV

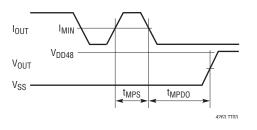

**Overcurrent Response Time**

#### **Rapid Response to** Momentary 50 $\Omega$ Short

# **TYPICAL PERFORMANCE CHARACTERISTICS**

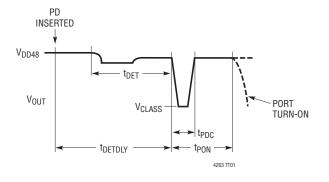

### **TEST TIMING**

#### Detect, Class and Turn-On Timing

#### DC Disconnect Timing

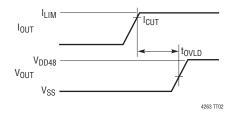

#### **Current Limit Timing**

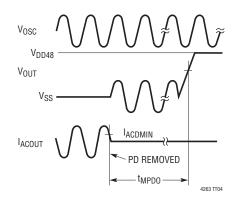

#### AC Disconnect Timing

## PIN FUNCTIONS (DFN/S0)

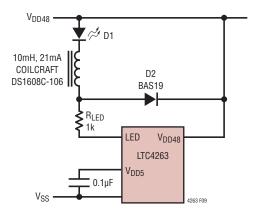

**LED (Pin 1):** Port State LED Drive. This pin is an open drain output that pulls down when the port is powered. Under port fault conditions, the LED will flash in patterns to indicate the nature of the port fault. See the Applications Information section for a description of these patterns. When the LTC4263 is operated from a single 48V supply, this pin is pulsed low with a 6% duty cycle during the periods when the LED should be on. This allows use of a simple inductor, diode, and resistor circuit to avoid excess heating due to the large voltage drop from V<sub>DD48</sub>. See the Applications Information section for details on this circuit.

**LEGACY (Pin 2):** Legacy Detect. This pin controls whether legacy detect is enabled. If held at  $V_{DD5}$ , legacy detect is enabled and testing for a large capacitor is performed to detect the presence of a legacy PD on the port. See the Applications Information section for descriptions of legacy PDs that can be detected. If held at  $V_{SS}$ , only IEEE 802.3af compliant PDs are detected. If left floating, the LTC4263 enters force-power-on mode and any PD that generates between 1V and 10V when biased with 270µA of detection current will be powered as a legacy device. This mode is useful if the system uses a differential detection scheme to detect legacy devices. Warning: Legacy modes are not IEEE 802.3af compliant.

**MIDSPAN (Pin 3):** Midspan Enable. If this pin is connected to  $V_{DD5}$ , Midspan backoff is enabled and a 3.2 second delay occurs after every failed detect cycle unless the result is open circuit. If held at  $V_{SS}$ , no delay occurs after failed detect cycles.

**PWRMGT (Pin 4):** Power Management. The LTC4263 sources current at the PWRMGT pin proportional to the class of the PD that it is powering. The voltage of this pin is checked before powering the port. The port will not turn on if this pin is more than 1V above  $V_{SS}$ . Connect the PWRMGT pins of multiple LTC4263s together with a resistor and capacitor to  $V_{SS}$  to implement power management. If power management is not used, tie this pin to  $V_{SS}$ .

**V<sub>SS</sub> (Pins 5, 6):** Negative 48V Supply. Pins 5 and 6 should be tied together on the PCB.

**OSC (Pin 7)** Oscillator for AC Disconnect. If AC disconnect is used, connect a  $0.1\mu$ F X7R capacitor from OSC to V<sub>SS</sub>. Tie OSC to V<sub>SS</sub> to disable AC disconnect and enable DC disconnect.

**ACOUT (Pin 8):** AC Disconnect Sense. Senses the port to determine whether a PD is still connected when in AC disconnect mode. If port capacitance drops below about 0.15 $\mu$ F for longer than T<sub>MPDO</sub> the port is turned off. If AC disconnect is used, connect this pin to the port with a series combination of a 1k resistor and a 0.47 $\mu$ F 100V X7R capacitor. See the Applications Information section for more information.

**OUT (Pins 9, 10):** Port Output. If DC disconnect is used, these pins are connected to the port. If AC disconnect is used, these pins are connected to the port through a parallel combination of a 1A diode and a 500k resistor. Pins 9 and 10 should be tied together on the PCB. See the Applications Information section for more information.

$V_{DD48}$  (Pin 11): 48V Return. Must be bypassed with a 0.1  $\mu F$  capacitor to  $V_{SS}.$

**SD** (Pin 12): Shutdown. If held low, the LTC4263 is prevented from performing detection or powering the port. Pulling  $\overline{SD}$  low will turn off the port if it is powered. When released, a 4-second delay will occur before detection is attempted.

**ENFCLS (Pin 13):** Enforce Class Current Limits. If held at  $V_{DD5}$ , the LTC4263 will reduce the  $I_{CUT}$  threshold for class 1 or class 2 PDs. If ENFCLS is held at  $V_{SS}$ ,  $I_{CUT}$  remains at 375mA (typ) for all classes.

$V_{DD5}$  (Pin 14): Logic Power Supply. Apply 5V referenced to V<sub>SS</sub>, if such a supply is available, or place a 0.1µF bypass capacitor to V<sub>SS</sub> to enable the internal regulator. When the internal regulator is used, this pin should only be connected to the bypass capacitor and to any logic pins of the LTC4263 that are being held at V<sub>DD5</sub>.

**Exposed Pad (Pin 15, DE Package Only):**  $V_{SS}$ . Must be connected to  $V_{SS}$  on the PCB. The Exposed Pad acts as a heatsink for the internal MOSFET.

# **BLOCK DIAGRAM**

BOLD LINES INDICATE HIGH CURRENT

9

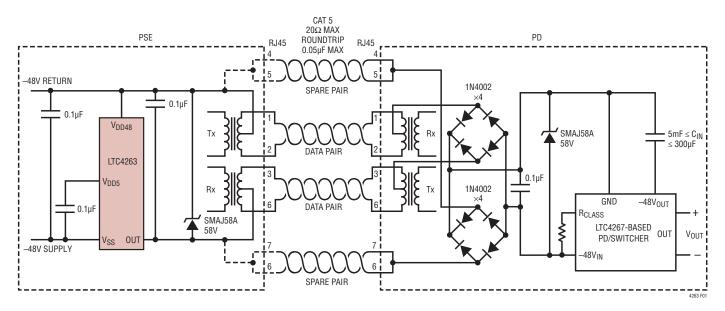

#### **POE OVERVIEW**

Over the years, twisted-pair Ethernet has become the most commonly used method for local area networking. The IEEE 802.3 group, the originator of the Ethernet standard, has defined an extension to the standard, IEEE 802.3af, which allows DC power to be delivered simultaneously over the same cable used for data communication. This has enabled a whole new class of Ethernet devices, including IP telephones, wireless access points, and PDA charging stations which do not require additional AC wiring or external power transformers, a.k.a. "wall warts." With about 13W of power available, small data devices can be powered by their Ethernet connections, free from AC wall outlets. Sophisticated detection and power monitoring techniques prevent damage to legacy data-only devices while still supplying power to newer, Ethernetpowered devices over the twisted-pair cable.

The device that supplies power is called the Power Sourcing Equipment (PSE). A device that draws power from the wire is called a Powered Device (PD). A PSE is typically an Ethernet switch, router, hub, or other network switching equipment that is commonly found in the wiring closets where cables converge. PDs can take many forms. Digital IP telephones, wireless network access points, PDA or notebook computer docking stations, cell phone chargers, and HVAC thermostats are examples of devices that can draw power from the network.

A PSE is required to provide a nominal 48V DC between either the signal pairs or the spare pairs (but not both) as shown in Figure 1. The power is applied as a voltage between two of the pairs, typically by powering the center taps of the isolation transformers used to couple the differential data signals to the wire. Since Ethernet data is transformer coupled at both ends and is sent differentially, a voltage difference between the transmit pairs and the receive pairs does not affect the data. A 10Base-T/ 100Base-TX Ethernet connection only uses two of the four pairs in the cable. The unused or spare pairs can optionally be powered directly, as shown in Figure 1, without affecting the data. 1000Base-T uses all four pairs and power must be connected to the transformer center taps if compatibility with 1000Base-T is required.

The LTC4263 provides a complete PSE solution for detection and powering of PD devices in an IEEE 802.3af compliant system. The LTC4263 controls a single PSE port that will detect, classify, and provide isolated 48V power to a PD device connected to the port. The LTC4263 senses removal of a PD with IEEE 802.3af compliant AC or DC methods and turns off 48V power when the PD is disconnected. An internal control circuit takes care of system configuration and timing.

#### LTC4263 OPERATION

#### **Signature Detection**

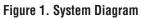

The IEEE 802.3af specification defines a specific pair-topair signature resistance used to identify a device that can accept power via its Ethernet connection. When the port voltage is below 10V, an IEEE 802.3af compliant PD will have an input resistance of approximately 25k $\Omega$ . Figure 2 illustrates the relationship between the PD signature resistance and the required resistance ranges the PSE must accept and reject. According to the IEEE 802.3af specification, the PSE must accept PDs with signatures between 19k $\Omega$  and 26.5k $\Omega$  and may or may not accept resistances in the two ranges of 15k $\Omega$  to 19k $\Omega$  and 26.5k $\Omega$ to 33k $\Omega$ . The black box in Figure 2 represents the typical 150 $\Omega$  pair-to-pair termination used in Ethernet devices like a computer's network interface card (NIC) that cannot accept power.

Figure 2. IEEE 802.3af Signature Resistance Ranges

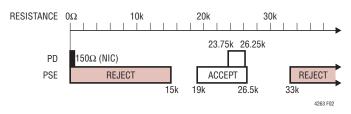

The LTC4263 checks for the signature resistance by forcing two test currents on the port in sequence and measuring the resulting voltages. It then subtracts the two V-I points to determine the resistive slope while removing voltage offset caused by any series diodes or current offset caused by leakage at the port (see Figure 3). The LTC4263 will typically accept any PD resistance between  $17k\Omega$  and  $29.7k\Omega$  as a valid PD. Values outside this range (excluding open and short-circuits) are reported to the user by a code flashed via the LED pin.

The LTC4263 uses a force-current detection method in order to reduce noise sensitivity and provide a more robust detection algorithm. The first test point is taken by forcing a test current into the port, waiting a short time to allow

Figure 3. PD 2-Point Detection

the line to settle and measuring the resulting voltage. This result is stored and the second current is applied to the port, allowed to settle and the voltage measured.

The LTC4263 will not power the port if the PD has more than  $5\mu$ F in parallel with its signature resistor unless legacy mode is enabled.

The LTC4263 autonomously tests for a valid PD connected to the port. It repeatedly queries the port every 580ms, or every 3.2s if midspan backoff mode is active (see below). If detection is successful, it performs classification and power management and then powers up the port.

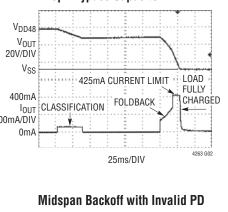

#### Midspan Backoff

IEEE 802.3af requires the midspan PSE to wait two seconds after a failed detection before attempting to detect again unless the port resistance is greater than 500k $\Omega$ . This requirement is to prevent the condition of an endpoint PSE and a midspan PSE, connected to the same PD at the same time, from each corrupting the PD signature and preventing power-on. After the first corrupted detection cycle, the midspan PSE waits while the endpoint PSE completes detection and turns the port on. If the midspan mode of the LTC4263 is enabled by connecting the MIDSPAN pin to V<sub>DD5</sub>, a 3.2 second delay occurs after every failed detect cycle unless the result is an open circuit.

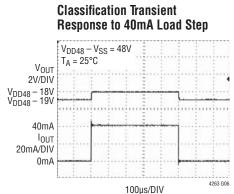

#### Classification

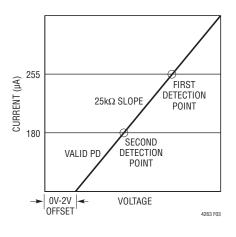

An IEEE 802.3af PD has the option of presenting a classification signature to the PSE to indicate how much power it will draw when operating. This signature consists of a specific constant-current draw when the PSE port voltage is between 15.5V and 20.5V, with the current level

Figure 4. Classification Load Lines

indicating the power class to which the PD belongs. Per the IEEE 802.3af specification, there are five classes and three power levels for a PD as shown in Table 1. Note that class 4 is presently reserved by the IEEE for future use. Figure 4 shows an example PD load line, starting with the shallow slope of the 25k signature resistor below 10V, then drawing the classification current (in this case, class 3) between 15.5V and 20.5V. Also shown is the load line for the LTC4263. It maintains a low impedance until reaching current limit at 60mA (typ).

The LTC4263 will classify a port immediately after a successful detection. It measures the PD classification signature current by applying 18V (typ) to the port and measuring the resulting current. The LTC4263 identifies the three IEEE power levels and stores the detected class internally for use by the power management circuitry. In addition, the LTC4263 allows selectable enforcement of IEEE classification power levels. With the ENFCLS pin high, the LTC4263 reduces the I<sub>CUT</sub> current threshold if it detects class 1 or class 2, thereby insuring that PDs which violate their advertised class are shut down.

| IEEE 802.3af<br>CLASS | CLASSIFICATION<br>CURRENT | MAXIMUM<br>IEEE ALLOWABLE<br>PD POWER | LTC4263<br>ENFORCED I <sub>CUT</sub><br>THRESHOLD* | CLASS DESCRIPTION                                   |

|-----------------------|---------------------------|---------------------------------------|----------------------------------------------------|-----------------------------------------------------|

| 0                     | 0mA to 5mA                | 12.95W                                | 375mA (typ)                                        | PD Does Not Implement Classification, Unknown Power |

| 1                     | 8mA to 13mA               | 3.84W                                 | 100mA (typ)                                        | Low Power PD                                        |

| 2                     | 16mA to 21mA              | 6.49W                                 | 175mA (typ)                                        | Medium Power PD                                     |

| 3                     | 25mA to 31mA              | 12.95W                                | 375mA (typ)                                        | Full Power PD                                       |

| 4                     | 35mA to 45mA              | 12.95W                                | 375mA (typ)                                        | Reserved, Power as Class 0                          |

Table 1. IEEE 802.3af Classification, PD Power Consumption, and LTC4263 Enforced Power Output

\*Enforced I<sub>CUT</sub> active if ENFCLS pin is high. Otherwise, I<sub>CUT</sub> is 375mA (typ).

#### **Power Management**

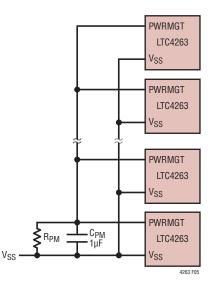

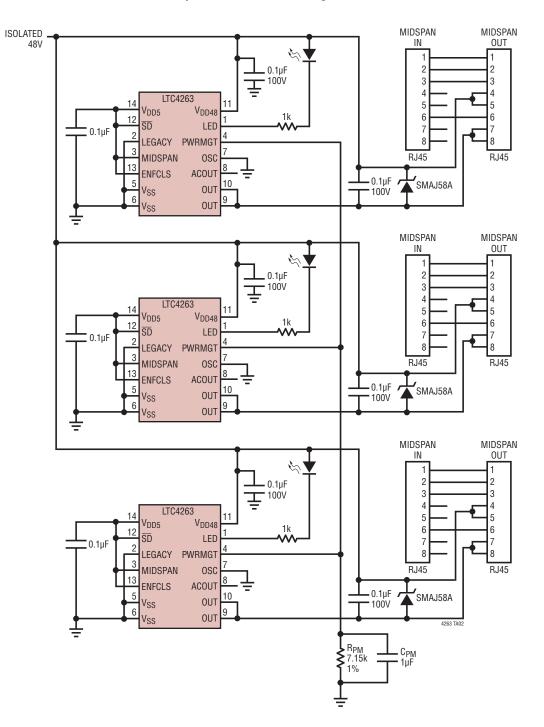

The LTC4263 includes a power management feature allowing simple implementation of power management across multiple ports driven by a single power supply. The PWRMGT pins of all LTC4263 devices are tied together along with an RC network to prevent over-allocation of power in a multi-port system.

Immediately following classification, the LTC4263 performs a power management check to ensure power is available to supply the newly classed PD. The allocated power is represented by the voltage on the shared PWRMGT node and the LTC4263 checks the allocated power by measuring this voltage. If the PWRMGT voltage is less than 1V, there is power available and the power needs of the new PD are added to the already allocated power on the node. To allocate power, a current proportional to the power needs for the new PD is sourced out of the PWRMGT pin (Table 2).

| Table 2. LT | C4263 Powe | r Management |

|-------------|------------|--------------|

|-------------|------------|--------------|

| ~                            |                                             |

|------------------------------|---------------------------------------------|

| PSE OUTPUT<br>POWER REQUIRED | LTC4263 PWRMGT<br>CURRENT                   |

| 15.4W                        | -72.3μA                                     |

| 7W                           | –32.8μA                                     |

| 4W                           | –18.8μA                                     |

|                              | PSE OUTPUT<br>POWER REQUIRED<br>15.4W<br>7W |

When additional current is added to the PWRMGT node, the voltage rises toward the 1V threshold. After adding current, the LTC4263 verifies that the power supply is not over-allocated by verifying the node voltage remains below 1V. If the voltage is below 1V, the LTC4263 proceeds to power the port. If over 1V, the current is removed from the node, port powering is aborted, and the LTC4263 goes back into detection mode. For multiple LTC4263s implementing power management, the PWRMGT pins are connected together and to a RC network connected to  $V_{SS}$  as shown in Figure 5. The value of  $R_{PM}$  represents the full load output capability of the system power supply ( $P_{FULL\_LOAD}$ ). Select a 1% resistor to set the full load output power using the following formula:

$$\mathsf{R}_{\mathsf{PM}} = \frac{213 \mathsf{k} \Omega \bullet \mathsf{W}}{\mathsf{P}_{\mathsf{FULL\_LOAD}}}$$

The LTC4263 power management uses pulse width modulation to set the power requirements of each PD. Capacitor  $C_{PM}$  is used as a lowpass filter to generate the average power requirement for all PDs in the system. Set  $C_{PM}$  to  $1\mu$ F.

If power management is not used, tie PWRMGT to V<sub>SS</sub>.

Figure 5. PWRMGT Pin Connections

4263f

#### Power Control

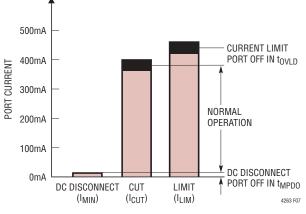

The primary function of the LTC4263 is to control the delivery of power to the PSE port. In order to meet IEEE 802.3af requirements and provide a robust solution, a variety of current limit and current monitoring functions are needed, as shown in Figure 6. All control circuitry is integrated and the LTC4263 requires no external MOSFET, sense resistor, or microcontroller to achieve IEEE compliance.

The LTC4263 includes an internal MOSFET for driving the PSE port. The LTC4263 drives the gate of the internal MOSFET while monitoring the current and the output voltage at the OUT pin. This circuitry couples the 48V input supply to the port in a controlled manner that satisfies the PD's power needs while minimizing disturbances on the 48V backplane.

Figure 6. Current Thresholds and Current Limits

#### Port Overload

A PSE port is permitted to supply up to 15.4W continuously and up to 400mA ( $I_{CUT}$ ) for up to 75ms ( $t_{OVID}$ ) when in overload. Per the IEEE 802.3af specification, the PSE is required to remove power if a port stays in an overload condition. The LTC4263 monitors port current and removes port power if port current exceeds 375mA (typ) for greater than 62ms (typ).

#### Port Inrush and Short-Circuit

The IEEE 802.3af standard lists two separate maximum current limits, I<sub>INBUSH</sub> and I<sub>I IM</sub>, that a PSE must implement. I<sub>INRUSH</sub> refers to current at port turn-on and I<sub>LIM</sub> is the maximum allowable current in the case of a short after the port is powered. Because the IEEE specification calls out identical values, the LTC4263 implements both as a single current limit referred to as I<sub>LIM</sub>.

When 48V power is applied to the port, the LTC4263 is designed to power-up the PD in a controlled manner without causing transients on the input supply. To accomplish this, the LTC4263 implements inrush current limit. At turn-on, current limit will allow the port voltage to guickly rise until the PD reaches its input turn-on threshold. At this point, the PD begins to draw current to charge its bypass capacitance, slowing the rate of port voltage increase.

If at any time the port is shorted or an excessive load is applied, the LTC4263 limits port current to avoid a hazardous condition. The current is limited to I<sub>I IM</sub> for port voltages above 30V and is reduced for lower port voltages (see the Foldback section). Inrush and short-circuit current limit are allowed to be active for 62ms (typ) before the port is shut off.

#### **Port Fault**

If the port is suddenly shorted, the internal MOSFET power dissipation can rise to very high levels until the short-circuit current limit circuit can respond. A separate high speed current limit circuit detects severe fault conditions ( $I_{OUT}$  > 650mA (typ)) and quickly turns off the internal MOSFET if such an event occurs. The circuit then limits current to I<sub>LIM</sub> while the t<sub>OVLD</sub> timer increments. During a short-circuit, ILIM will be reduced by the foldback circuitry.

### tovi D Timing

For overload, inrush, and short-circuit conditions, the IEEE 802.3af standard limits the duration of these events to 50ms-75ms. The LTC4263 includes a 62ms (typ) toyl n timer to monitor overload conditions. The timer is incremented whenever current greater than I<sub>CUT</sub> flows through the port. If the current is still above  $I_{CUT}$  when the  $t_{OVLD}$ timer expires, the LTC4263 will turn off power to the port and flash the LED. In this situation, the LTC4263 waits four seconds and then restarts detection. If the overload

condition is removed before the  $t_{\mbox{OVLD}}$  timer expires, the port stays powered and the timer is reset.

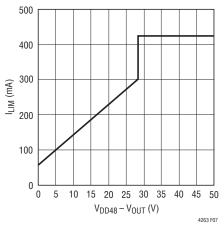

#### Foldback

Foldback is designed to limit power dissipation in the LTC4263 during power-up and momentary short-circuit conditions. At low port output voltages, the voltage across the internal MOSFET is high, and power dissipation will be large if significant current is flowing. Foldback monitors the port output voltage and reduces the  $I_{LIM}$  current limit level for port voltages of less than 28V, as shown in Figure 7.

Figure 7. Current Limit Foldback

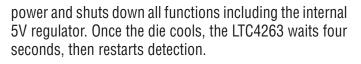

### **Thermal Protection**

The LTC4263 includes thermal overload protection in order to provide full device functionality in a miniature package while maintaining safe operating temperatures. Several factors create the possibility for very large power dissipation within the LTC4263. At port turn-on, while I<sub>LIM</sub> is active, the instantaneous power dissipated by the LTC4263 can be as high as 12W. This can cause 40°C or more of die heating in a single turn-on sequence. Similarly, excessive heating can occur if an attached PD repeatedly pushes the LTC4263 into I<sub>LIM</sub> by drawing too much current. Excessive heating can also occur if the V<sub>DD5</sub> pin is shorted or overloaded.

The LTC4263 protects itself from thermal damage by monitoring die temperature. If the die temperature exceeds the overtemperature trip point, the LTC4263 removes port

### DC Disconnect

The DC disconnect circuit monitors port current whenever power is on to detect continued presence of the PD. IEEE 802.3af mandates a minimum current of 10mA that the PD must draw for periods of at least 75ms with optional dropouts of no more than 250ms. The  $t_{MPDO}$  disconnect timer increments whenever port current is below 7.5mA (typ). If the timer expires, the port is turned off and the LTC4263 waits 1.5 seconds before restarting detection. If the undercurrent condition goes away before  $t_{MPDO}$  (350ms (typ)), the timer is reset to zero. The DC disconnect circuit includes a glitch filter to prevent noise from falsely resetting the timer. The current must be present for a period of at least 20ms to guarantee reset of the timer. To enable DC disconnect, tie the OSC pin to V<sub>SS</sub>.

#### AC Disconnect

AC disconnect is an alternate method of sensing the presence or absence of a PD by monitoring the port impedance. The LTC4263 forces an AC signal from an internal sine wave generator on to the port. The ACOUT pin current is then sampled once per cycle and compared to  $I_{ACDMIN}$ . Like DC disconnect, the AC disconnect sensing circuitry controls the  $t_{MPDO}$  disconnect timer. When the connection impedance rises due to the removal of the PD, AC peak current falls below  $I_{ACDMIN}$  and the disconnect timer increments. If the impedance remains high (AC peak current remains below  $I_{ACDMIN}$ ), the disconnect timer counts to  $t_{MPDO}$  and the port is turned off. If the impedance falls, causing AC peak current to rise above  $I_{ACDMIN}$  for two consecutive samples before the maximum count of the disconnect timer, the timer resets and the port remains powered.

The AC disconnect circuitry senses the port via the ACOUT pin. Connect a 0.47 $\mu$ F 100V X7R capacitor (C<sub>DET</sub>) and a 1k $\Omega$  resistor (R<sub>DET</sub>) from the DETECT pin to the port output as shown in Figure 8. This provides an AC path for sensing the port impedance. The 1k $\Omega$  resistor, R<sub>DET</sub>, limits current flowing through this path during port power-on and power-off. An AC blocking diode (D<sub>AC</sub>) is inserted between the OUT pin and the port to prevent the AC signal from 4283fe

Figure 8. LTC4263 Using AC Disconnect

being shorted by the LTC4263's power control MOSFET. The 500k resistor across  $D_{AC}$  allows the port voltage to decay after disconnect occurs.

Sizing of capacitors is critical to ensure proper function of AC disconnect.  $C_{PSE}$  (Figure 8) controls the connection impedance on the PSE side. Its capacitance must be kept low enough for AC disconnect to be able to sense the PD. On the other hand,  $C_{DET}$  has to be large enough to pass the signal at 110Hz. The recommended values are  $0.1\mu$ F for  $C_{PSE}$  and  $0.47\mu$ F for  $C_{DET}$ . The sizes of  $C_{PSE}$ ,  $C_{DET}$ , and  $R_{DET}$  are chosen to create an economical, physically compact and functionally robust system. Moreover, the complete Power over Ethernet AC disconnect system (PSE, transformers, cabling, PD, etc.) is complex; deviating from the recommended values of  $C_{DET}$ ,  $R_{DET}$  and  $C_{PSE}$  is strongly discouraged. Contact the Linear Technology Applications department for additional support.

#### Internal 110Hz AC Oscillator

The LTC4263 includes onboard circuitry to generate a 110Hz (typ),  $2V_{P-P}$  sine wave on its OSC pin when a 0.1µF capacitor is connected between the OSC pin and V<sub>SS</sub>. This sine wave is synchronized to the controller inside the LTC4263 and should not be externally driven. Tying the OSC pin to V<sub>SS</sub> shuts down the oscillator and enables DC disconnect.

#### Power-On Reset and Reset/Backoff Timing

Upon start-up, the LTC4263 waits four seconds before starting its first detection cycle. Depending on the results of this detection it will either power the port, repeat

detection, or wait 3.2 seconds before attempting detection again if in midspan mode.

The LTC4263 may be reset by pulling the  $\overline{SD}$  pin low. The port is turned off immediately and the LTC4263 sits idle. After  $\overline{SD}$  is released there will be a 4-second delay before the next detection cycle begins.

#### V<sub>DD5</sub> Logic-Level Supply

The V<sub>DD5</sub> supply for the LTC4263 can either be supplied externally or generated internally from the V<sub>DD48</sub> supply. If supplied externally, a voltage between 4.5V and 5.5V should be applied to the V<sub>DD5</sub> pin to cause the internal regulator to shut down. If V<sub>DD5</sub> is to be generated internally, the voltage will be 4.4V (typ) and a 0.1µF capacitor should be connected between V<sub>DD5</sub> and V<sub>SS</sub>. Do not connect the internally generated V<sub>DD5</sub> to anything other than a bypass capacitor and the logic control pins of the same LTC4263.

#### **LED Flash Codes**

The LTC4263 includes a multi-function LED driver to inform the user of the port status. The LED is turned on when the port is connected to a PD and power is applied. If the port is not connected or is connected to a non-powered device with a  $150\Omega$  or shorted termination, the port will not be powered and the LED will be off. For other port conditions, the LTC4263 blinks a code to communicate the status to the user as shown in Table 3. One flash indicates low signature resistance, two flashes indicates high resistance, five flashes indicates an overload fault, and nine flashes indicates that power management is preventing the port from turning on.

When active, the LED flash codes are repeated every 1.2 seconds. The duration of each LED flash is 75ms. Multiple LED flashes occur at a 300ms interval.

The LTC4263 includes a feature for efficiently driving the LED from a 48V power supply without the wasted power caused by having to drop over 45V in a current limit resistor. When operating the  $V_{DD5}$  supply internally, the LTC4263 drives the LED pin with a 6% duty cycle PWM signal. This allows use of the simple LED drive circuit in Figure 9 to minimize power dissipation. The modulation frequency of the LED drive is 28kHz, making the on period

Figure 9. LED Drive Circuit with Single 48V Supply

| PORT STATUS                                                   | LED FLASH CODE | FLASH PATTERN                                                                                                                                 |

|---------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Non-Powered Device $0\Omega < R_{PORT} < 200\Omega$           | Off            | LED Off                                                                                                                                       |

| Port Open $R_{PORT} > 1M\Omega$                               | Off            | LED Off                                                                                                                                       |

| Port On<br>25kΩ                                               | On             | LED On                                                                                                                                        |

| Low Signature Resistance $300\Omega < R_{PORT} < 15 k\Omega$  | 1 Flash        | $\dot{\mathbf{x}} \bullet \bullet \bullet \dot{\mathbf{x}} \bullet \bullet \bullet \dot{\mathbf{x}} \bullet \bullet \bullet \dot{\mathbf{x}}$ |

| High Signature Resistance $33k\Omega < R_{PORT} < 500k\Omega$ | 2 Flashes      | **                                                                                                                                            |

| Port Overload Fault                                           | 5 Flashes      |                                                                                                                                               |

| Power Management<br>Allocation Exceeded                       | 9 Flashes      | $\bullet \dot{\varphi} \dot{\varphi} \dot{\varphi} \dot{\varphi} \dot{\varphi} \dot{\varphi} \dot{\varphi} \dot{\varphi}$                     |

#### Table 3. Port Status and LED Flash Codes

2.2 $\mu$ s. During the 2.2 $\mu$ s that the LED pin is pulled low, current ramps up in the inductor, limited by R<sub>LED</sub>. Diode D2 completes the circuit by allowing current to circulate while the LED pin is open circuit. Since current is only drawn from the power supply 6% of the time, power dissipation is substantially reduced.

When  $V_{DD5}$  is powered from an external supply, the PWM signal is disabled and the LED pin will pull down continuously when on. In this mode, the LED can be powered from the 5V supply with a simple series resistor.

# IEEE 802.3af COMPLIANCE AND EXTERNAL COMPONENT SELECTION

This section discusses the other elements that go along with the LTC4263 to make an IEEE 802.3af compliant PSE. The LTC4263 is designed to control power delivery in IEEE 802.3af compliant Power Sourcing Equipment. Because proper operation of the LTC4263 also depends on external components and power sources like the 48V supply, using the LTC4263 in a PSE does not in itself guarantee IEEE 802.3af compliance. To ensure a compliant PSE design, it is recommended to adhere closely to the example application circuits provided. For further assistance contact the Linear Technology Applications department.

#### **Common Mode Chokes**

Both non-powered and powered Ethernet connections achieve best performance for data transfer and EMI when a common mode choke is used on each port. For cost reduction reasons, some designs share a common mode choke between two adjacent ports. This is not recommended. Sharing a common mode choke between two ports couples start-up, disconnect and fault transients from one port to the other. The end result can range from momentary noncompliance with IEEE 802.3af to intermittent behavior and even to excessive voltages that may damage circuitry in both the PSE and PD connected to the port.

#### Transient Suppressor Diode

IEEE 802.3af Power over Ethernet is a challenging Hot Swap<sup>™</sup> application because it must survive unintentional abuse by repeated plugging in and out of devices at the port. Ethernet cables could potentially be cut or shorted together. Consequently, the PSE must be designed to handle these events without damage.

The most severe of these events is a sudden short on a powered port. What the PSE sees depends on how much CAT-5 cable is between it and the short. If the short occurs on the far end of a long cable, the cable inductance will prevent the current in the cable from increasing too quickly and the LTC4263 built-in short-circuit protection will control the current and turn off the port. However, the high current along with the cable inductance causes a large flyback voltage to appear across the port when the MOSFET is turned off. In the case of a short occurring with a minimum length cable, the instantaneous current can be extremely high due to the lower inductance. The LTC4263 has a high speed fault current limit circuit that shuts down the port in 20µs (typ). In this case, there is lower inductance but higher current so the event is still severe. A transient suppressor is required to clamp the port voltage and prevent damage to the LTC4263. An SMAJ58A or equivalent device works well to maintain port voltages within a safe range. A bidirectional transient suppressor should not be used. Good board layout places the transient suppressor between the port and the LTC4263 to enhance the protective function.

If the port voltage reverses polarity and goes positive, the OUT pin can be overstressed because this voltage is stacked on top of the 48V supply. In this case, the transient suppressor must clamp the voltage to a small positive value to protect the LTC4263 and the PSE capacitor.

Component leakages across the port can have an adverse affect on AC disconnect and even affect DC disconnect if the leakage becomes severe. The SMAJ58A is rated at less than  $5\mu$ A leakage at 58V and works well in this application. There is a potential for stress induced leakage, so sufficient margins should be used when selecting transient suppressors for these applications.

#### Capacitors

Sizing of both the C<sub>DET</sub> and C<sub>PSE</sub> capacitors is critical for proper operation of the LTC4263 AC disconnect sensing. See the AC Disconnect section for more information. Note that many ceramic capacitors have dramatic DC voltage and temperature coefficients. Use 100V or higher rated X7R capacitors for C<sub>DET</sub> and C<sub>PSE</sub>, as these have reduced voltage dependence while also being relatively small and inexpensive. Bypass the 48V supply with a  $0.1\mu$ F, 100V capacitor located close to the LTC4263. The V<sub>DD5</sub> supply also requires a  $0.1\mu$ F bypass capacitor.

#### Fuse

While the LTC4263 does not require a fuse for proper operation or for compliance with IEEE 802.3af, some safety requirements state that the output current must be limited to less than 2A in less than 60 seconds if any one component fails or is shorted. Since the LTC4263 is the primary current limiter, its failure could result in excess current to the port. To meet these safety requirements, a fuse can be placed in the positive leg of the port. The fuse must be large enough that it will pass at least 450mA when derated for high temperature but small enough that it will fuse at less than 2A at cold temperature. This requirement can usually be satisfied with a 1A fuse or PTC. Placing the fuse between the RJ-45 connector and the LTC4263 and its associated circuitry provides additional protection for this circuitry. Consult a safety requirements expert for the application specific requirements.

#### **Power Supply**

Poor regulation on the 48V supply can lead to noncompliance. The IEEE specification requires a PSE output voltage between 44V and 57V. When the LTC4263 begins powering an Ethernet port, it controls the current through the port to minimize disturbances on V<sub>SS</sub>. However, if the V<sub>SS</sub> supply is underdamped or otherwise unstable, its voltage could go outside of the IEEE-specified limits, causing the PSE to be noncompliant. This scenario can be even worse when a PD is unplugged because the current can drop immediately to zero. In both cases the port voltage must always stay between 44V and 57V. Beyond this, the IEEE 802.3af specification places specific ripple, noise and load regulation requirements on the PSE. Disturbances on V<sub>SS</sub> can also adversely affect detection, classification and AC disconnect sensing. For these reasons, proper bypassing and stability of the  $V_{SS}$  supply is important.

Another problem that can affect the V<sub>SS</sub> supply is insufficient power, leading to the supply voltage dropping out of the specified range. The 802.3af specification states that if a PSE powers a PD it must be able to provide the maximum power level requested by the PD based on the PD's classification. The specification does allow a PSE to choose not to power a port, typically because the PD requires more power than the PSE has available to deliver. If a PSE is built with a V<sub>SS</sub> supply not capable of delivering full power to all ports, it is recommended to use the LTC4263 power management feature to prevent ports from being turned on when there is insufficient power. Because the specification also requires the PSE to supply an inrush current of 400mA at up to a 5% duty cycle, the V<sub>SS</sub> supply capability should be at least a few percent higher than the maximum total power the PSE needs to supply to the PDs.

#### Isolation

The IEEE 802.3af standard requires Ethernet ports to be electrically isolated from all other conductors that are user accessible. This includes the metal chassis, other connectors, and the AC power line. Environment A isolation is the most common and applies to wiring within a single building serviced by a single AC power system. For this type of application, the PSE isolation requirement can be met with the use of a single, isolated 48V supply powering several LTC4263 ports. Environment B, the stricter isolation requirement, is for networks that cross an AC power distribution boundary. In this case, electrical isolation must be maintained between each port in the PSE. The LTC4263 can be used to build a multi-port Environment B PSE by powering each LTC4263 from a separate, isolated 48V supply. In all PSE applications, there should be no user accessible connections to the LTC4263 other than the RJ-45 port.

# TYPICAL APPLICATIONS

Three Port Midspan PSE with Power Management Set for 30W

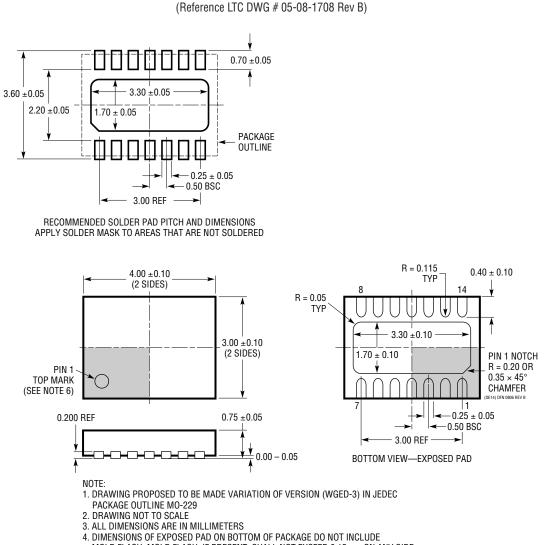

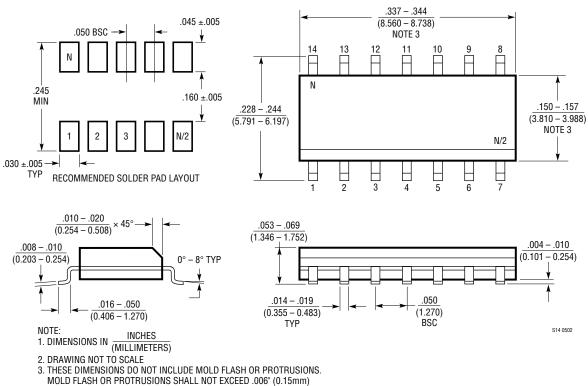

### PACKAGE DESCRIPTION

$\begin{array}{c} \text{DE Package} \\ \text{14-Lead Plastic DFN (4mm <math display="inline">\times \text{3mm})} \end{array}$

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

TOP AND BOTTOM OF PACKAGE

# **PACKAGE DESCRIPTION**

S Package 14-Lead Plastic Small Outline (Narrow .150 Inch) (Reference LTC DWG # 05-08-1610)

# **REVISION HISTORY** (Revision history begins at Rev E)

| REV | DATE | DESCRIPTION                                           | PAGE NUMBER |

|-----|------|-------------------------------------------------------|-------------|

| Е   | 6/10 | Replaced Figure 3 in Applications Information section | 11          |

# TYPICAL APPLICATION

Complete Single-Port Endpoint PSE with Integrated RJ45

# **RELATED PARTS**

| PART NUMBER                                                 | DESCRIPTION                                       | COMMENTS                                                                                                   |

|-------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| LTC1737                                                     | High Power Isolated Flyback Controller            | Sense Output Voltage Directly from Primary-Side Winding                                                    |

| LTC3803                                                     | Current Mode Flyback DC/DC Controller in ThinSOT™ | 200kHz Constant-Frequency, Adjustable Slope Compensation,<br>Optimized for High Input Voltage Applications |

| LTC4257                                                     | IEEE 802.3af PD Interface Controller              | 100V 400mA Internal Switch, Programmable Classification                                                    |

| LTC4257-1                                                   | IEEE 802.3af PD Interface Controller              | 100V 400mA Dual Current Limit                                                                              |

| LTC4258                                                     | Quad IEEE 802.3af Power Over Ethernet Controller  | DC Disconnect Only                                                                                         |

| LTC4259A-1 Quad IEEE 802.3af Power Over Ethernet Controller |                                                   | With AC Disconnect                                                                                         |

| LTC4267                                                     | IEEE 802.3af PD Interface with Switcher           | Integrated Current Mode Switching Regulator                                                                |

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком):

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

«JONHON» (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«FORSTAR» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный) Факс: 8 (812) 320-03-32 Электронная почта: ocean@oceanchips.ru Web: http://oceanchips.ru/ Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А