# **USB-910H**

# **Embedded Systems Interface**

### **FEATURES**

- SPI, I2C, SMBus Master or Slave

- Full I2C/SMBus Multi-Master Support

- Up to 9 General-Purpose I/O

- SMBus Timeouts and Bus-free Detect

- Supports PMBus Transport Layer

- Configurable I/O Levels from 1.65V to 5V

- SPI to 24MHz, I2C/SMBus to 1.5MHz

- Power the Target from the Adapter

- Responds to 16 Slave Addresses (or All)

- Up to 64kByte Transactions

- Powerful Scripting Feature

- Easy-to-use API for Software Development

- USB/HID No User-Installed Device Drivers

- Built-in I2C Pull-ups with Enable

### **GENERAL DESCRIPTION**

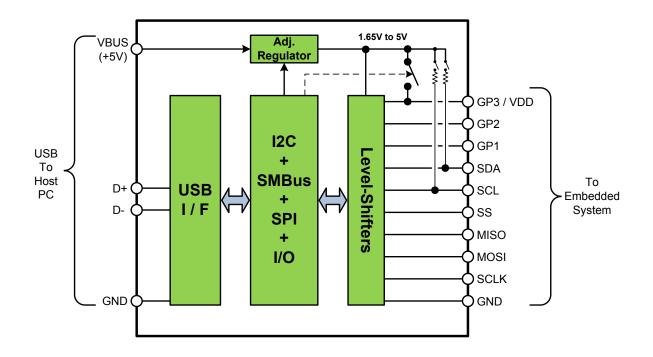

The Keterex USB-910H Embedded Systems Interface provides connectivity between a host PC and an embedded system requiring an I2C, SMBus, or SPI protocol. Other protocols can be supported by "bit-banging" up to 9 available general-purpose I/O. USB transactions are generated on the host PC using either the Keterex USB-900 Control Center application or calls to a provided API. The USB-910H Adapter converts these transactions to I2C, SMBus, SPI, or generalpurpose I/O operations. Built-in scripting accommodates complex bus protocols, including combining bus transactions, timing, and generalpurpose I/O operations.

The USB-910H Adapter provides configurable I/O voltage levels from 1.65V to 5V. In addition to setting the drive and sense logic levels, this voltage can be connected to the target hardware, providing up to 400mA to the target device.

## **FUNCTIONAL BLOCK DIAGRAM**

## 1. RELATED DOCUMENTS

The following Keterex documents describe other components of the USB-910H Embedded Systems Interface:

- 1. Application Note AN2101 The USB-910H API and Include File Reference Manual.

- 2. Application Note AN2102 The USB-900 Control Center User's Guide.

### 2. REFERENCES

This datasheet assumes the reader is familiar with the I2C, SMBus, PMBus, SPI, and similar interfaces and standards. The following references are recommended:

- 1. The I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000, Philips Semiconductors #939839340011.

- 2. The I<sup>2</sup>C-Bus and How to Use it, Philips Semiconductors #98808057501.

- 3. System Management Bus (SMBus) Specification, Version 2.0, August 3, 2000, SBS Implementers Forum.

- 4. PMBus<sup>TM</sup> Power System Management Protocol Specification, Part I General Requirements, Transport And Electrical Interface, Revision 1.0, System Management Interface Forum, Inc., 28 March 2005.

- 5. *MICROWIRE*<sup>TM</sup> Serial Interface, National Semiconductor, Application Note 452, January 1992.

# 3. PERFORMANCE CHARACTERISTICS

| PARAMETER                             | CONDITIONS                                    | MIN                   | TYP               | MAX                   | UNITS      |  |

|---------------------------------------|-----------------------------------------------|-----------------------|-------------------|-----------------------|------------|--|

| Over veltere Televenee                | except GP3                                    | -0.3                  |                   | VBUS+0.3              | V          |  |

| Over-voltage Tolerance                | GP3                                           | -0.3                  |                   | V <sub>IO</sub> +0.3  | V          |  |

| Torget I/O Voltage (V/ )              | configurable mode                             | 1.65                  |                   | 3.6                   | V          |  |

| Target I/O Voltage (V <sub>IO</sub> ) | JSB 5V bypass mode                            |                       | 5.0               |                       | V          |  |

| Target I/O Voltage Error              | configurable mode                             | -3                    |                   | +3                    | %          |  |

| Low-level Input Voltage               |                                               |                       |                   | V <sub>IO</sub> x 0.3 | V          |  |

| (except SDA and SCL)                  |                                               |                       |                   | V <sub>10</sub> X 0.3 | V          |  |

| High-level Input Voltage              |                                               | V <sub>IO</sub> x 0.7 |                   |                       | V          |  |

| (except SDA and SCL)                  |                                               | V <sub>10</sub> X U.7 |                   |                       | V          |  |

| Low-level Input Voltage               |                                               |                       |                   | 0.8                   | V          |  |

| (SDA and SCL only)                    |                                               |                       |                   | 0.0                   | V          |  |

| High-level Input Voltage              |                                               | 2.0                   |                   |                       | V          |  |

| (SDA and SCL only)                    |                                               | 2.0                   |                   |                       | <b>V</b>   |  |

|                                       | I <sub>OL</sub> =4mA, V <sub>IO</sub> =1.65V  |                       |                   | 0.5                   | v          |  |

| Low-level Output Voltage              | I <sub>OL</sub> =8mA, V <sub>IO</sub> =2.3V   |                       |                   | 0.4                   |            |  |

| Low-level Output voltage              | I <sub>OL</sub> =24mA, V <sub>IO</sub> =3V    |                       |                   | 0.8                   |            |  |

|                                       | I <sub>OL</sub> =32mA, V <sub>IO</sub> =4.5V  |                       |                   | 0.9                   |            |  |

|                                       | I <sub>OH</sub> =-4mA, V <sub>IO</sub> =1.65V | 1.2                   |                   |                       |            |  |

| High-level Output Voltage             | I <sub>OH</sub> =-8mA, V <sub>IO</sub> =2.3V  | 1.8                   |                   |                       | V          |  |

| l ligh-level Output voltage           | I <sub>OH</sub> =-24mA, V <sub>IO</sub> =3V   | 2.8                   |                   |                       | V          |  |

|                                       | I <sub>OH</sub> =-32mA, V <sub>IO</sub> =4.5V | 4.2                   |                   |                       |            |  |

| Input Leakage Current                 | $0V \le V_{IN} \le 5V$                        |                       |                   | ±2                    | μΑ         |  |

| SCL and SDA Pull-ups                  | when enabled                                  |                       | 2.2               |                       | kΩ         |  |

| I2C/SMBus Bit Rate                    |                                               | 31.75                 |                   | 1500                  | kbits/sec  |  |

| SPI Master Bit Rate                   |                                               | 93.75                 |                   | 24000                 | kbits/sec  |  |

| SPI Byte Throughput                   | Transactions < 4kbytes                        |                       | 170               |                       | kbytes/sec |  |

| SPI Slave Bit Rate                    |                                               |                       | 4000 <sup>†</sup> |                       | kbits/sec  |  |

| SPI Slave SS Setup                    |                                               | 3 <sup>∆</sup>        |                   |                       | µsec       |  |

| SCL Idle Bus Free Period              | when enabled                                  | 3.3                   |                   |                       | SCL        |  |

| SOL IUIE BUS FIEE PEIIOU              | when enabled                                  |                       | ა.ა               |                       | periods    |  |

| SCL Low Timeout Period                | when enabled (infinite                        |                       |                   | 32.7                  | msec       |  |

| _                                     | timeout when disabled)                        |                       |                   |                       |            |  |

<sup>&</sup>lt;sup>†</sup>This value depends strongly on the electrical characteristics of a particular system design, such as bus capacitance, etc. The maximum bit-rate the SPI Slave can support in the user's system may be higher or lower than this value.

<sup>&</sup>lt;sup>Δ</sup>This value assumes no additional USB traffic is sent to the adapter while the SPI slave is armed. Additional USB traffic can extend the required setup time by several microseconds.

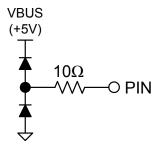

## 4. EQUIVALENT PIN CIRCUITS

All non-USB pins of the USB-910H Adapter except GP3/VDD, SCL and SDA have the following equivalent input circuit:

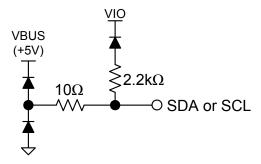

The SDA and SCL pins have the following equivalent input circuit (assuming the built-in  $2.2k\Omega$  pull-up resistors are disabled):

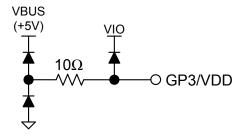

VIO is the programmed Target I/O voltage of the Adapter. The GP3/VDD pin has the following equivalent input circuit, assuming the pin is operating as GP3:

## 5. ADAPTER PINS

The USB-910H Adapter has nine pins plus GND to interface to a target embedded system. These pins provide functions ranging from I2C/SMBus and SPI signaling to general-purpose I/O and power. The following table describes the available pins, their functions, and their position and color-coding on the USB-910H Adapter connector.

Table 1. Adapter Pin-out and Color-coding.

| Pin<br>Name | Connector Pin Number | Connector Wire Color | Function                                                                            |

|-------------|----------------------|----------------------|-------------------------------------------------------------------------------------|

| SCL         | 1                    | BROWN                | Serves as either the clock for I2C/SMBus mode or as a general-purpose I/O.          |

| GND         | 2                    | RED                  | Ground.                                                                             |

| SDA         | 3                    | ORANGE               | Serves as either the data for I2C/SMBus mode or as a general-purpose I/O.           |

| GP3/VDD     | 4                    | YELLOW               | Serves as either VDD to the target or as a general-purpose I/O.                     |

| MISO        | 5                    | GREEN                | Serves as either master-in/slave-out data for SPI mode or as a general-purpose I/O. |

| GP1         | 6                    | BLUE                 | A general-purpose I/O.                                                              |

| SCLK        | 7                    | VIOLET               | Serves as either the clock in SPI mode or as a general-purpose I/O.                 |

| MOSI        | 8                    | GREY                 | Serves as either master-out/slave-in data for SPI mode or as a general-purpose I/O. |

| SS          | 9                    | WHITE                | A general-purpose I/O. Named SS only as a convenience.                              |

| GP2         | 10                   | BLACK                | A general-purpose I/O.                                                              |

Below is a color-coded diagram of a bottom-view of the standard connector for the USB-910H Adapter:

Connector

**Bottom View** GP2 10 SS MOSI 7 **SCLK** GP1 5 MISO GP3 / VDD 3 **SDA GND** 1 SCL

The table below shows the specific capabilities of each Adapter pin (beyond those associated with the I2C/SMBus and SPI interfaces).

Table 2. Adapter Pin Capabilities.

| Pin  | General-Purpose<br>Input | General-Purpose<br>Output | Master Mode<br>Slave-Select | Slave Mode<br>Slave-Select |  |

|------|--------------------------|---------------------------|-----------------------------|----------------------------|--|

| SCLK | •                        | •                         |                             |                            |  |

| MOSI | •                        | •                         |                             |                            |  |

| MISO | •                        | •                         |                             |                            |  |

| SDA  | •                        | •                         | •                           | •                          |  |

| SCL  | •                        | •                         | •                           | •                          |  |

| SS   | •                        | •                         | •                           | •                          |  |

| GP1  | •                        | •                         | •                           | •                          |  |

| GP2  | •                        | •                         | •                           | •                          |  |

| GP3  | •                        | •                         | •                           |                            |  |

## 6. FUNCTIONAL DESCRIPTION

The USB-910H Embedded Systems Interface is a complete solution for providing connectivity between a host PC and a target system. The USB-910H provides this connectivity by converting USB transactions from the PC into I2C, SMBus, SPI, or "bit-banged" general-purpose I/O operations.

The USB-910H Adapter provides the following high-level capabilities:

- I2C/SMBus Master mode.

- I2C/SMBus Slave mode.

- SPI Master mode.

- SPI Slave mode.

- Up to 9 general-purpose I/O.

- I2C/SMBus Pull-up Resistors.

- Target VDD supply from 1.65V to 3.6V, or 5V @ 400mA.

At any given time, the USB-910H Adapter can act as any one of the four serial devices list above (an I2C/SMBus or SPI + Master or Slave), can be used strictly for general-purpose I/O operations, or can be both a serial device and perform "bit-banged" operations using the remaining I/O pins. The I2C Pull-up Resistors can be enabled in any combination with the other features, even if the Adapter is not acting as an I2C device.

All Adapter pins operate using a programmable I/O logic range<sup>1</sup>. This allows the Adapter to communicate with target systems running at a wide range of supply voltages. Regardless of the I/O voltage, all Adapter pins except GP3 can tolerate voltages up to VBUS+0.3V (GP3 is limited to  $V_{IO}$ +0.3V).

### 6.1. I/O Voltage and Powering the Target System

The USB-910H Adapter has the ability to level-shift the interface pins from a programmable I/O voltage to its own internal logic levels. This level-shifting is done using a true high-impedance method – the target system is not required to drive DC current into or out of the adapter pins. The I/O voltage at which the

6

<sup>&</sup>lt;sup>1</sup> The SDA and SCL pins switch to fixed logic levels when in I2C/SMBus mode to accommodate the SMBus standard.

Adapter communicates with the target system is programmable from the host PC with supported values ranging from 1.65V to 3.6V, or 5V (see Section 1 for details).

The programmed I/O voltage sets the value the Adapter uses when driving an interface pin to a logic HIGH. The output drivers are true bi-directional, level-shifting, push-pull drivers. This prevents the target system from sinking high leakage current when driving a low voltage into an Adapter pin. The built-in I2C Pull-up Resistors are also switched to the I/O voltage when enabled.

The USB-910H Adapter can optionally connect the programmed I/O voltage directly to the GP3/VDD interface pin in order to supply power to the target system directly from the host PC. This VDD pin can provide up to 400mA and is both short-circuit and thermal-overload protected.

## 6.2. General-Purpose I/O

Any pin not claimed by an enabled feature of the USB-910 Adapter can be used as a general-purpose input/output signal. The following table shows which capabilities of the USB-910H claim which Adapter pins:

| Adapter<br>Feature | Pins Claimed by the Adapter vs. Feature (not available as general-purpose I/O) |      |      |     |      |    |     |     |     |

|--------------------|--------------------------------------------------------------------------------|------|------|-----|------|----|-----|-----|-----|

|                    | SCLK                                                                           | MOSI | MISO | SDA | SCLK | SS | GP1 | GP2 | GP3 |

| I2C/SMBus Master   |                                                                                |      |      | Х   | Х    |    |     |     |     |

| I2C/SMBus Slave    |                                                                                |      |      | Х   | Х    |    |     |     |     |

| SPI Master         | Х                                                                              | Х    | Х    |     |      |    |     |     |     |

| SPI Slave          | Х                                                                              | Х    | Х    |     |      |    |     |     |     |

| Target VDD         |                                                                                |      |      |     |      |    |     |     | Х   |

Table 3. Adapter Pins Claimed by Features.

For example, when the Adapter is enabled as a SPI Master, the SCLK, MOSI, and MISO pins are not available as general-purpose I/O. Although one Adapter pin is named SS that is strictly for convenience. The SS pin in fact has no special significance. Any pin can be used as a Slave-Select during a SPI Master or SPI Slave operation. As such, it is up to the user to avoid using a chosen Slave-Select pin as a general-purpose I/O.

The USB-910H Adapter provides commands to set, clear, and tri-state any set of general-purpose I/O at any time, even during I2C or SPI operations. In addition, the Adapter allows all pins to be polled regardless of whether they are used by an enabled feature in the Adapter. Finally, both the I2C/SMBus and SPI script languages include commands to drive and poll I/O, allowing a mix of serial operations and I/O operations. For example, a SPI Master script can use I/O commands to handshake with a slave between or during serial transfers.

#### 6.3. I2C / SMBus Modes

The USB-910H Adapter can operate as a fully-compliant I2C / SMBus master or slave device, supporting the following system requirements:

- Complete multi-master compliance.

- 7-bit and 10-bit addressing.

- Programmable SCL rates up to 1.5MHz.

- SMBus compliant setup/hold times.

- Shift data least-significant or most-significant bit first.

- SCL stretching compliance.

- Loss of arbitration detection and optional retry.

- SMBus PEC generation and checking.

- SCL low timeout and recovery.

- SCL high bus-free detection.

- Repeated STARTs.

- Group commands (master and slave).

- Bus fault detection.

- Built-in  $2.2k\Omega$  pull-up resistors to a programmable  $V_{IO}$  (with enables).

- Respond to up to 16 specific addresses or respond to all addresses.

- Generate arbitrary bus faults for use in system testing.

## 6.3.1. I2C/SMBus Master Operations

I2C/SMBus Master operations can be performed using three methods:

- 1. **Quick Write** Perform a bus write to a specific slave device using 7-bit or 10-bit addressing.

- 2. **Quick Read** Perform a bus read from a specific slave device using 7-bit or 10-bit addressing.

- 3. **Execute a Script** Execute a script to perform any combination of configuration, reads, writes, delays, and general-purpose I/O operations.

Most simple data operations can be performed using a Quick Read or Quick Write. Both operations move a block of data to or from a slave device using the normal I2C/SMBus read or write protocol (i.e. a single START + Address + R/W bit + DATA + STOP).

However, the real power of the USB-910H Adapter is found in its ability to execute scripts supporting any combination of bus transactions, delays, and I/O operations. A script is a string of data and simple commands, each representing a low-level action to be performed, much like the list above (e.g. START + Address + R/W ...). The I2C/SMBus master device can execute the following actions:

- Generate a START on the bus.

- Generate a STOP on the bus.

- Transmit a byte on the bus.

- Read a specified number of bytes from the bus.

- Delay a specified number of microseconds.

- Write an automatically-generated PEC byte to the bus.

- Read a PEC byte from the bus and compare to an automatically-generated value.

- Read a byte from the bus and compare to a specified value.

- Reconfigure the I2C Master settings (e.g. whether to retry if arbitration is lost, etc.).

- Drive a specified pin low, high, or to High-Z.

- Wait until a specified pin is high or low (with configurable timeout).

Using this simple script capability, complex protocols can be layered onto the I2C/SMBus bus, including handshaking using available general-purpose I/O.

### 6.3.2. I2C/SMBus Slave Operations

As an I2C/SMBus Slave device, the USB-910H Adapter can either respond to up to 16 specific 7-bit or 10-bit addresses, or can respond to all 7-bit or all 10-bit addresses. The slave device supports both read and write operations. For reads, the user sends the desired outgoing data to the Adapter prior to "arming" it as a slave. If a bus master attempts to read more data than provided by the user, the slave continues to transmit an internally-calculated PEC byte until a STOP is received. While addressed, the USB-910H stores all incoming data, including the address bytes, in its internal buffers. This allows the host PC to retrieve both the addresses and write data after the bus operation completes.

The USB-910H supports the PMBus Group Command Protocol. This protocol allows multiple devices to be addressed in the same operation, i.e. by using repeated STARTs. For example, consider the following bus operation:

This group operation writes 0x55 to device 0x10 (right-justified), 0xAA to device 0x20 and 0x5A to device 0x40. The USB-910H supports such protocols and will operate correctly as any of the addressed devices.

#### 6.4. SPI Modes

The USB-910H Adapter can operate as a full-featured master or slave device compatible with SPI, MICROWIRE, and most other three-wire and four-wire synchronous serial interfaces. The following system requirements are supported:

- SCLK rates up to 24MHz.

- Active-high or active-low Slave-Selects.

- Shift data least-significant or most-significant bit first.

- Supports all standard "modes".

- · Clock data on leading or trailing edge.

- Idle with SCLK high or low.

- Transfer a configurable number of bytes per Slave-Select assertion.

- Up to 6 different Slave-Select pins available.

- Programmable Slave-Select setup/hold timing.

- Slave-Select pin can tri-state the MISO output to support multiple slaves.

- Operate with no Slave-Select (single-slave mode).

## 6.4.1. SPI Master Operations

SPI Master operations can be performed using two methods:

- 1. **Quick Transfer** Perform a bus transfer using a specific Slave-Select pin.

- 2. **Execute a Script** Execute a script to perform any combination of configurations, transfers, delays, and general-purpose I/O operations.

Most simple data transfers can be performed using a Quick Transfer. This operation transfers a block of data of a given size between the master and a slave using a single Slave-Select pin (or no Slave-Select pin). The number of bytes the master transfers each time it asserts the Slave-Select pin can be configured from 1 to 65536.

However, similar to I2C/SMBus mode, the SPI Master can execute scripts supporting any combination of configurations, bus transfers, delays, and I/O operations. The SPI Master device can execute the following actions:

- Transfer a byte on the bus.

- Transfer (i.e. repeat) a byte a given number of times.

- Delay a specified number of microseconds.

- Expect a specific byte from the slave.

- Reconfigure the SPI Master settings (e.g. change the Slave-Select, etc.).

- Drive a specific pin low, high, or to High-Z.

- Wait until a specific pin is high or low (with configurable timeout).

Using this simple script capability, complex protocols can be layered onto the SPI bus, including handshaking using available general-purpose I/O, communicating with multiple slaves, etc.

### 6.4.2. SPI Slave Operations

As a SPI Slave device, the USB-910H Adapter can be configured to respond to any one of 5 Slave-Select pins and can be configured to activate if that pin asserts either high or low. In addition, a slave device can operate with no Slave-Select – it will transfer data on all SCLK cycles.

Like a SPI Master, a slave device can transfer data either LSB or MSB first, and can support all standard SPI clocking modes. Slave operations are initiated by sending the desired outgoing data to the Adapter, then sending a command which "arms" the slave, causing it to start watching for its Slave-Select pin to assert. The slave will remain armed until its Slave-Select asserts and de-asserts (if it has a Slave-Select pin) or until it has transferred all outgoing data (if it has no Slave-Select pin). If a slave has a Slave-Select pin and a master requests more data than available in its outgoing buffer, the slave will enter loopback mode in which it transmits its incoming data back to the master. Once the slave disarms, the incoming data can be retrieved from the device and the next operation can be initiated by the host PC.

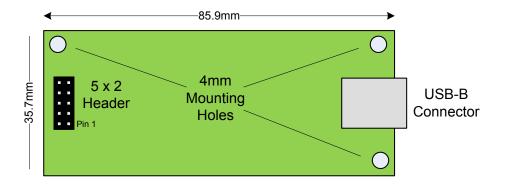

# 7. IN SYSTEM MOUNTING

Although generally the USB-910 Adapter will be used in its factory enclosure and connected to a target system via a ribbon connector or break-out cable, the Adapter PCB is equipped to be mounted directly into a target system when appropriate. The diagram below shows a simplified top-view of the Adapter PCB layout. For more information, contact Keterex at <a href="mailto:support@keterex.com">support@keterex.com</a>.

## **Contact Information**

Keterex, Inc.

7320 N. Mo Pac Expressway

Suite 201

Austin, Texas 78731

Tel: 512-346-8800

www.keterex.com

Email: support@keterex.com

Information furnished by Keterex, Inc. in this document is believed to be accurate and reliable. However, no responsibility is assumed for its use. Information in this document is subject to change without notice.

**Trademarks:** The Keterex name and logo are registered trademarks of Keterex Incorporated. Other products or brand names mentioned herein are trademarks or registered trademarks of their respective holders.

**Use in life support systems:** Keterex devices are not designed for use in life support and/or safety equipment where malfunction of the product can result in personal injury or death. Your use or sale of these devices for use in life support and/or safety applications is at your own risk. You agree to defend and hold us harmless from any and all damages, claims, suits or expenses resulting from such use.

Limitation of Liability: You acknowledge and agree that, in no event, shall Keterex be liable, whether in contract, warranty, tort (including negligence or breach of statutory duty), strict liability, indemnity, contribution, or otherwise, for any indirect, special, punitive, exemplary, incidental or consequential loss, damage, cost or expense of any kind whatsoever, howsoever caused, or for any loss of production, cost of procurement of substitute goods, loss of capital, loss of software, loss of profit, loss of revenues, contracts, business, cost of rework, loss of goodwill or anticipated savings, or wasted management time, even if Keterex has been advised of the possibility or they are foreseeable. The total liability of Keterex on all claims, whether in contract, warranty, tort (including negligence or breach of statutory duty), strict liability, indemnity, contribution, or otherwise, shall not exceed the purchase price of these devices.

Компания «Океан Электроники» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Поставка оригинальных импортных электронных компонентов напрямую с производств Америки, Европы и Азии, а так же с крупнейших складов мира;

- Широкая линейка поставок активных и пассивных импортных электронных компонентов (более 30 млн. наименований);

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Помощь Конструкторского Отдела и консультации квалифицированных инженеров;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Поставка электронных компонентов под контролем ВП;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- При необходимости вся продукция военного и аэрокосмического назначения проходит испытания и сертификацию в лаборатории (по согласованию с заказчиком);

- Поставка специализированных компонентов военного и аэрокосмического уровня качества (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Actel, Aeroflex, Peregrine, VPT, Syfer, Eurofarad, Texas Instruments, MS Kennedy, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Компания «Океан Электроники» является официальным дистрибьютором и эксклюзивным представителем в России одного из крупнейших производителей разъемов военного и аэрокосмического назначения «JONHON», а так же официальным дистрибьютором и эксклюзивным представителем в России производителя высокотехнологичных и надежных решений для передачи СВЧ сигналов «FORSTAR».

**«JONHON»** (основан в 1970 г.)

Разъемы специального, военного и аэрокосмического назначения:

(Применяются в военной, авиационной, аэрокосмической, морской, железнодорожной, горно- и нефтедобывающей отраслях промышленности)

«**FORSTAR**» (основан в 1998 г.)

ВЧ соединители, коаксиальные кабели, кабельные сборки и микроволновые компоненты:

(Применяются в телекоммуникациях гражданского и специального назначения, в средствах связи, РЛС, а так же военной, авиационной и аэрокосмической отраслях промышленности).

Телефон: 8 (812) 309-75-97 (многоканальный)

Факс: 8 (812) 320-03-32

Электронная почта: ocean@oceanchips.ru

Web: http://oceanchips.ru/

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, д. 2, корп. 4, лит. А