# Variable Resolution, 10-Bit to 16-Bit R/D Converter with Reference Oscillator

# AD2S1210

#### FEATURES

Complete monolithic resolver-to-digital converter 3125 rps maximum tracking rate (10-bit resolution) ±2.5 arc minutes of accuracy 10-/12-/14-/16-bit resolution, set by user Parallel and serial 10-bit to 16-bit data ports Absolute position and velocity outputs System fault detection Programmable fault detection thresholds Differential inputs Incremental encoder emulation Programmable sinusoidal oscillator on-board Compatible with DSP and SPI interface standards 5 V supply with 2.3 V to 5 V logic interface -40°C to +125°C temperature rating

#### **APPLICATIONS**

DC and ac servo motor control Encoder emulation Electric power steering Electric vehicles Integrated starter generators/alternators Automotive motion sensing and control

#### **GENERAL DESCRIPTION**

The AD2S1210 is a complete 10-bit to 16-bit resolution tracking resolver-to-digital converter, integrating an on-board programmable sinusoidal oscillator that provides sine wave excitation for resolvers.

The converter accepts  $3.15 \text{ V} \text{ p-p} \pm 27\%$  input signals, in the range of 2 kHz to 20 kHz on the sine and cosine inputs. A Type II servo loop is employed to track the inputs and convert the input sine and cosine information into a digital representation of the input angle and velocity. The maximum tracking rate is 3125 rps.

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

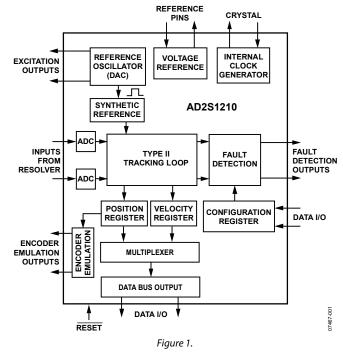

#### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT HIGHLIGHTS**

- 1. Ratiometric tracking conversion. The Type II tracking loop provides continuous output position data without conversion delay. It also provides noise immunity and tolerance of harmonic distortion on the reference and input signals.

- 2. System fault detection. A fault detection circuit can sense loss of resolver signals, out-of-range input signals, input signal mismatch, or loss of position tracking. The fault detection threshold levels can be individually programmed by the user for optimization within a particular application.

- 3. Input signal range. The sine and cosine inputs can accept differential input voltages of 3.15 V p-p ± 27%.

- 4. Programmable excitation frequency. Excitation frequency is easily programmable to a number of standard frequencies between 2 kHz and 20 kHz.

- Triple format position data. Absolute 10-bit to 16-bit angular position data is accessed via either a 16-bit parallel port or a 4-wire serial interface. Incremental encoder emulation is in standard A-quad-B format with direction output available.

- 6. Digital velocity output. 10-bit to 16-bit signed digital velocity accessed via either a 16-bit parallel port or a 4-wire serial interface.

### TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| Functional Block Diagram 1                  |

| General Description 1                       |

| Product Highlights 1                        |

| Revision History 2                          |

| Specifications                              |

| Timing Specifications 6                     |

| Absolute Maximum Ratings                    |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics11       |

| Resolver Format Signals15                   |

| Theory of Operation                         |

| Resolver to Digital Conversion16            |

| Fault Detection Circuit16                   |

| On-Board Programmable Sinusoidal Oscillator |

| Synthetic Reference Generation              |

| Configuration of AD2S1210 20                |

| Modes of Operation                          |

| Register Map21                              |

| Position Register                           |

| Velocity Register                           |

#### **REVISION HISTORY**

| 2/10—Rev. 0 to Rev. A                                     |      |

|-----------------------------------------------------------|------|

| Changes to Typical Performance Characteristics Section11, | 12   |

| Changes to Ordering Guide                                 | . 34 |

8/08—Revision 0: Initial Version

|   | LOS Threshold Register                              | . 21 |

|---|-----------------------------------------------------|------|

|   | DOS Overrange Threshold Register                    | . 21 |

|   | DOS Mismatch Threshold Register                     | . 21 |

|   | DOS Reset Maximum and Minimum Threshold Registers . | . 22 |

|   | LOT High Threshold Register                         | . 22 |

|   | LOT Low Threshold Register                          | . 22 |

|   | Excitation Frequency Register                       | . 22 |

|   | Control Register                                    | . 22 |

|   | Software Reset Register                             | . 23 |

|   | Fault Register                                      | . 23 |

| D | igital interface                                    | . 24 |

|   | SOE Input                                           | . 24 |

|   | SAMPLE Input                                        | . 24 |

|   | Data Format                                         | . 24 |

|   | Parallel Interface                                  | . 24 |

|   | Serial Interface                                    | . 28 |

|   | Incremental Encoder Outputs                         | . 31 |

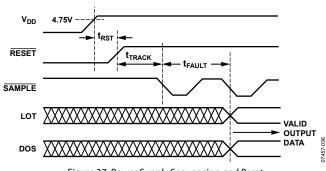

|   | Supply Sequencing and Reset                         | . 31 |

| С | ircuit Dynamics                                     | . 32 |

|   | Loop Response Model                                 | . 32 |

|   | Sources of Error                                    | . 33 |

| О | outline Dimensions                                  | . 34 |

|   | Ordering Guide                                      | . 34 |

### **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 5.0 V \pm 5\%$ , CLKIN = 8.192 MHz ± 25%, EXC, EXC frequency = 10 kHz to 20 kHz (10-bit); 6 kHz to 20 kHz (12-bit); 3 kHz to 12 kHz (14-bit); 2 kHz to 10 kHz (16-bit); T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>; unless otherwise noted.<sup>1</sup>

| Parameter                        | Min  | Тур            | Max         | Unit      | Conditions/Comments                                           |

|----------------------------------|------|----------------|-------------|-----------|---------------------------------------------------------------|

| SINE, COSINE INPUTS <sup>2</sup> |      |                |             |           |                                                               |

| Voltage Amplitude                | 2.3  | 3.15           | 4.0         | V р-р     | Sinusoidal waveforms, differential SIN to SINLO, COS to COSLO |

| Input Bias Current               |      |                | 8.25        | μA        | V <sub>IN</sub> = 4.0 V p-p, CLKIN = 8.192 MHz                |

| Input Impedance                  | 485  |                |             | kΩ        | V <sub>IN</sub> = 4.0 V p-p, CLKIN = 8.192 MHz                |

| Phase Lock Range                 | -44  |                | +44         | Degrees   | Sine/cosine vs. EXC output, Control Register D3 =             |

| Common-Mode Rejection            |      | ±20            |             | arc sec/V | 10 Hz to 1 MHz, Control Register D4 = 0                       |

| ANGULAR ACCURACY <sup>3</sup>    |      |                |             |           |                                                               |

| Angular Accuracy                 |      | ±2.5 + 1 LSB   | ±5 + 1 LSB  | arc min   | B, D grades                                                   |

|                                  |      | ±5 + 1 LSB     | ±10 + 1 LSB | arc min   | A, C grades                                                   |

| Resolution                       |      | 10, 12, 14, 16 |             | Bits      | No missing codes                                              |

| Linearity INL                    |      |                |             |           |                                                               |

| 10-bit                           |      |                | ±1          | LSB       | B, D grades                                                   |

|                                  |      |                | ±2          | LSB       | A, C grades                                                   |

| 12-bit                           |      |                | ±2          | LSB       | B, D grades                                                   |

|                                  |      |                | ±4          | LSB       | A, C grades                                                   |

| 14-bit                           |      |                | ±4          | LSB       | B, D grades                                                   |

|                                  |      |                | ±8          | LSB       | A, C grades                                                   |

| 16-bit                           |      |                | ±16         | LSB       | B, D grades                                                   |

|                                  |      |                | ±32         | LSB       | A, C grades                                                   |

| Linearity DNL                    |      |                | ±0.9        | LSB       |                                                               |

| Repeatability                    |      | ±1             |             | LSB       |                                                               |

| VELOCITY OUTPUT                  |      |                |             |           |                                                               |

| Velocity Accuracy <sup>4</sup>   |      |                |             |           |                                                               |

| 10-bit                           |      |                | ±2          | LSB       | B, D grades, zero acceleration                                |

|                                  |      |                | ±4          | LSB       | A, C grades, zero acceleration                                |

| 12-bit                           |      |                | ±2          | LSB       | B, D grades, zero acceleration                                |

|                                  |      |                | ±4          | LSB       | A, C grades, zero acceleration                                |

| 14-bit                           |      |                | ±4          | LSB       | B, D grades, zero acceleration                                |

|                                  |      |                | ±8          | LSB       | A, C grades, zero acceleration                                |

| 16-bit                           |      |                | ±16         | LSB       | B, D grades, zero acceleration                                |

|                                  |      |                | ±32         | LSB       | A, C grades, zero acceleration                                |

| <b>Resolution</b> <sup>5</sup>   |      | 9, 11, 13, 15  |             | Bits      |                                                               |

| DYNAMNIC PERFORMANCE             |      |                |             |           |                                                               |

| Bandwidth                        |      |                |             |           |                                                               |

| 10-bit                           | 2000 |                | 6500        | Hz        |                                                               |

|                                  | 2900 |                | 5300        | Hz        | CLKIN = 8.192 MHz                                             |

| 12-bit                           | 900  |                | 2800        | Hz        |                                                               |

|                                  | 1200 |                | 2200        | Hz        | CLKIN = 8.192 MHz                                             |

| 14-bit                           | 400  |                | 1500        | Hz        |                                                               |

|                                  | 600  |                | 1200        | Hz        | CLKIN = 8.192 MHz                                             |

| 16-bit                           | 100  |                | 350         | Hz        |                                                               |

|                                  | 125  |                | 275         | Hz        | CLKIN = 8.192 MHz                                             |

| Parameter                                                                              | Min        | Тур         | Мах    | Unit    | Conditions/Comments                                                           |

|----------------------------------------------------------------------------------------|------------|-------------|--------|---------|-------------------------------------------------------------------------------|

| Tracking Rate                                                                          |            |             |        |         |                                                                               |

| 10-bit                                                                                 |            |             | 3125   | rps     | CLKIN = 10.24 MHz                                                             |

|                                                                                        |            |             | 2500   |         | CLKIN = 8.192 MHz                                                             |

| 12-bit                                                                                 |            |             | 1250   | rps     | CLKIN = 10.24 MHz                                                             |

|                                                                                        |            |             | 1000   |         | CLKIN = 8.192 MHz                                                             |

| 14-bit                                                                                 |            |             | 625    | rps     | CLKIN = 10.24 MHz                                                             |

|                                                                                        |            |             | 500    |         | CLKIN = 8.192 MHz                                                             |

| 16-bit                                                                                 |            |             | 156.25 | rps     | CLKIN = 10.24 MHz                                                             |

|                                                                                        |            |             | 125    | 1       | CLKIN = 8.192 MHz                                                             |

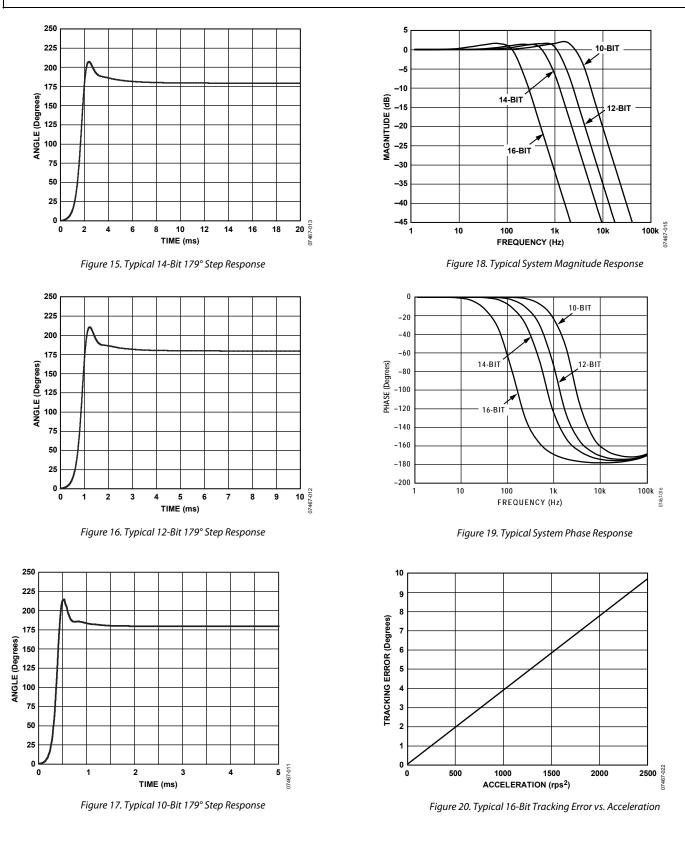

| Acceleration Error                                                                     |            |             |        |         |                                                                               |

| 10-bit                                                                                 |            | 30          |        | arc min | At 50,000 rps <sup>2</sup> , CLKIN = 8.192 MHz                                |

| 12-bit                                                                                 |            | 30          |        | arc min | At 10,000 rps <sup>2</sup> , CLKIN = 8.192 MHz                                |

| 14-bit                                                                                 |            | 30          |        | arc min | At 2500 rps <sup>2</sup> , CLKIN = $8.192$ MHz                                |

| 16-bit                                                                                 |            | 30          |        | arc min | At 125 $rps^2$ , CLKIN = 8.192 MHz                                            |

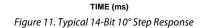

| Settling Time 10° Step Input                                                           |            | 50          |        | aremin  | At 125 1p3 ; CERIN = 0.152 MI12                                               |

| 10-bit                                                                                 |            | 0.6         | 0.9    | ms      | To settle to within $\pm 2$ LSB , CLKIN = 8.192 MHz                           |

| 12-bit                                                                                 |            | 2.2         | 3.1    | ms      | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                            |

| 12-bit                                                                                 |            | 2.2<br>6.5  |        |         |                                                                               |

| 14-bit                                                                                 |            | 0.5<br>27.5 | 9.0    | ms      | To settle to within $\pm 2 \text{ LSB}$ , CLKIN = 8.192 MHz                   |

|                                                                                        |            | 27.5        | 40     | ms      | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                            |

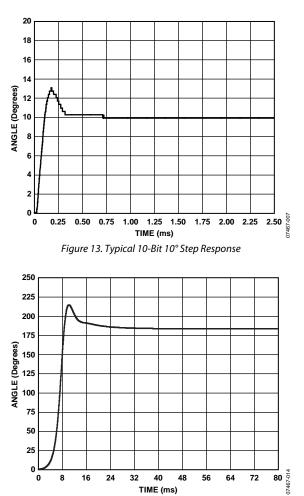

| Settling Time 179° Step Input                                                          |            | 1 5         | 2.2    |         |                                                                               |

| 10-bit                                                                                 |            | 1.5         | 2.2    | ms      | To settle to within $\pm 2$ LSB , CLKIN = 8.192 MHz                           |

| 12-bit                                                                                 |            | 4.75        | 6.0    | ms      | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                            |

| 14-bit                                                                                 |            | 10.5        | 14.7   | ms      | To settle to within $\pm 2$ LSB , CLKIN = 8.192 MHz                           |

| 16-bit                                                                                 |            | 45          | 66     | ms      | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                            |

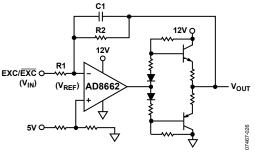

| EXC, EXC OUTPUTS                                                                       |            |             |        |         |                                                                               |

| Voltage                                                                                | 3.2        | 3.6         | 4.0    | V р-р   | Load $\pm 100 \mu$ A, typical differential output<br>(EXC to EXC) = 7.2 V p-p |

| Center Voltage                                                                         | 2.40       | 2.47        | 2.53   | V       |                                                                               |

| Frequency                                                                              | 2          |             | 20     | kHz     |                                                                               |

| EXC/EXC DC Mismatch                                                                    |            |             | 30     | mV      |                                                                               |

| EXC/EXC AC Mismatch                                                                    |            |             | 100    | mV      |                                                                               |

| THD                                                                                    |            | -58         |        | dB      | First five harmonics                                                          |

| VOLTAGE REFERENCE                                                                      |            |             |        |         |                                                                               |

| REFOUT                                                                                 | 2.40       | 2.47        | 2.53   | v       | ±Ι <sub>ουτ</sub> = 100 μΑ                                                    |

| Drift                                                                                  | 2.10       | 100         | 2.55   | ppm/°C  |                                                                               |

| PSRR                                                                                   |            | -60         |        | dB      |                                                                               |

|                                                                                        | -          | -00         |        | ab      |                                                                               |

| V <sub>IL</sub> Voltage Input Low                                                      |            |             | 0.8    | v       |                                                                               |

| Vill Voltage Input Low<br>Vill Voltage Input High                                      | 2.0        |             | 0.8    | V       |                                                                               |

|                                                                                        | 2.0        |             |        | v       |                                                                               |

| LOGIC INPUTS                                                                           |            |             | 0.0    | N       |                                                                               |

| V <sub>IL</sub> Voltage Input Low                                                      |            |             | 0.8    | V       | $V_{DRIVE} = 2.7 V \text{ to } 5.25 V$                                        |

|                                                                                        |            |             | 0.7    | V       | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                 |

| V <sub>⊮</sub> Voltage Input High                                                      | 2.0        |             |        | V       | $V_{DRIVE} = 2.7 V \text{ to } 5.25 V$                                        |

|                                                                                        | 1.7        |             |        | V       | $V_{DRIVE} = 2.3 V \text{ to } 2.7 V$                                         |

| I <sub>L</sub> Low Level Input Current (Non<br>Pull-Up)                                |            |             | 10     | μΑ      |                                                                               |

| I <sub>IL</sub> Low Level Input Current (Pull-Up)                                      |            |             | 80     | μA      | RES0, RES1, RD, WR/FSYNC, A0, A1, and RESET pins                              |

| l⊪ High Level Input Current                                                            | -10        |             |        | μA      |                                                                               |

| LOGIC OUTPUTS                                                                          | 1          |             |        |         |                                                                               |

| V <sub>oL</sub> Voltage Output Low                                                     |            |             | 0.4    | v       | $V_{DRIVE} = 2.3 V \text{ to } 5.25 V$                                        |

|                                                                                        | 2.4        |             |        | v       | $V_{\text{DRIVE}} = 2.7 \text{ V to } 5.25 \text{ V}$                         |

| Vollage Output High                                                                    |            |             |        |         | Dinte In to died t                                                            |

| $V_{OH}$ Voltage Output High                                                           | 2.0        |             |        | V       | $V_{DRME} = 2.3 V to 2.7 V$                                                   |

| V <sub>OH</sub> Voltage Output High<br>I <sub>оzн</sub> High Level Three-State Leakage | 2.0<br>-10 |             |        | V<br>μA | $V_{\text{DRIVE}} = 2.3 \text{ V to } 2.7 \text{ V}$                          |

| Parameter          | Min  | Тур | Мах  | Unit | Conditions/Comments |

|--------------------|------|-----|------|------|---------------------|

| POWER REQUIREMENTS |      |     |      |      |                     |

| AVDD               | 4.75 |     | 5.25 | V    |                     |

|                    | 4.75 |     | 5.25 | V    |                     |

| VDRIVE             | 2.3  |     | 5.25 | V    |                     |

| POWER SUPPLY       |      |     |      |      |                     |

| lavdd              |      |     | 12   | mA   |                     |

| I <sub>DVDD</sub>  |      |     | 35   | mA   |                     |

| I <sub>OVDD</sub>  |      |     | 2    | mA   |                     |

<sup>1</sup> Temperature ranges are as follows: A, B grades: -40°C to +85°C; C, D grades: -40°C to +125°C.

<sup>2</sup> The voltages, SINLO, COS, and COSLO, relative to AGND, must always be between 0.15 V and  $AV_{DD} - 0.2$  V. <sup>3</sup> All specifications within the angular accuracy parameter are tested at constant velocity, that is, zero acceleration. <sup>4</sup> The velocity accuracy specification includes velocity offset and dynamic ripple.

<sup>5</sup> For example when RES0 = 0 and RES1 = 1, the position output has a resolution of 12 bits. The velocity output has a resolution of 11 bits with the MSB indicating the direction of rotation. In this example, with a CLKIN frequency of 8.192 MHz the velocity LSB is 0.488 rps, that is, 1000 rps/(211).

<sup>6</sup> The clock frequency of the AD2S1210 can be supplied with a crystal, an oscillator, or directly from a DSP/microprocessor digital output. When using a single-ended clock signal directly from the DSP/microprocessor, the XTALOUT pin should remain open circuit and the logic levels outlined under the logic inputs parameter in Table 1 apply.

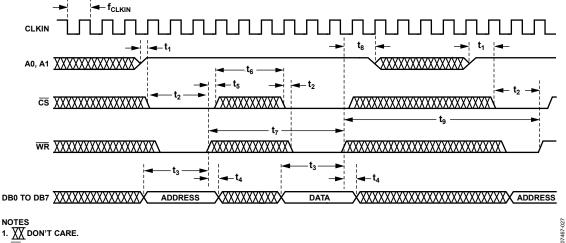

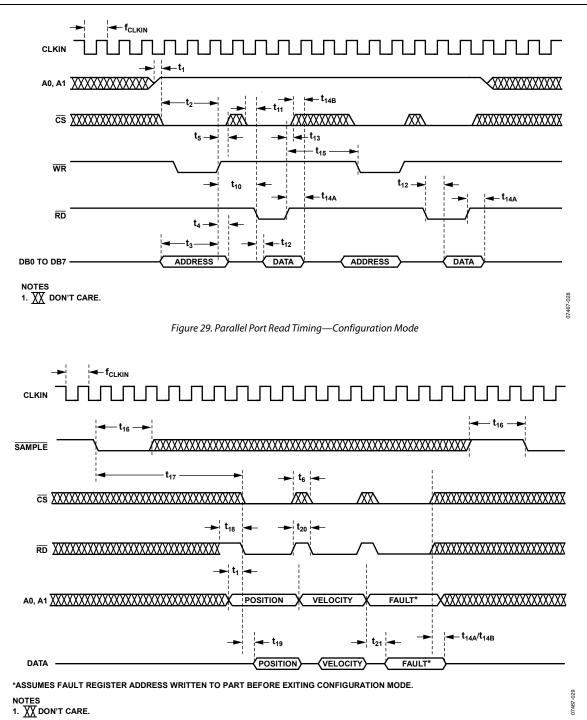

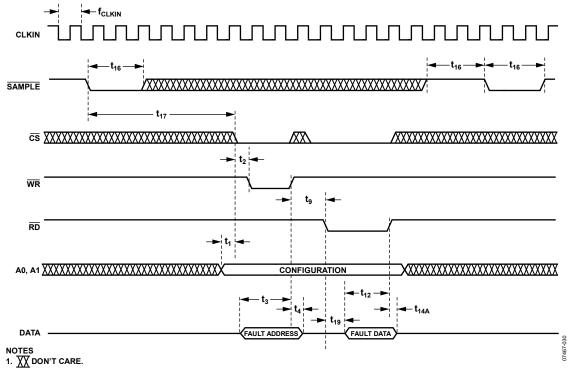

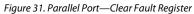

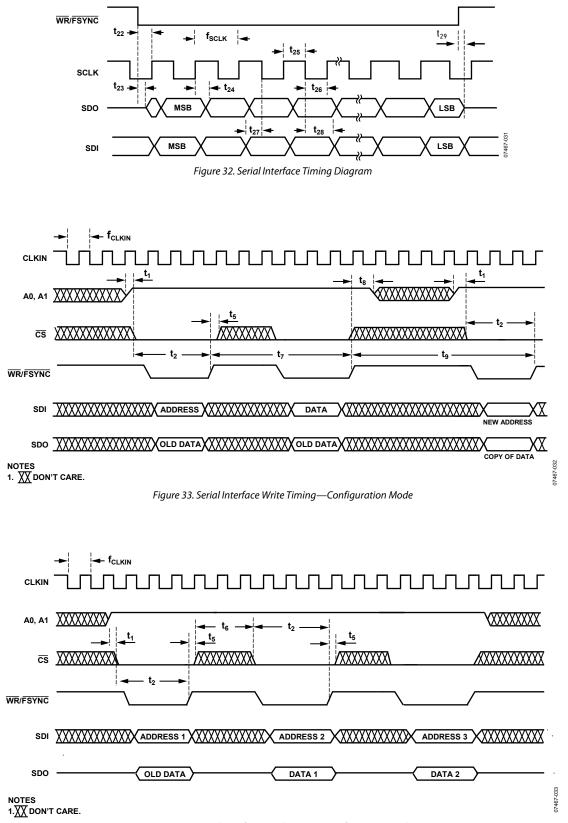

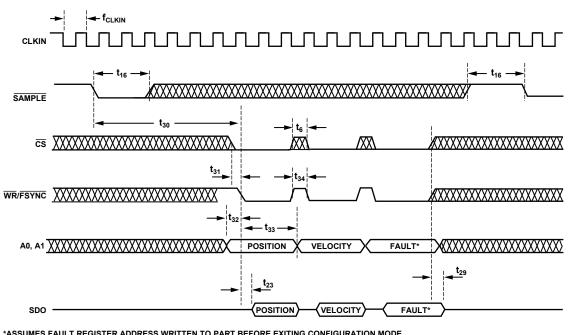

#### TIMING SPECIFICATIONS

$AV_{\rm DD}$  =  $DV_{\rm DD}$  = 5.0 V  $\pm$  5%,  $T_{\rm A}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX,}$  unless otherwise noted.  $^{\rm 1}$

#### Table 2.

| Parameter              | Description                                                                                                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    |

|------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|

| fclkin                 | Frequency of clock input                                                                                      | 6.144                                        | MHz min |

|                        |                                                                                                               | 10.24                                        | MHz max |

| tск                    | Clock period ( = $1/f_{CLKIN}$ )                                                                              | 98                                           | ns min  |

|                        |                                                                                                               | 163                                          | ns max  |

| tı                     | A0 and A1 setup time before $\overline{RD}/\overline{CS}$ low                                                 | 2                                            | ns min  |

| t <sub>2</sub>         | Delay CS falling edge to WR/FSYNC rising edge                                                                 | 22                                           | ns min  |

| t3                     | Address/data setup time during a write cycle                                                                  | 3                                            | ns min  |

| t4                     | Address/data hold time during a write cycle                                                                   | 2                                            | ns min  |

| 15                     | Delay $\overline{WR}/\overline{FSYNC}$ rising edge to $\overline{CS}$ rising edge                             | 2                                            | ns min  |

| t <sub>6</sub>         | Delay $\overline{CS}$ rising edge to $\overline{CS}$ falling edge                                             | 10                                           | ns min  |

| t <sub>7</sub>         | Delay between writing address and writing data                                                                | 2 × t <sub>CK</sub> + 20                     | ns min  |

| t <sub>8</sub>         | A0 and A1 hold time after WR/FSYNC rising edge                                                                | 2                                            | ns min  |

| t9                     | Delay between successive write cycles                                                                         | 6 × t <sub>ск</sub> + 20                     | ns min  |

| 10                     | Delay between rising edge of $\overline{WR}/\overline{FSYNC}$ and falling edge of $\overline{RD}$             | 2                                            | ns min  |

| L11                    | Delay $\overline{CS}$ falling edge to $\overline{RD}$ falling edge                                            | 2                                            | ns min  |

| t <sub>12</sub>        | Enable delay RD low to data valid in configuration mode                                                       |                                              |         |

| <b>C</b> 12            | $V_{\text{DRIVE}} = 4.5 \text{ V to } 5.25 \text{ V}$                                                         | 37                                           | ns min  |

|                        | $V_{\text{DRIVE}} = 4.5 \text{ V to } 3.25 \text{ V}$<br>$V_{\text{DRIVE}} = 2.7 \text{ V to } 3.6 \text{ V}$ | 25                                           | ns min  |

|                        | $V_{\text{DRIVE}} = 2.3 \text{ V to } 3.6 \text{ V}$ $V_{\text{DRIVE}} = 2.3 \text{ V to } 2.7 \text{ V}$     | 30                                           | ns min  |

| t <sub>13</sub>        | $\overrightarrow{RD}$ rising edge to $\overrightarrow{CS}$ rising edge                                        | 2                                            | ns min  |

|                        | Disable delay RD high to data high-Z                                                                          | 16                                           | ns min  |

| t <sub>14A</sub>       | Disable delay $\overline{\text{CS}}$ high to data high-Z                                                      | 16                                           |         |

| t <sub>14B</sub>       |                                                                                                               |                                              | ns min  |

| t <sub>15</sub>        | Delay between rising edge of RD and falling edge of WR/FSYNC                                                  | 2                                            | ns min  |

| t <sub>16</sub>        | SAMPLE pulse width                                                                                            | 2 × t <sub>CK</sub> + 20                     | ns min  |

| t <sub>17</sub>        | Delay from SAMPLE before RD/CS low                                                                            | 6 × t <sub>CK</sub> + 20                     | ns min  |

| <b>t</b> <sub>18</sub> | Hold time RD before RD low                                                                                    | 2                                            | ns min  |

| t <sub>19</sub>        | Enable delay RD/CS low to data valid                                                                          |                                              |         |

|                        | $V_{DRIVE} = 4.5 V \text{ to } 5.25 V$                                                                        | 17                                           | ns min  |

|                        | $V_{\text{DRIVE}} = 2.7 \text{ V to } 3.6 \text{ V}$                                                          | 21                                           | ns min  |

|                        | $V_{DRIVE} = 2.3 V \text{ to } 2.7 V$                                                                         | 33                                           | ns min  |

| t <sub>20</sub>        | RD pulse width                                                                                                | 6                                            | ns min  |

| t <sub>21</sub>        | A0 and A1 set time to data valid when $\overline{RD}/\overline{CS}$ low                                       |                                              |         |

|                        | $V_{DRIVE} = 4.5 V \text{ to } 5.25 V$                                                                        | 36                                           | ns min  |

|                        | $V_{DRIVE} = 2.7 V \text{ to } 3.6 V$                                                                         | 37                                           | ns min  |

|                        | $V_{DRIVE} = 2.3 V \text{ to } 2.7 V$                                                                         | 29                                           | ns min  |

| t <sub>22</sub>        | Delay WR/FSYNC falling edge to SCLK rising edge                                                               | 3                                            | ns min  |

| t <sub>23</sub>        | Delay WR/FSYNC falling edge to SDO release from high-Z                                                        |                                              |         |

|                        | $V_{DRIVE} = 4.5 V \text{ to } 5.25 V$                                                                        | 16                                           | ns min  |

|                        | $V_{DRIVE} = 2.7 V \text{ to } 3.6 V$                                                                         | 26                                           | ns min  |

|                        | $V_{DRIVE} = 2.3 V \text{ to } 2.7 V$                                                                         | 29                                           | ns min  |

| t <sub>24</sub>        | Delay SCLK rising edge to DBx valid                                                                           |                                              |         |

|                        | $V_{DRIVE} = 4.5 V \text{ to } 5.25 V$                                                                        | 24                                           | ns min  |

|                        | V <sub>DRIVE</sub> = 2.7 V to 3.6 V                                                                           | 18                                           | ns min  |

|                        | V <sub>DRIVE</sub> = 2.3 V to 2.7 V                                                                           | 32                                           | ns min  |

| t <sub>25</sub>        | SCLK high time                                                                                                | $0.4 \times t_{SCLK}$                        | ns min  |

| t <sub>26</sub>        | SCLK low time                                                                                                 | $0.4 \times t_{SCLK}$                        | ns min  |

| t <sub>27</sub>        | SDI setup time prior to SCLK falling edge                                                                     | 3                                            | ns min  |

| t <sub>28</sub>        | SDI hold time after SCLK falling edge                                                                         | 2                                            | ns min  |

| Parameter              | Description                                                                                        | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   |

|------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|--------|

| t <sub>29</sub>        | Delay WR/FSYNC rising edge to SDO high-Z                                                           | 15                                           | ns min |

| t <sub>30</sub>        | Delay from SAMPLE before WR/FSYNC falling edge                                                     | 6 × t <sub>ск</sub> + 20 ns                  | ns min |

| <b>t</b> <sub>31</sub> | Delay $\overline{CS}$ falling edge to $\overline{WR}/\overline{FSYNC}$ falling edge in normal mode | 2                                            | ns min |

| t <sub>32</sub>        | A0 and A1 setup time before WR/FSYNC falling edge                                                  | 2                                            | ns min |

| t <sub>33</sub>        | A0 and A1 hold time after WR/FSYNC falling edge <sup>2</sup>                                       |                                              |        |

|                        | In normal mode, $A0 = 0$ , $A1 = 0/1$                                                              | $24 \times t_{CK} + 5$ ns                    | ns min |

|                        | In configuration mode, $A0 = 1$ , $A1 = 1$                                                         | 8 × t <sub>CK</sub> + 5 ns                   | ns min |

| t <sub>34</sub>        | Delay WR/FSYNC rising edge to WR/FSYNC falling edge                                                | 10                                           | ns min |

| f <sub>sclk</sub>      | Frequency of SCLK input                                                                            |                                              |        |

|                        | $V_{DRIVE} = 4.5 V \text{ to } 5.25 V$                                                             | 20                                           | MHz    |

|                        | $V_{DRIVE} = 2.7 V \text{ to } 3.6 V$                                                              | 25                                           | MHz    |

|                        | $V_{DRIVE} = 2.3 V \text{ to } 2.7 V$                                                              | 15                                           | MHz    |

<sup>1</sup> Temperature ranges are as follows: A, B grades: -40°C to +85°C; C, D grades: -40°C to +125°C. <sup>2</sup> A0 and A1 should remain constant for the duration of the serial readback. This may require 24 clock periods to read back the 8-bit fault information in addition to the 16 bits of position/velocity data. If the fault information is not required, A0/A1 may be released following 16 clock cycles.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                             | Rating                                       |

|-------------------------------------------------------|----------------------------------------------|

| AV <sub>DD</sub> to AGND, DGND                        | –0.3 V to +7.0 V                             |

| DV <sub>DD</sub> to AGND, DGND                        | –0.3 V to +7.0 V                             |

| V <sub>DRIVE</sub> to AGND, DGND                      | -0.3 V to AV <sub>DD</sub>                   |

| AV <sub>DD</sub> to DV <sub>DD</sub>                  | –0.3 V to +0.3 V                             |

| AGND to DGND                                          | –0.3 V to +0.3 V                             |

| Analog Input Voltage to AGND                          | $-0.3$ V to AV_{\mbox{\scriptsize DD}}+0.3 V |

| Digital Input Voltage to DGND                         | $-0.3$ V to $V_{\text{DRIVE}}$ + 0.3 V       |

| Digital Output Voltage to DGND                        | $-0.3$ V to $V_{\text{DRIVE}}$ + 0.3 V       |

| Analog Output Voltage Swing                           | $-0.3$ V to AV_{\mbox{\scriptsize DD}}+0.3 V |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                       |

| Operating Temperature Range (Ambient)                 |                                              |

| A, B Grades                                           | -40°C to +85°C                               |

| C, D Grades                                           | -40°C to +125°C                              |

| Storage Temperature Range                             | –65°C to +150°C                              |

| $\theta_{JA}$ Thermal Impedance <sup>2</sup>          | 54°C/W                                       |

| θ <sub>JA</sub> Thermal Impedance <sup>2</sup>        | 15°C/W                                       |

| RoHS-Compliant Temperature, Soldering<br>Reflow       | 260(-5/+0)°C                                 |

| ESD                                                   | 2 kV HBM                                     |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> Transient currents of up to 100 mA do not cause latch-up.

<sup>2</sup> JEDEC 2S2P standard board.

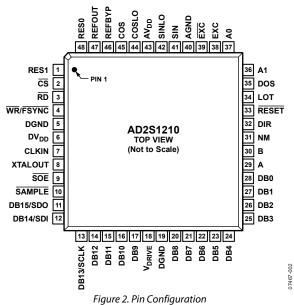

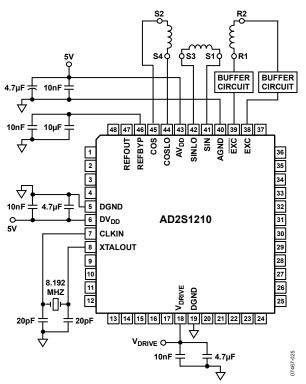

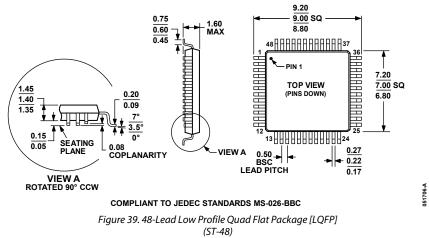

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 4. Pin Function Descriptions**

\_

| Pin   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1     | RES1             | Resolution Select 1. Logic input. RES1 in conjunction with RES0 allows the resolution of the AD2S1210 to be programmed. Refer to the Configuration of AD2S1210 section.                                                                                                                                                                                                                                                                               |

| 2     | CS               | Chip Select. Active low logic input. The device is enabled when $\overline{CS}$ is held low.                                                                                                                                                                                                                                                                                                                                                          |

| 3     | RD               | Edge-Triggered Logic Input. When the SOE pin is high, this pin acts as a frame synchronization signal and output enable for the parallel data outputs, DB15 to DB0. The output buffer is enabled when CS and RD are held low. When the SOE pin is low, the RD pin should be held high.                                                                                                                                                                |

| 4     | WR/FSYNC         | Edge-Triggered Logic Input. When the SOE pin is high, this pin acts as a frame synchronization signal and input<br>enable for the parallel data inputs, DB7 to DB0. The input buffer is enabled when CS and WR/FSYNC are held low.<br>When the SOE pin is low, the WR/FSYNC pin acts as a frame synchronization signal and enable for the serial data bus.                                                                                            |

| 5, 19 | DGND             | Digital Ground. These pins are ground reference points for digital circuitry on the AD2S1210. Refer all digital input signals to this DGND voltage. Both of these pins can be connected to the AGND plane of a system. The DGND and AGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                           |

| 6     | DV <sub>DD</sub> | Digital Supply Voltage, 4.75 V to 5.25 V. This is the supply voltage for all digital circuitry on the AD2S1210. The AV <sub>DD</sub> and DV <sub>DD</sub> voltages ideally should be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                          |

| 7     | CLKIN            | Clock Input. A crystal or oscillator can be used at the CLKIN and XTALOUT pins to supply the required clock frequency of the AD2S1210. Alternatively, a single-ended clock can be applied to the CLKIN pin. The input frequency of the AD2S1210 is specified from 6.144 MHz to 10.24 MHz.                                                                                                                                                             |

| 8     | XTALOUT          | Crystal Output. When using a crystal or oscillator to supply the clock frequency to the AD2S1210, apply the crystal across the CLKIN and XTALOUT pins. When using a single-ended clock source, the XTALOUT pin should be considered a no connect pin.                                                                                                                                                                                                 |

| 9     | SOE              | Serial Output Enable. Logic input. This pin enables either the parallel or serial interface. The serial interface is selected by holding the SOE pin high.                                                                                                                                                                                                                                                                                            |

| 10    | SAMPLE           | Sample Result. Logic input. Data is transferred from the position and velocity integrators to the position and velocity registers, after a high-to-low transition on the SAMPLE signal. The fault register is also updated after a high-to-low transition on the SAMPLE signal.                                                                                                                                                                       |

| 11    | DB15/SDO         | Data Bit 15/Serial Data Output Bus. When the $\overline{\text{SOE}}$ pin is high, this pin acts as DB15, a three-state data output pin controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ . When the $\overline{\text{SOE}}$ pin is low, this pin acts as SDO, the serial data output bus controlled by $\overline{\text{CS}}$ and $\overline{\text{WR}}/\overline{\text{FSYNC}}$ . The bits are clocked out on the rising edge of SCLK. |

| 12    | DB14/SDI         | Data Bit 14/Serial Data Input Bus. When the SOE pin is high, this pin acts as DB14, a three-state data output pin controlled by CS and RD. When the SOE pin is low, this pin acts as SDI, the serial data input bus controlled by CS and WR/FSYNC. The bits are clocked in on the falling edge of SCLK.                                                                                                                                               |

| Pin<br>No.  | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13          | DB13/SCLK          | Data Bit 13/Serial Clock. In parallel mode, this pin acts as DB13, a three-state data output pin controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ . In                                                                                                                                                                                                        |

| 15          | DDT5/SCER          | serial mode, this pin acts as the serial clock input.                                                                                                                                                                                                                                                                                                                        |

| 14 to<br>17 | DB12 to<br>DB9     | Data Bit 12 to Data Bit 9. Three-state data output pins controlled by $\overline{CS}$ and $\overline{RD}$ .                                                                                                                                                                                                                                                                  |

| 18          | V <sub>DRIVE</sub> | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Decouple this pin to DGND. The voltage range on this pin is 2.3 V to 5.25 V and may be different to the voltage range at $AV_{DD}$ and $DV_{DD}$ but should never exceed either by more than 0.3 V.                                                            |

| 20          | DB8                | Data Bit 8. Three-state data output pin controlled by $\overline{CS}$ and $\overline{RD}$ .                                                                                                                                                                                                                                                                                  |

| 21 to<br>28 | DB7 to DB0         | Data Bit 7 to Data Bit 0. Three-state data input/output pins controlled by $\overline{CS}$ , $\overline{RD}$ , and $\overline{WR}/\overline{FSYNC}$ .                                                                                                                                                                                                                        |

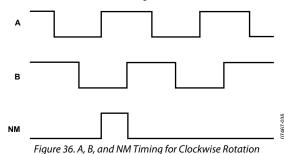

| 29          | A                  | Incremental Encoder Emulation Output A. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                                      |

| 30          | В                  | Incremental Encoder Emulation Output B. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                                      |

| 31          | NM                 | North Marker Incremental Encoder Emulation Output. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                           |

| 32          | DIR                | Direction. Logic output. This output is used in conjunction with the incremental encoder emulation outputs. The DIR output indicates the direction of the input rotation and is high for increasing angular rotation.                                                                                                                                                        |

| 33          | RESET              | Reset. Logic input. The AD2S1210 requires an external reset signal to hold the RESET input low until V <sub>DD</sub> is within the specified operating range of 4.75 V to 5.25 V.                                                                                                                                                                                            |

| 34          | LOT                | Loss of Tracking. Logic output. LOT is indicated by a logic low on the LOT pin and is not latched. Refer to the Loss of<br>Position Tracking Detection section.                                                                                                                                                                                                              |

| 35          | DOS                | Degradation of Signal. Logic output. Degradation of signal (DOS) is detected when either resolver input (sine or cosine) exceeds the specified DOS sine/cosine threshold or when an amplitude mismatch occurs between the sine and cosine input voltages. DOS is indicated by a logic low on the DOS pin. Refer to the Signal Degradation Detection section.                 |

| 36          | A1                 | Mode Select 1. Logic input. A1 in conjunction with A0 allows the mode of the AD2S1210 to be selected. Refer to the Configuration of AD2S1210 section.                                                                                                                                                                                                                        |

| 37          | A0                 | Mode Select 0. Logic input. A0 in conjunction with A1 allows the mode of the AD2S1210 to be selected. Refer to the Configuration of AD2S1210 section.                                                                                                                                                                                                                        |

| 38          | EXC                | Excitation Frequenc <u>y. A</u> nalog output. An on-board oscillator provides the sinusoidal excitation signal (EXC) and its complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the excitation frequency register.                                                                                                          |

| 39          | EXC                | Excitation Frequency Complement. Analog output. An on-board oscillator provides the sinusoidal excitation signal (EXC) and its complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the excitation frequency register.                                                                                                        |

| 40          | AGND               | Analog Ground. This pin is the ground reference points for analog circuitry on the AD2S1210. Refer all analog input signals and any external reference signal to this AGND voltage. Connect the AGND pin to the AGND plane of a system. The AGND and DGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis. |

| 41          | SIN                | Positive Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                             |

| 42          | SINLO              | Negative Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                             |

| 43          | AV <sub>DD</sub>   | Analog Supply Voltage, 4.75 V to 5.25 V. This pin is the supply voltage for all analog circuitry on the AD2S1210. The $AV_{DD}$ and $DV_{DD}$ voltages ideally should be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                             |

| 44          | COSLO              | Negative Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                             |

| 45          | COS                | Positive Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                             |

| 46          | REFBYP             | Reference Bypass. Connect reference decoupling capacitors at this pin. Typical recommended values are 10 µF and 0.01 µF.                                                                                                                                                                                                                                                     |

| 47          | REFOUT             | Voltage Reference Output.                                                                                                                                                                                                                                                                                                                                                    |

| 48          | RESO               | Resolution Select 0. Logic input. RES0 in conjunction with RES1 allows the resolution of the AD2S1210 to be programmed. Refer to the Configuration of AD2S1210 section.                                                                                                                                                                                                      |

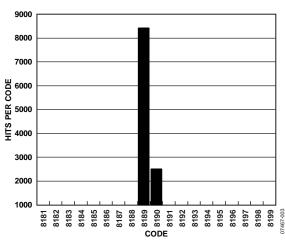

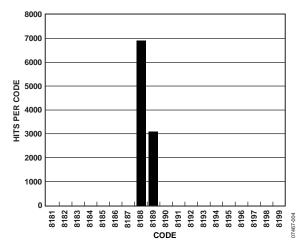

### **TYPICAL PERFORMANCE CHARACTERISTICS**

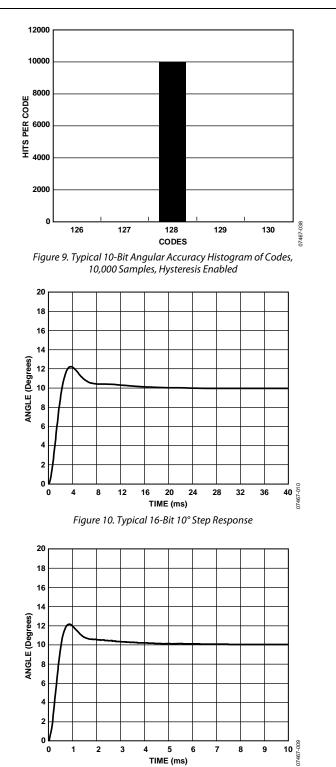

T<sub>A</sub> = 25°C, AV<sub>DD</sub> = DV<sub>DD</sub> = V<sub>DRIVE</sub> = 5 V, SIN/SINLO = 3.15 V p-p, COS/COSLO = 3.15 V p-p, CLKIN = 8.192 MHz , unless otherwise noted.

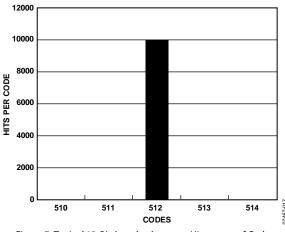

Figure 3. Typical 16-Bit Angular Accuracy Histogram Of Codes, 10,000 Samples

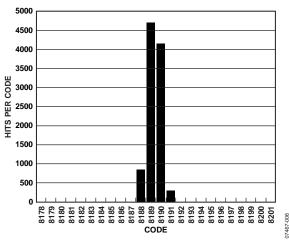

Figure 4. Typical 14-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 5. Typical 14-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Enabled

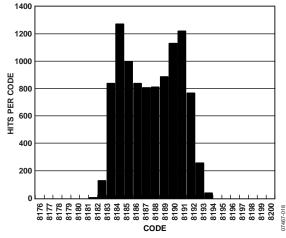

Figure 6. Typical 12-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 7. Typical 12-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Enabled

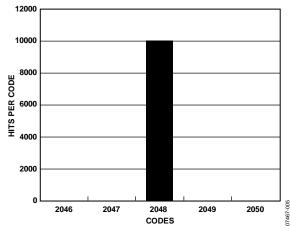

Figure 8. Typical 10-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 14. Typical 16-Bit 179° Step Response

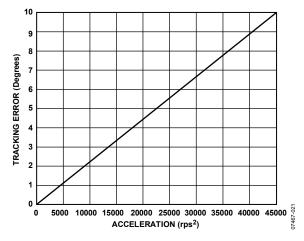

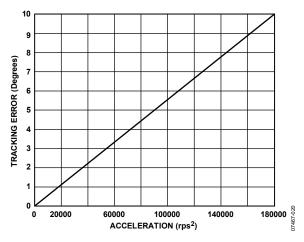

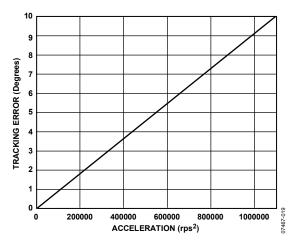

Figure 21. Typical 14-Bit Tracking Error vs. Acceleration

Figure 22. Typical 12-Bit Tracking Error vs. Acceleration

Figure 23. Typical 10-Bit Tracking Error vs. Acceleration

### **RESOLVER FORMAT SIGNALS**

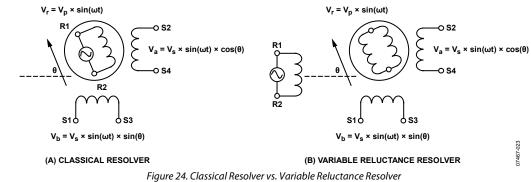

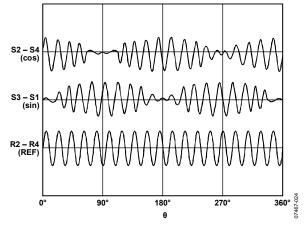

A resolver is a rotating transformer, typically with a primary winding on the rotor and two secondary windings on the stator. In the case of a variable reluctance resolver, there are no windings on the rotor, as shown in Figure 24. The primary winding is on the stator as well as the secondary windings, but the saliency in the rotor design provides the sinusoidal variation in the secondary coupling with the angular position. Either way, the resolver output voltages (S3 - S1, S2 - S4) have the same equations, as shown in Equation 1.

$$S3 - S1 = E_0 \sin \omega t \times \sin \theta$$

$$S2 - S4 = E_0 \sin \omega t \times \cos \theta$$

(1)

where:

$\theta$  is the shaft angle. Sin $\omega t$  is the rotor excitation frequency.  $E_0$  is the rotor excitation amplitude. The stator windings are displaced mechanically by 90° (see Figure 24). The primary winding is excited with an ac reference. The amplitude of subsequent coupling onto the stator secondary windings is a function of the position of the rotor (shaft) relative to the stator. The resolver, therefore, produces two output voltages (S3 - S1, S2 - S4) modulated by the sine and cosine of shaft angle. Resolver format signals refer to the signals derived from the output of a resolver, as shown in Equation 1. Figure 25 illustrates the output format.

Figure 25. Electrical Resolver Representation

### THEORY OF OPERATION resolver to digital conversion

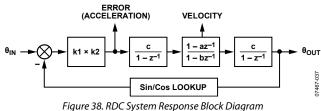

The AD2S1210 operates on a Type II tracking closed-loop principle. The output continually tracks the position of the resolver without the need for external conversion and wait states. As the resolver moves through a position equivalent to the least significant bit weighting, the output is updated by one LSB.

The converter tracks the shaft angle  $\theta$  by producing an output angle  $\phi$  that is fed back and compared to the input angle  $\theta$ , and the resulting error between the two is driven towards 0 when the converter is correctly tracking the input angle. To measure the error, S3 – S1 is multiplied by cos $\phi$  and S2 – S4 is multiplied by sin $\phi$  to give

$E_0 \sin \omega t \times \sin \theta \cos \phi$  (for S3 – S1)

$E_0 \sin \omega t \times \cos \theta \sin \phi$  (for S2 – S4)

The difference is taken, giving

$E_0 \sin \omega t \times (\sin \theta \cos \phi - \cos \theta \sin \phi) \tag{2}$

This signal is demodulated using the internally generated synthetic reference, yielding

$$E_0(\sin\theta\cos\phi - \cos\theta\sin\phi) \tag{3}$$

Equation 3 is equivalent to  $E_0 \sin(\theta - \phi)$ , which is approximately equal to  $E_0(\theta - \phi)$  for small values of  $\theta - \phi$ , where  $\theta - \phi =$  angular error.

The value  $E_0 (\theta - \phi)$  is the difference between the angular error of the rotor and the digital angle output of the converter.

A phase-sensitive demodulator, some integrators, and a compensation filter form a closed-loop system that seeks to null the error signal. When this is accomplished,  $\varphi$  equals the Resolver Angle  $\theta$  within the rated accuracy of the converter. A Type II tracking loop is used so that constant velocity inputs can be tracked without inherent error.

#### FAULT DETECTION CIRCUIT

The AD2S1210 fault detection circuit can sense loss of resolver signals, out-of-range input signals, input signal mismatch, or loss of position tracking; however, in the event of a fault, the position indicated by the AD2S1210 may differ significantly from the actual shaft position of the resolver.

#### **Monitor Signal**

The AD2S1210 generates a monitor signal by comparing the angle in the position register to the incoming sine and cosine signals from the resolver. The monitor signal is created in a similar fashion to the error signal described in the Resolver to Digital Conversion section. The incoming signals,  $\sin\theta$  and  $\cos\theta$ , are multiplied by the sin and  $\cos \theta$  the output angle, respectively, and then added together.

$Monitor = A1 \times \sin \theta \times \sin \phi + A2 \times \cos \theta \times \cos \phi \tag{4}$

where:

A1 is the amplitude of the incoming sine signal  $(A1 \times \sin\theta)$ . A2 is the amplitude of the incoming cosine signal  $(A2 \times \cos\theta)$ .  $\theta$  is the resolver angle.

$\phi$  is the angle stored in the position register.

Note that Equation 4 is shown after demodulation, with the Carrier Signal sin $\omega$ t removed. Also, note that for matched input signal (that is, a no fault condition), A1 = A2.

When A1 = A2 and the converter is tracking ( $\theta = \phi$ ), the monitor signal output has a constant magnitude of A1 (Monitor = A1 × (sin<sup>2</sup>  $\theta$  + cos<sup>2</sup>  $\theta$ ) = A1), which is independent of shaft angle. When A1  $\neq$  A2, the monitor signal magnitude varies between A1 and A2 at twice the rate of shaft rotation. The monitor signal is used as described in the following sections to detect degradation or loss of input signals.

#### Loss of Signal Detection

The AD2S1210 indicates that a loss of signal (LOS) has occurred for four separate conditions.

- When either resolver input (sine or cosine) falls below the specified LOS sine/cosine threshold. This threshold is defined by the user and is set by writing to the internal register, Address 0x88 (see the Register Map section).

- When any of the resolver input pins (SIN, SINLO, COS, or COSLO) are disconnected from the sensor.

- When any of the resolver input pins (SIN, SINLO, COS, or COSLO) are clipping the power rail or ground rail of the AD2S1210. Refer to the Sine/Cosine Input Clipping section.

- When a configuration parity error has occurred. Refer to the Configuration Parity Error section.

A loss of signal is caused if either of the stator windings of the resolver (sine or cosine) are open circuit or have a number of shorted turns. LOS is indicated by both the DOS and LOT pins latching as logic low outputs. The DOS and LOT pins are reset to a no fault state when the user enters configuration mode and reads the fault register. The LOS condition has priority over both the DOS and LOT conditions, as shown in Table 6. To determine the cause of the LOS fault detection, the user must read the fault register, Address 0xFF (see the Register Map section).

When a loss of signal is detected due to the resolver inputs (sine or cosine) falling below the specified LOS sine/cosine threshold, the electrical angle through which the resolver may rotate before the LOS can be detected by the AD2S1210 is referred to as the LOS angular latency. This is defined by the specified LOS sine/ cosine threshold set by the user and the maximum amplitude of the input signals being applied to the AD2S1210. The worst-case angular latency can be calculated as follows:

$$Angular Latency = 2 \times Arc \cos \left[ \frac{LOS \ threshold}{\max \ sine \ / \ cosine \ amplitude} \right]$$

(5)

The preceding equation is based on the worst-case angular error, which can be seen by the AD2S1210 before an LOS fault is indicated. This occurs if one of the resolver input signals, either sine or cosine, is lost while the remaining signal is at its peak amplitude, for example, if the sine input is lost while the input angle is 90°. The worst-case angular latency is twice the worst-case angular error.

#### Signal Degradation Detection

The AD2S1210 indicates that a degradation of signal (DOS) has occurred for two separate conditions.

- When either resolver input (sine or cosine) exceeds the specified DOS sine/cosine threshold. This threshold is defined by the user and is set by writing to the internal register, Address 0x89 (see the Register Map section).

- When the amplitudes of the input signals, sine and cosine, mismatch by more than the specified DOS sine/cosine mismatch threshold. This threshold is defined by the user and is set by writing to the internal register, Address 0x8A (see the Register Map section). The AD2S1210 continuously stores the minimum and maximum magnitude of the monitor signal in internal registers. The difference between the minimum and maximum is calculated to determine if a DOS mismatch has occurred. The initial values for the minimum and maximum internal registers must be defined by the user, at Address 0x8C and Address 0x8B, respectively (see the Register Map section).

DOS is indicated by a logic low on the DOS pin. When DOS is indicated, the output is latched low until the user enters configuration mode and reads the fault register. The DOS condition has priority over the LOT condition, as shown in Table 6. To determine the cause of the DOS fault detection, the user must read the fault register, Address 0xFF (see the Register Map section).

#### Time Latency for LOS and DOS Detection

Note that the monitor signal is generated on the active edge of the internal AD2S1210 clock. The internal clock is generated by dividing the externally applied CLKIN frequency by 2; for example, when using a CLKIN frequency of 8.192 MHz the internal AD2S1210 clock is 4.096 MHz. The AD2S1210 continuously stores the minimum and maximum magnitude of the monitor signal in internal registers. The values stored in these internal registers are compared to the LOS and DOS thresholds configured by the user at set intervals. This interval, known as the window counter period, is dependent on the excitation frequency configured by the user. It is set to ensure that two window counter periods include at least one full period of the excitation frequency applied to the resolver. The window counter period is defined in terms of internal clock cycles. The window counter periods for the range of excitation frequencies on the AD2S1210 are outlined in Table 5.

| Table 5. Window Counter Period vs. Excitation Frequency |

|---------------------------------------------------------|

| Range, CLKIN = 8.192 MHz                                |

| Excitation Frequency<br>Range | Number of<br>Internal Clock<br>Cycles | Window<br>Counter Period<br>(µs) <sup>1</sup> |

|-------------------------------|---------------------------------------|-----------------------------------------------|

| 2 kHz ≤ Exc Freq < 4 kHz      | 1065                                  | 260                                           |

| 4 kHz ≤ Exc Freq < 8 kHz      | 554                                   | 135.25                                        |

| 8 kHz ≤ Exc Freq ≤ 20 kHz     | 256                                   | 62.5                                          |

<sup>1</sup> CLKIN = 8.192 MHz. The window counter period scales with clock frequency and can be calculated by multiplying the number of internal clock cycles by the period of the internal clock frequency, that is, CLKIN/2.

The AD2S1210 detects an LOS or DOS due to the resolver inputs (sine or cosine) falling below or exceeding the LOS and DOS thresholds within two window counter periods. For example, with an excitation frequency of 10 kHz, a fault is detected within 125  $\mu$ s. A persistent fault is detected within one window counter period of the reading and clearing the fault register.

Note that the time latency to detect the occurrence of a DOS mismatch fault is dependent on the speed of rotation of the resolver. The worst-case time latency to detect a DOS mismatch fault is the time required for one full rotation of the resolver.

#### Loss of Position Tracking Detection

The AD2S1210 indicates that a loss of tracking (LOT) has occurred when

- The internal error signal of the AD2S1210 has exceeded the specified angular threshold. This threshold is defined by the user and is set by writing to the internal register, Address 0x8D (see the Register Map section).

- The input signal exceeds the maximum tracking rate. The maximum tracking rate depends on the resolution defined by the user and the CLKIN frequency.

LOT is indicated by a logic low on the LOT pin and is not latched. LOT has hysteresis and is not cleared until the internal error signal is less than the value defined in the LOT low threshold register, Address 0x8E (see the Register Map section).

When the maximum tracking rate is exceeded, LOT is cleared only if the velocity is less than the maximum tracking rate and the internal error signal is less than the value defined in the LOT low threshold register. LOT can be indicated for step changes in position (such as after a RESET signal is applied to the AD2S1210). It is also useful as a built-in test to indicate that the tracking converter is functioning properly. The LOT condition has lower priority than both the DOS and LOS conditions, as shown in Table 6. The LOT and DOS conditions cannot be indicated using the LOT and DOS pins at the same time. However, both conditions are indicated separately in the fault register. To determine the cause of the LOT fault detection, the user must read the fault register, Address 0xFF (see the Register Map section).

| Condition                   | DOS Pin | LOT Pin | Order of<br>Priority |

|-----------------------------|---------|---------|----------------------|

| Loss of Signal (LOS)        | 0       | 0       | 1                    |

| Degradation of Signal (DOS) | 0       | 1       | 2                    |

| Loss of Tracking (LOT)      | 1       | 0       | 3                    |

| No Fault                    | 1       | 1       | N/A                  |

#### Table 6. Fault Detection Decoding

#### Sine/Cosine Input Clipping

The AD2S1210 indicates that a clipping error has occurred if any of the resolver input pins (SIN, SINLO, COS, or COSLO) are clipping the power rail or ground rail of the AD2S1210. The clipping fault is indicated if the input amplitudes are less than 0.15 V or greater then AV<sub>DD</sub> – 0.2 V for more than 4 µs.

Sine/cosine input clipping error is indicated by both the DOS and LOT pins latching as logic low outputs. Sine/cosine input clipping error is also indicated by Bit D7 of the fault register being set high. The DOS and LOT pins are reset to a no fault state when the user enters configuration mode and reads the fault register.

#### **Configuration Parity Error**