# **10-Gbps Ethernet MAC MegaCore Function**

**User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-01083-3.3

Document last updated for Altera Complete Design Suite version: Document publication date: 13.1 February 2014

Copyright © 2014 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, and specific device designations are trademarks and/or service marks of Altera Corporation in the U.S. and other countries. All other words and logos identified as trademarks and/or service marks are the property of Altera Corporation or their respective owners. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### **Chapter 1. About This IP Core**

| 1.1. Features                             | 1–1 |

|-------------------------------------------|-----|

| 1.2. Release Information                  | 1–2 |

| 1.3. Device Family Support                | 1–3 |

| 1.4. IP Core Verification                 |     |

| 1.4.1. Simulation Environment             | 1–4 |

| 1.4.2. Compatibility Testing Environment  | 1–4 |

| 1.5. Performance and Resource Utilization |     |

### **Chapter 2. Getting Started with Altera IP Cores**

| 2.1. Installation and Licensing               | . 2–1 |

|-----------------------------------------------|-------|

| 2.2. Design Flows                             | . 2–2 |

| 2.3. MegaWizard Plug-In Manager Flow          | . 2–2 |

| 2.3.1. Specifying Parameters                  |       |

| 2.3.2. Simulate the IP Core                   |       |

| 2.4. Qsys System Integration Tool Design Flow | . 2–4 |

| 2.4.1. Specify Parameters                     | . 2–4 |

| 2.4.2. Complete the Qsys System               | . 2–5 |

| 2.4.3. Simulate the System                    |       |

| 2.5. 10GbE MAC Parameter Settings             |       |

#### Chapter 3. 10GbE MAC Design Examples

| 3.1. Software and Hardware Requirements                            |  |

|--------------------------------------------------------------------|--|

| 3.2. 10GbE Design Example Components                               |  |

| 3.2.0.1. Ethernet Loopback Module                                  |  |

| 3.2.0.2. Base Addresses                                            |  |

| 3.3. 10GbE Design Example Files                                    |  |

| 3.4. Creating a New 10GbE Design                                   |  |

| 3.5. 10GbE Design Example Parameter Settings                       |  |

| 3.6. 10GbE Testbenches                                             |  |

| 3.6.1. 10GbE Testbench                                             |  |

| 3.6.2. 10GbE Testbench Component                                   |  |

| 3.6.3. 10GbE Testbench Files                                       |  |

| 3.6.4. 10GbE Testbench Simulation Flow                             |  |

| 3.6.5. Simulating the 10GbE Testbench with the ModelSim Simulator  |  |

| 3.6.6. Enabling Local Loopback                                     |  |

| 3.6.7. 10GbE Simulation Timing Diagrams                            |  |

| 3.7. 10GbE Design Example Compilation and Verification in Hardware |  |

| 3.7.1. Compiling the 10GbE Design                                  |  |

| 3.7.2. Verifying the 10GbE Design in Hardware                      |  |

| 3.7.3. Debugging                                                   |  |

| 3.7.4. 10GbE Design Transmit and Receive Latencies                 |  |

| 3.7.5. 10GbE Design Performance and Resource Utilization           |  |

|                                                                    |  |

### Chapter 4. 10GbE MAC with IEEE1588v2 Design Example

| 4.1. Software Requirements                            |  |

|-------------------------------------------------------|--|

| 4.2. 10GbE with IEEE 1588v2 Design Example Components |  |

| 4.2.1. Base Addresses                                 |  |

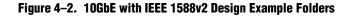

| 4.3. 10GbE with IEEE 1588v2 Design Example Files                           | . 4–4 |

|----------------------------------------------------------------------------|-------|

| 4.4. Creating a New 10GbE with IEEE 1588v2 Design                          |       |

| 4.5. 10GbE with IEEE 1588v2 Testbench                                      |       |

| 4.5.1. 10GbE with IEEE 1588v2 Testbench                                    |       |

| 4.5.2. 10GbE with IEEE 1588v2 Testbench Components                         |       |

| 4.5.3. 10GbE with IEEE 1588v2 Testbench Files                              |       |

| 4.5.4. 10GbE with IEEE 1588v2 Testbench Simulation Flow                    | . 4–7 |

| 4.5.5. Simulating 10GbE with IEEE 1588v2 Testbench with ModelSim Simulator | . 4–7 |

|                                                                            |       |

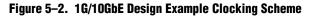

### Chapter 5. 1G/10GbE MAC Design Example

| 5.1. Software and Hardware Requirements                              |  |

|----------------------------------------------------------------------|--|

| 5.2. 1G/10GbE Design Example Components                              |  |

| 5.2.1. Reconfiguration Bundle Parameters                             |  |

| 5.2.2. Base Addresses                                                |  |

| 5.3. 1G/10GbE Design Example Files                                   |  |

| 5.4. Creating a New 1G/10GbE Design                                  |  |

| 5.5. 1G/10GbE Testbench                                              |  |

| 5.5.1. 1G/10GbE Testbench                                            |  |

| 5.5.2. 1G/10GbE Testbench Components                                 |  |

| 5.5.3. 1G/10GbE Testbench Files                                      |  |

| 5.5.4. 1G/10GbE Testbench Simulation Flow                            |  |

| 5.5.4.1. 1G/10Gb Ethernet Mode                                       |  |

| 5.5.4.2. Backplane-KR Mode                                           |  |

| 5.5.5. Simulating the 1G/10GbE Testbench with the ModelSim Simulator |  |

| 5.5.6. 1G/10GbE Simulation Timing Diagrams                           |  |

| 5.6. 1G/10GbE Design Example Compilation                             |  |

| 5.6.1. Compiling the 1G/10GbE Design                                 |  |

| 5.6.2. 1G/10GbE Design Performance and Resource Utilization          |  |

|                                                                      |  |

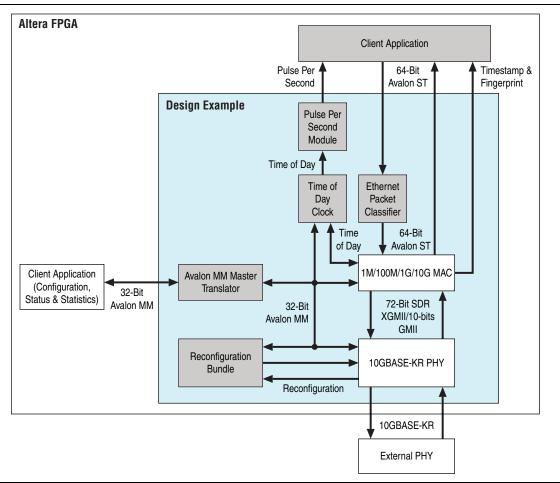

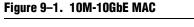

## Chapter 6. 10M-10GbE MAC with IEEE 1588v2 Design Example

| 6.1. Software and Hardware Requirements                                            | 6–1 |

|------------------------------------------------------------------------------------|-----|

| 6.2. 10M-10GbE MAC with IEEE 1588v2 Design Example Components                      | 6–1 |

| 6.2.1. Base Addresses                                                              | 6–3 |

| 6.3. 10M-10GbE MAC with IEEE 1588v2 Design Example Files                           | 6–3 |

| 6.4. Creating a New 10M-10GbE MAC with IEEE 1588v2 Design                          | 6–4 |

| 6.5. 10M-10GbE with IEEE 1588v2 Testbench                                          |     |

| 6.5.1. 10M-10GbE with IEEE 1588v2 Testbench                                        | 6–5 |

| 6.5.2. 10M-10GbE with IEEE 1588v2 Testbench Components                             | 6–5 |

| 6.5.3. 10M-10GbE MAC with IEEE 1588v2 Testbench Files                              | 6–6 |

| 6.5.4. 10M-10GbE MAC with IEEE 1588v2 Testbench Simulation Flow                    | 6–7 |

| 6.5.5. Simulating 10M-10GbE MAC with IEEE 1588v2 Testbench with ModelSim Simulator | 6–7 |

### **Chapter 7. Functional Description**

| 7.1. Architecture                                      | 7–1 |

|--------------------------------------------------------|-----|

| 7.2. Interfaces                                        |     |

| 7.2.1. Avalon-ST Interface                             | 7–3 |

| 7.2.2. SDR XGMII                                       | 7–4 |

| 7.2.3. GMII                                            | 7–4 |

| 7.2.4. MII                                             | 7–4 |

| 7.2.5. Avalon-MM Control and Status Register Interface | 7–4 |

| 7.3. Frame Types                                       | 7–5 |

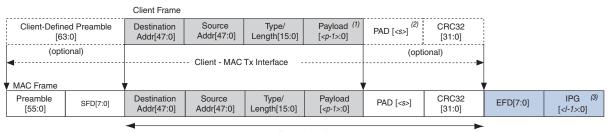

| 7.4. Transmit Datapath                                 | 7–5 |

| 7.4.1. Frame Payload Padding                           | 7–5 |

| 7.4.2. Address Insertion                                      |      |

|---------------------------------------------------------------|------|

| 7.4.3. Frame Check Sequence (CRC-32) Insertion                |      |

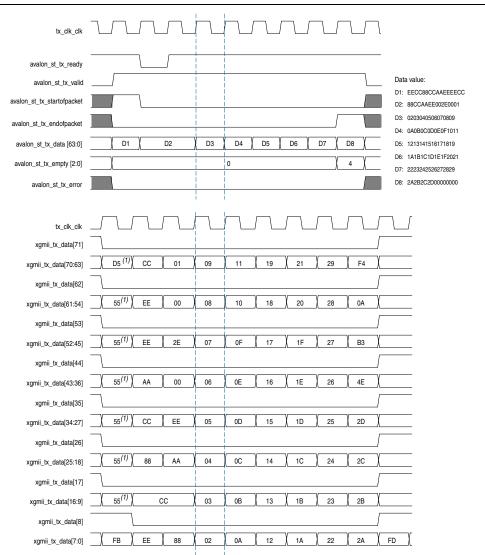

| 7.4.4. XGMII Encapsulation                                    |      |

| 7.4.5. Inter-Packet Gap Generation and Insertion              |      |

| 7.4.6. SDR XGMII Transmission                                 |      |

| 7.5. Receive Datapath                                         |      |

| 7.5.1. Minimum Inter-Packet Gap                               |      |

| 7.5.2. XGMII Decapsulation                                    |      |

| 7.5.3. Frame Check Sequence (CRC-32) Checking                 |      |

| 7.5.4. Address Checking                                       |      |

| 7.5.5. Frame Type Checking                                    |      |

| 7.5.6. Length Checking                                        |      |

| 7.5.7. CRC-32 and Pad Removal                                 | 7 14 |

| 7.5.8. Overflow Handling                                      |      |

| 7.6. Transmit and Receive Latencies                           |      |

|                                                               |      |

| 7.7. Congestion and Flow Control                              |      |

| 7.7.1. IEEE 802.3 Flow Control                                |      |

| 7.7.1.1. Pause Frame Reception                                |      |

| 7.7.1.2. Pause Frame Transmission                             |      |

| 7.7.2. Priority-Based Flow Control                            |      |

| 7.7.2.1. PFC Frame Reception                                  |      |

| 7.7.2.2. PFC Frame Transmission                               |      |

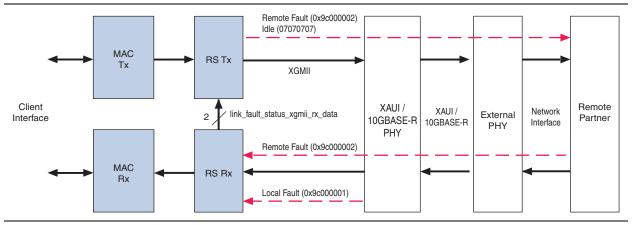

| 7.8. Error Handling (Link Fault)                              |      |

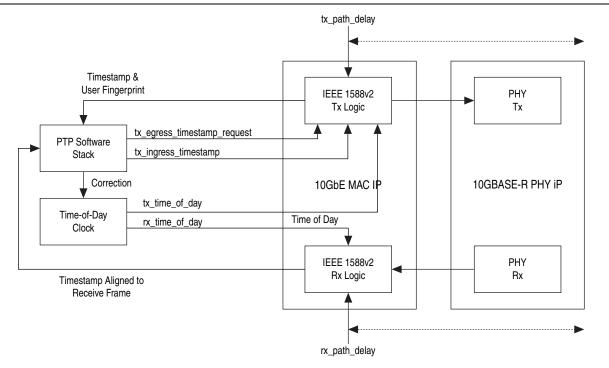

| 7.9. IEEE 1588v2                                              |      |

| 7.9.1. Architecture                                           |      |

| 7.9.2. Transmit Datapath                                      |      |

| 7.9.3. Receive Datapath                                       |      |

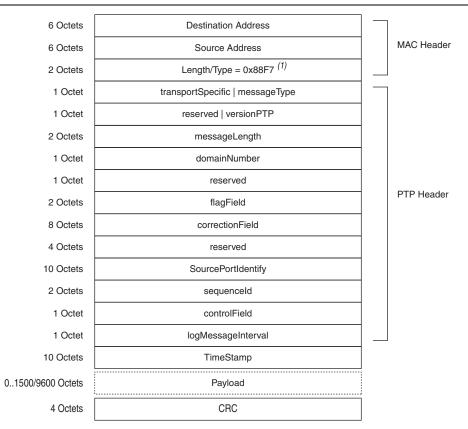

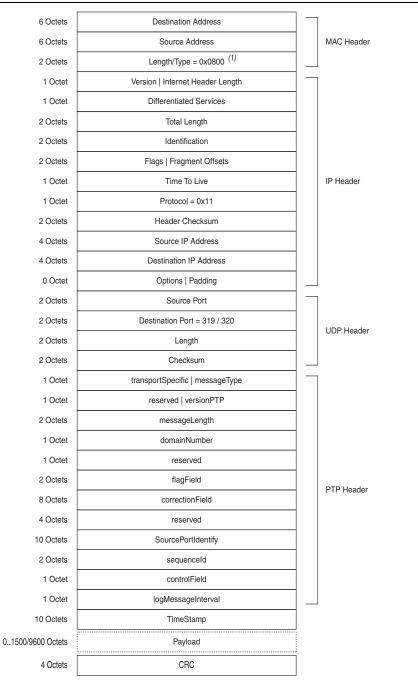

| 7.9.4. Frame Format                                           |      |

| 7.9.4.1. PTP Packet in IEEE 802.3                             |      |

| 7.9.4.2. PTP Packet over UDP/IPv4                             |      |

| 7.9.4.3. PTP Packet over UDP/IPv6                             |      |

| Oberter O. Berletere                                          |      |

| Chapter 8. Registers                                          |      |

| 8.1. MAC Registers                                            |      |

| 8.1.1. Rx_frame_control Register                              |      |

| 8.1.2. Rx_pfc_control Register                                |      |

| 8.2. MAC Registers for IEEE 1588v2 Feature                    |      |

| 8.2.1. Configuring PMA Analog and Digital Delay               |      |

| 8.3. Register Initialization                                  |      |

| Chapter 9. Interface Signals                                  |      |

| • •                                                           | 0.2  |

| 9.0.1. Clock and Reset Signals                                |      |

| 9.0.2. Avalon-ST Transmit and Receive Interface Signals       |      |

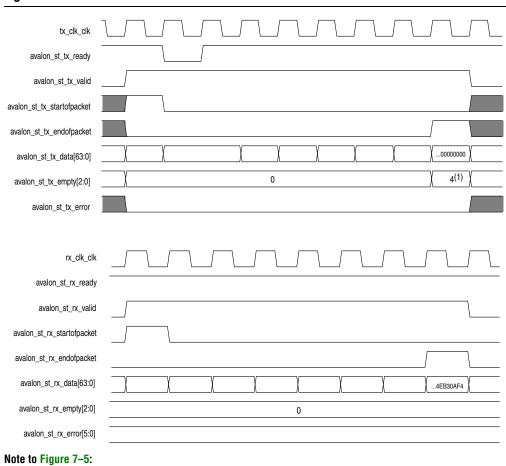

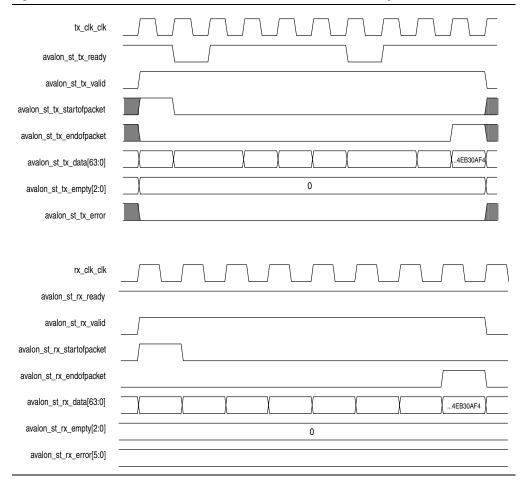

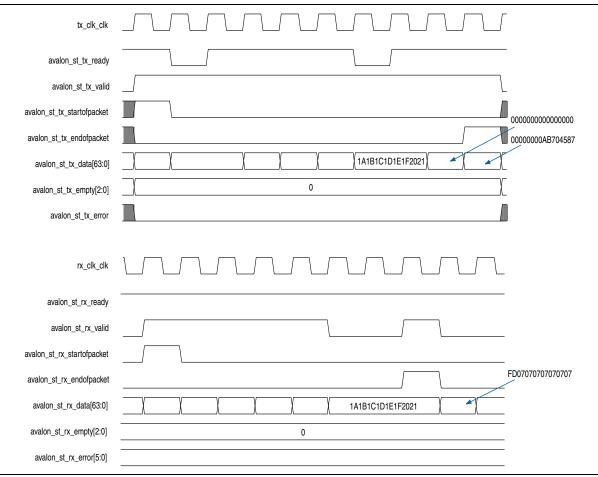

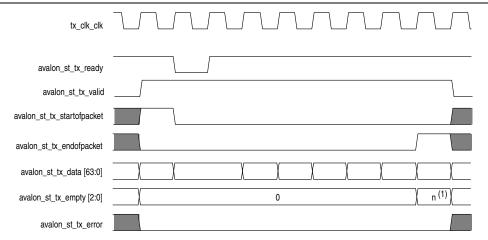

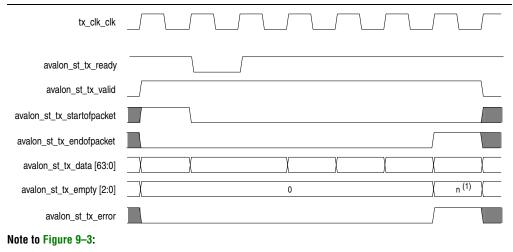

| 9.0.2.1. Timing Diagrams—Avalon-ST Transmit Interface         |      |

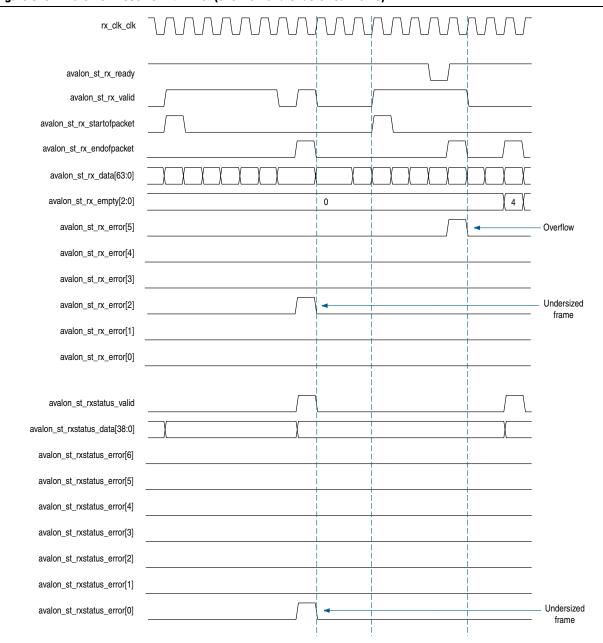

| 9.0.2.2. Timing Diagrams—Avalon-ST Receive Interface          |      |

| Σ.υ.ο. δΙ/Κ Αυτίνιματα το |      |

| , solution of necesse interface interface           |      |

|-----------------------------------------------------|------|

| 9.0.3. SDR XGMII                                    | 9–8  |

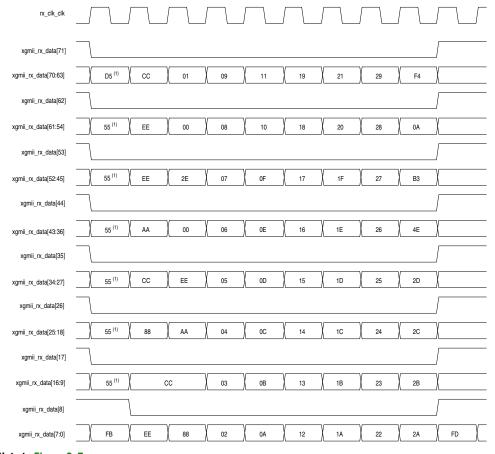

| 9.0.3.1. Timing Diagrams—SDR XGMII                  | 9–9  |

| 9.0.4. GMII Signals                                 | 9–11 |

| 9.0.5. MII Signals                                  | 9–11 |

| 9.0.6. Avalon-MM Programming Interface Signals      | 9–12 |

| 9.0.7. Avalon-ST Status and Pause Interface Signals | 9–13 |

| 9.0.8. 10M-10GbE MAC Speed Control Signal           | 9–20 |

| 9.0.9. IEEE 1588v2 Interface Signals                | 9–20 |

|                                                     |      |

| 9.0.9.1. IEEE 1588v2 Timestamp Interface Signals | 9–20 |

|--------------------------------------------------|------|

| 9.0.9.2. ToD Clock Interface Signals             |      |

| 9.0.9.3. Path Delay Interface Signals            | 9–25 |

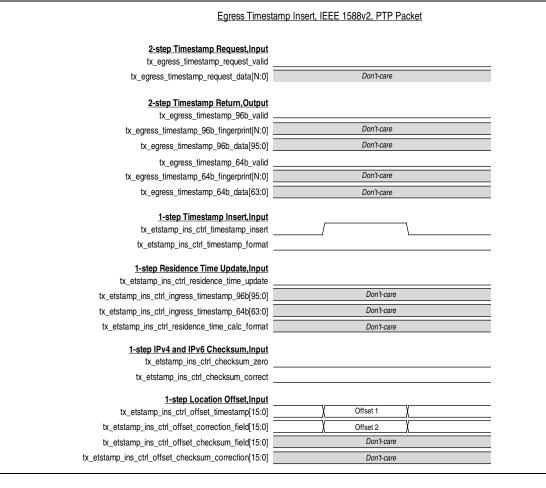

| 9.0.9.4. Timing Diagrams—IEEE 1588v2 Timestamp   | 9–27 |

### **Chapter 10. Design Considerations**

| 10.1. SDR XGMII to DDR XGMII Conversion                     |  |

|-------------------------------------------------------------|--|

| 10.1.1. ALTDDIO_IN Megafunction Configuration               |  |

| 10.1.2. ALTDDIO_OUT Megafunction Configuration              |  |

| 10.2. 10GbE MAC and PHY Connection with XGMII               |  |

| 10.3. Sharing TX and RX Clocks for Multi-Port System Design |  |

| 10.4. Sharing Reference Clocks for Multi-Port System Design |  |

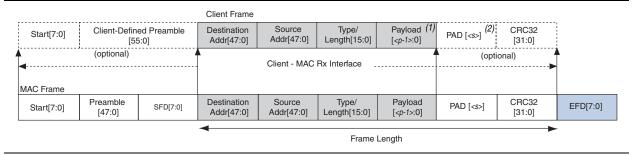

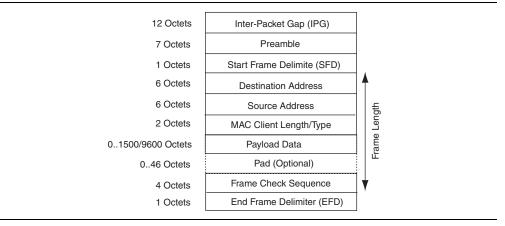

### Appendix A. Frame Format

| A.1. Ethernet Frame                         |     |

|---------------------------------------------|-----|

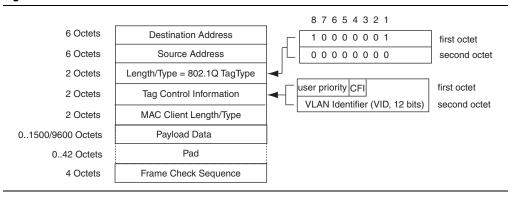

| A.2. VLAN and Stacked VLAN Tagged MAC Frame | A–2 |

| A.3. Pause Frame                            |     |

| A.4. Priority-Based Flow Control Frame      | A–4 |

| •                                           |     |

### Appendix B. Time-of-Day (ToD) Clock

| B.1. Features                               | B–1 |

|---------------------------------------------|-----|

| B.2. Device Family Support                  | B–1 |

| B.3. Performance and Resource Utilization   | B–1 |

| B.4. Parameter Setting                      | B-2 |

| B.5. ToD Clock Interface Signals            | B-2 |

| B.5.1. Avalon-MM Control Interface Signal   | B-3 |

| B.5.2. Avalon-ST Transmit Interface Signal  | B-3 |

| B.6. ToD Clock Configuration Register Space | B-4 |

| B.6.1. Adjusting ToD's Drift                | B-5 |

|                                             |     |

### Appendix C. Packet Classifier

| C.1. Block Diagram                      | . C–1 |

|-----------------------------------------|-------|

| C.2. Packet Classifier Signals          | . C-2 |

| C.2.1. Common Clock and Reset Signals   | . C–2 |

| C.2.2. Avalon-ST Interface Signals      |       |

| C.2.3. Ingress Control Signals          | . C–3 |

| C.2.4. Control Insert Signals           |       |

| C.2.5. Timestamp Field Location Signals |       |

|                                         |       |

### Appendix D. ToD Synchronizer

| D.1. Device Family Support               | . D–1 |

|------------------------------------------|-------|

| D.2. Block Diagram                       | . D–2 |

| D.3. ToD Synchronizer Parameter Settings | . D–3 |

| D.4. ToD Synchronizer Signals            |       |

| D.4.1. Common Clock and Reset Signals    | . D–4 |

| D.4.2. Interface Signals                 | . D-4 |

### **Additional Information**

| Document Revision History | Info-1 |

|---------------------------|--------|

| How to Contact Altera     |        |

| Typographic Conventions   | Info-4 |

# 1. About This IP Core

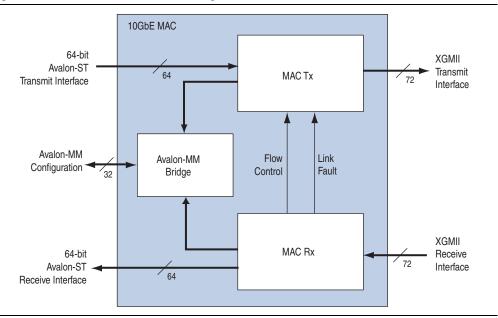

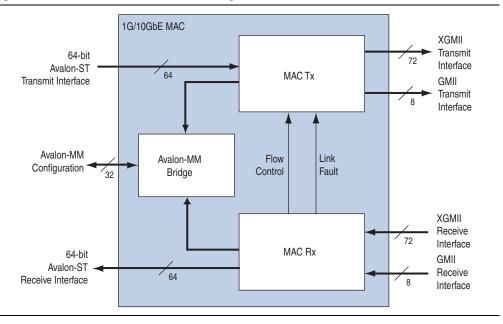

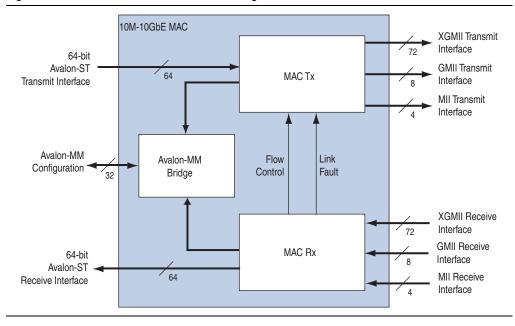

The 10-Gbps Ethernet (10GbE) Media Access Controller (MAC) IP core is a configurable component that implements the IEEE 802.3-2008 specification. The IP core offers the following modes:

- 10 Gbps mode—uses the Avalon<sup>®</sup> Streaming (Avalon-ST) interface on the client side and the single data rate (SDR) XGMII on the network side.

- 1 Gbps/10 Gbps mode— uses the Avalon-ST interface on the client side and GMII/SDR XGMII on the network side.

- 10 Mbps/100 Mbps/1 Gbps/10 Gbps (10M-10G) mode—uses the Avalon-ST interface on the client side and MII/GMII/SDR XGMII on the network side.

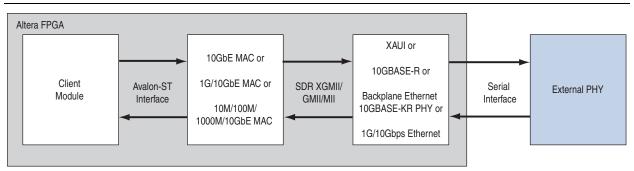

To build a complete Ethernet subsystem in an Altera<sup>®</sup> device and connect it to an external device, you can use the 10GbE MAC IP core with an Altera PHY IP core such as a soft XAUI PHY in FPGA fabric, hard silicon-integrated XAUI PHY, a 10GBASE-R PHY, a Backplane Ethernet 10GBASE-KR PHY, or a 1G/10 Gbps Ethernet PHY IP.

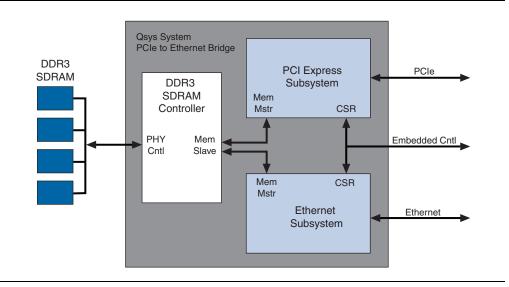

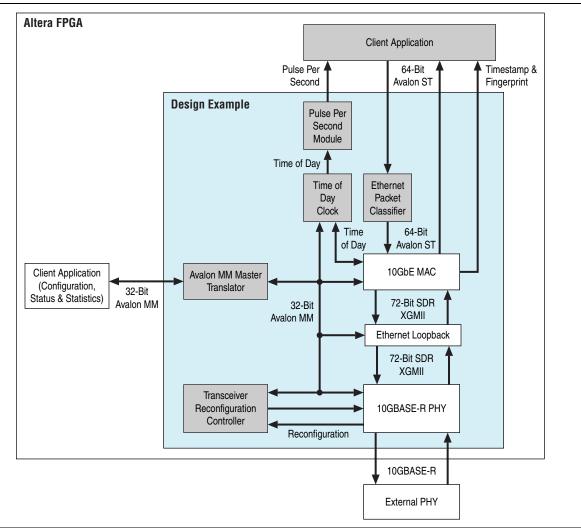

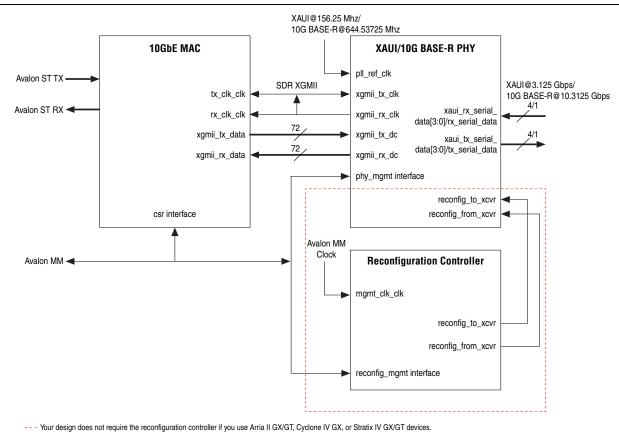

Figure 1–1 illustrates a system with the 10GbE MAC IP core.

#### Figure 1–1. Typical Application of 10GbE MAC

# **1.1. Features**

The 10GbE MAC supports the following features:

- Operating modes: 10 Mbps, 100 Mbps, 1 Gbps and 10 Gbps.

- Support for full duplex only.

- Avalon-ST 64-bit wide client interface running at 156.25 MHz.

- Direct interface to 4-bit MII running at 125 MHZ with clock enable; 2.5 MHz for 10 Mbps and 25 MHz for 100 Mbps.

- Direct interface to 8-bit GMII running at 125 MHZ.

- Direct interface to 64-bit SDR XGMII running at 156.25 MHZ.

- Virtual local area network (VLAN) and stacked VLAN tagged frames filtering as specified by IEEE 802.IQ and 802.1ad (Q-in-Q) standards respectively.

- Optional cyclic redundancy code (CRC)-32 computation and insertion on the transmit datapath; CRC checking on the receive datapath with optional forwarding of the frame check sequence (FCS) field to the client application.

- Checking of receive frames for FCS error, undersized and oversized frames, and payload length error.

- Deficit idle counter (DIC) for optimized performance with average inter-packet gap (IPG) of 12 bytes for LAN applications.

- Optional statistics collection on the transmit and receive datapaths.

- Packets termination when the transmit datapath receives incomplete packets.

- Programmable maximum length of transmit and receive frames up to 64 Kbytes (KB).

- Programmable promiscuous (transparent) mode.

- Optional Ethernet flow control and priority-based flow control (PFC) using pause frames with programmable pause quanta. The PFC supports up to 8 priority queues.

- Optional padding termination on the receive datapath and insertion on the transmit datapath.

- Design examples with optional loopback and testbench for design verification.

- Optional preamble passthrough mode on the transmit and receive datapaths. The preamble passthrough mode allows you to define the preamble in the client frame.

- Programmable datapath option to allow separate instantiation of MAC TX block, MAC RX block, or both MAC TX and MAC RX blocks.

- Optional IEEE 1588v2 feature for the following configurations:

- 10GbE MAC with 10GBASE-R PHY MegaCore function

- 1G/10GbE MAC with Backplane Ethernet 10GBASE-KR PHY MegaCore function

- Multi-speed 10M-10GbE MAC with Backplane Ethernet 10GBASE-KR PHY MegaCore function

# **1.2. Release Information**

Table 1–1 lists information about this release of the 10GbE MAC IP core.

| Item          | Description   |

|---------------|---------------|

| Version       | 13.1          |

| Release Date  | November 2013 |

| Ordering Code | IP-10GETHMAC  |

| Product ID    | ID 00D9       |

| Vendor ID     | 6AF7          |

#### Table 1–1. Release Information

# **1.3. Device Family Support**

MegaCore functions provide the following support for Altera device families:

- Preliminary support—Altera verifies the IP core with preliminary timing models for this device family. The core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- *Final support*—Altera verifies the IP core with final timing models for this device family. The core meets all functional and timing requirements for the device family and can be used in production designs.

Table 1–2 shows the level of support offered by the 10GbE MAC for the following Altera device family.

| Device Family                | Support     |  |

|------------------------------|-------------|--|

| Arria <sup>®</sup> II GX, GZ | Final       |  |

| Arria V GT, GX, and GZ       | Preliminary |  |

| Arria V SoC                  | Preliminary |  |

| Cyclone <sup>®</sup> IV GX   | Final       |  |

| Cyclone V                    | Preliminary |  |

| Cyclone V SoC                | Preliminary |  |

| Stratix III                  | Final       |  |

| Stratix IV                   | Final       |  |

| Stratix V                    | Preliminary |  |

#### Table 1–2. Device Family Support for 10GbE MAC

Table 1–3 shows the devices supported by the different configurations.

#### Table 1–3. Device Family Support for Configurations

| Configuration                                                                       | Arria V GT   | Arria V GZ   | Stratix V    |

|-------------------------------------------------------------------------------------|--------------|--------------|--------------|

| Multi-Speed 10M-10GbE MAC                                                           |              | $\checkmark$ | $\checkmark$ |

| Multi-Speed 10M-10GbE MAC with IEEE 1588v2                                          |              | $\checkmark$ | $\checkmark$ |

| 10GbE MAC with 10GBASE-R PHY                                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 10GbE MAC with 10GBASE-R PHY and IEEE 1588v2                                        | ✓ (1)        | ~            | ~            |

| Multi-Speed 10M-10GbE MAC with Backplane<br>Ethernet 10GBASE-KR PHY                 | _            | ~            | ~            |

| Multi-Speed 10M-10GbE MAC with Backplane<br>Ethernet 10GBASE-KR PHY and IEEE 1588v2 | _            | _            | _            |

| Multi-Speed 10M-10GbE MAC with 1G/10Gbps<br>Ethernet PHY                            | _            | ~            | $\checkmark$ |

| Multi-Speed 10M-10GbE MAC with 1G/10Gbps<br>Ethernet PHY and IEEE 1588v2            | _            | ~            | $\checkmark$ |

#### Note for Table 1–3:

(1) Supports only Arria V GT devices with speed grade of 3\_H3.

# **1.4. IP Core Verification**

To ensure compliance with the IEEE specification, Altera performs extensive validation of the 10GbE MAC IP core. Validation includes both simulation and hardware testing.

## **1.4.1. Simulation Environment**

Altera performs the following tests in the simulation environment:

- Directed tests that test all types and sizes of transaction layer packets and all bits of the configuration space.

- Error injection tests that inject errors in the link, transaction layer packets, and data link layer packets, and check for the proper response from the IP core.

- Random tests that test a wide range of traffic patterns across one or more virtual channels.

# 1.4.2. Compatibility Testing Environment

Altera has performed significant hardware testing of the 10GbE MAC IP core to ensure a reliable solution. The IP core has been tested with the following devices:

- Arria V, Stratix IV, and Stratix V

- Soft XAUI PHY

- Soft and hard 10GBASE-R PHY

- Hard Backplane Ethernet 10GBASE-KR PHY

- 1G/10Gbps Ethernet PHY

The IP core has passed all interoperability tests conducted by the UNH. In addition, Altera internally tests every release with the Spirent Ethernet and 10G testers.

# **1.5. Performance and Resource Utilization**

Table 1–4 provides the estimated performance and resource utilization of the 10GbE MAC for the Cyclone IV device family. The estimates are obtained by compiling the 10GbE MAC with the Quartus II software targeting a Cyclone IV (EP4CGX110DF31C7) device with speed grade –7.

To achieve your timing requirement in the Quartus II software, Altera recommends that you use multiple seeds in the Design Space Explorer to find the optimal Fitter settings for your design, follow the recommendations of the Timing Optimization Advisor, apply the Speed Optimization Technique and use the LogicLock regions.

| Settings                                                     | Logic Elements | Logic Registers | Memory Block (M9K) | f <sub>MAX</sub> (MHz) |

|--------------------------------------------------------------|----------------|-----------------|--------------------|------------------------|

| All options disabled                                         | 4,424          | 3,245           | 2                  | >156.25                |

| All options enabled with<br>memory-based statistics counters | 11,845         | 8,355           | 11                 | >156.25                |

Table 1–4. Cyclone IV Performance and Resource Utilization

Table 1–5 provides the estimated performance and resource utilization of the 10GbE MAC for the Stratix IV device family. The estimates are obtained by compiling the 10GbE MAC with the Quartus II software targeting a Stratix IV GX (EP4SGX70HF35C2) device with speed grade –2.

Table 1–5. Stratix IV Performance and Resource Utilization

| Settings                                                     | Combinational ALUTs | Logic Registers | Memory Block (M9K) | f <sub>MAX</sub> (MHz) |

|--------------------------------------------------------------|---------------------|-----------------|--------------------|------------------------|

| All options disabled                                         | 1,954               | 3,157           | 0                  | >156.25                |

| All options enabled with<br>memory-based statistics counters | 5,684               | 8,349           | 7                  | >156.25                |

| All options enabled with register-based statistics counters  | 8,135               | 10,117          | 3                  | >156.25                |

Table 1–6 provides the estimated performance and resource utilization of the 10GbE MAC for the Cyclone V device family. The estimates are obtained by compiling the 10GbE MAC with the Quartus II software targeting a Cyclone V GX (5CGXFC7D6F31C6) device with speed grade –6.

Table 1–6. Cyclone V Performance and Resource Utilization

| Settings                                                     | Combinational ALUTs | Logic Registers | Memory Block (M10K) | f <sub>MAX</sub> (MHz) |

|--------------------------------------------------------------|---------------------|-----------------|---------------------|------------------------|

| All options disabled                                         | 2,322               | 3,444           | 2                   | >156.25                |

| All options enabled with<br>memory-based statistics counters | 4,417               | 5,464           | 6                   | >156.25                |

| All options enabled with register-based statistics counters  | 6,867               | 7,113           | 2                   | >156.25                |

Table 1–7 provides the estimated performance and resource utilization of the 10GbE MAC for the Stratix V device family. The estimates are obtained by compiling the 10GbE MAC with the Quartus II software targeting a Stratix V GX (5SGXEA7H3F35C3) device with speed grade –3.

Table 1–7. Stratix V Performance and Resource Utilization for 10GbE MAC (Part 1 of 2)

| Settings                                                     | Combinational ALUTs | Dedicated Logic<br>Registers | Memory Block (M20K) | f <sub>MAX</sub> (MHz) |

|--------------------------------------------------------------|---------------------|------------------------------|---------------------|------------------------|

| All options disabled                                         | 2,001               | 3,077                        | 0                   | >156.25                |

| All options enabled with<br>memory-based statistics counters | 5,772               | 8,197                        | 7                   | >156.25                |

| All options enabled with register-based statistics counters  | 8,202               | 9,965                        | 3                   | >156.25                |

| Settings                                                              | Combinational ALUTs | Dedicated Logic<br>Registers | Memory Block (M20K) | f <sub>MAX</sub> (MHz) |

|-----------------------------------------------------------------------|---------------------|------------------------------|---------------------|------------------------|

| IEEE 1588v2 feature enabled with 2-step synchronization               | 4 007               | 5 004                        | 0                   |                        |

| <ul> <li>Timestamping is enabled</li> </ul>                           | 4,827               | 5,921                        | 8                   | >156.25                |

| ptp_1step is disabled                                                 |                     |                              |                     |                        |

| IEEE 1588v2 feature enabled with<br>1-step and 2-step synchronization |                     |                              |                     | 150.05                 |

| <ul> <li>Timestamping is enabled</li> </ul>                           | 6,822               | 7,926                        | 11                  | >156.25                |

| ptp_1step is disabled                                                 |                     |                              |                     |                        |

#### Table 1–7. Stratix V Performance and Resource Utilization for 10GbE MAC (Part 2 of 2)

Table 1–8 provides the estimated performance and resource utilization of the multi-speed 10M-10GbE MAC for the Stratix V device family. The estimates are obtained by compiling the 10M-10GbE MAC with the Quartus II software targeting a Stratix V GX (5SGXEA7H3F35C3) device with speed grade –3.

Table 1–8. Stratix V Performance and Resource Utilization for 10M-10GbE MAC

| Settings                                                     | Combinational ALUTs | Dedicated Logic<br>Registers | Memory Block (M20K) | f <sub>MAX</sub> (MHz) |

|--------------------------------------------------------------|---------------------|------------------------------|---------------------|------------------------|

| All options disabled                                         | 3,654               | 4,645                        | 7                   | >156.25                |

| All options enabled with<br>memory-based statistics counters | 4,877               | 5,797                        | 11                  | >156.25                |

| All options enabled with register-based statistics counters  | 7,313               | 7,544                        | 7                   | >156.25                |

# 2. Getting Started with Altera IP Cores

This chapter provides a general overview of the Altera IP core design flow to help you quickly get started with any Altera IP core. The Altera IP Library is installed as part of the Quartus II installation process. You can select and parameterize any Altera IP core from the library. Altera provides an integrated parameter editor that allows you to customize IP cores to support a wide variety of applications. The parameter editor guides you through the setting of parameter values and selection of optional ports. The following sections describe the general design flow and use of Altera IP cores.

# 2.1. Installation and Licensing

The Altera IP Library is distributed with the Quartus II software and downloadable from the Altera website (www.altera.com).

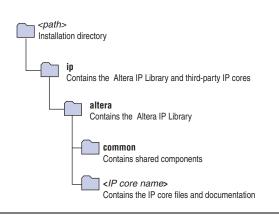

Figure 2–1 shows the directory structure after you install an Altera IP core, where *<path>* is the installation directory. The default installation directory on Windows is **C:\altera**\*<version number>*; on Linux it is **/opt/altera***<version number>*.

#### Figure 2–1. IP core Directory Structure

You can evaluate an IP core in simulation and in hardware until you are satisfied with its functionality and performance. Some IP cores require that you purchase a license for the IP core when you want to take your design to production. After you purchase a license for an Altera IP core, you can request a license file from the Altera Licensing page of the Altera website and install the license on your computer. For additional information, refer to *Altera Software Installation and Licensing*.

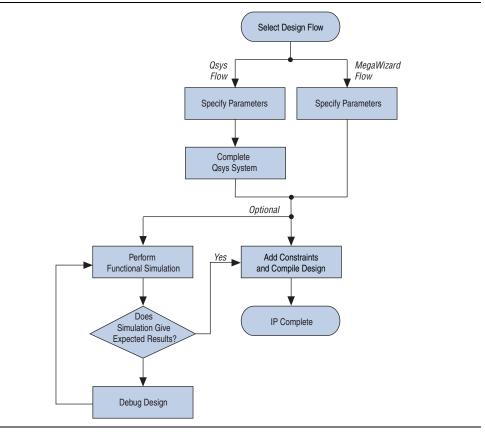

# 2.2. Design Flows

You can use the following flow(s) to parameterize Altera IP cores:

- "MegaWizard Plug-In Manager Flow"

- "Qsys System Integration Tool Design Flow"

Figure 2–2 shows the design flows for the MegaWizard Plug-In Manager and Qsys system integration tool.

# 2.3. MegaWizard Plug-In Manager Flow

The MegaWizard Plug-In Manager flow allows you to customize the 10GbE MAC IP core and manually integrate the function into your design.

## 2.3.1. Specifying Parameters

To specify the 10GbE MAC IP core parameters with the MegaWizard Plug-In Manager, follow these steps:

1. Open an existing Quartus II project or create a new project using the **New Project Wizard** available from the File menu.

- 2. In the Quartus II software, launch the **MegaWizard Plug-in Manager** from the Tools menu, and follow the prompts in the MegaWizard Plug-In Manager interface to create or edit a custom IP core variation.

- 3. In the **Installed Plug-Ins** list on page 2a of the MegaWizard Plug-In Manager interface, expand the **Interfaces** folder and then the **Ethernet** folder. Select **Ethernet 10G MAC**. Specify the type and name of the output file you want to create.

- 4. Specify the parameters on the **Parameter Settings** pages. For detailed explanations of these parameters, refer to "10GbE MAC Parameter Settings" on page 2–6.

- 5. Specify appropriate options in the wizard to generate a simulation model.

- Altera IP supports a variety of simulation models, including simulation-specific IP functional simulation models and encrypted RTL models. These are all cycle-accurate models. The models allow for fast functional simulation of your IP core instance using industry-standard VHDL or Verilog HDL simulators.

- For more information about functional simulation models for Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

- Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

- 6. Click **Finish**. The parameter editor generates the top-level HDL code for the 10GbE MAC IP core and a simulation directory which includes files for simulation.

- The **Finish** button may be unavailable until all parameterization errors listed in the messages window are corrected.

- 7. Click **Yes** if you are prompted to add the Quartus II IP File (.qip) to the current Quartus II project. You can also turn on **Automatically add Quartus II IP Files to all projects**.

You can now integrate your custom 10GbE MAC IP core instance in your design, simulate, and compile.

For information about the Quartus II software and the MegaWizard Plug-In Manager, refer to Quartus II Help.

### 2.3.2. Simulate the IP Core

You can simulate the 10GbE MAC IP core with the functional simulation model generated by the Quartus II software. To perform a successful simulation of the 10GbE MAC IP core using the MegaWizard Plug-In Manager flow, you are required to compile all files listed in the *<project directory>/<variation name>\_sim* output file. Otherwise, the simulation may fail.

• For more information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

# 2.4. Qsys System Integration Tool Design Flow

You can use the Qsys system integration tool to build a system that includes your customized IP core. You easily can add other components and quickly create a Qsys system. Qsys automatically generates HDL files that include all of the specified components and interconnections. In Qsys, you specify the connections you want. The HDL files are ready to be compiled by the Quartus II software to produce output files for programming an Altera device.

Figure 2–3 shows a high level block diagram of an example Qsys system.

#### Figure 2–3. Example Qsys System

- For more information about the Qsys system interconnect, refer to the *Qsys Interconnect* chapter in volume 1 of the *Quartus II Handbook* and to the *Avalon Interface Specifications*.

- **\*** For more information about the Qsys tool and the Quartus II software, refer to the *System Design with Qsys* section in volume 1 of the *Quartus II Handbook* and to Quartus II Help.

## 2.4.1. Specify Parameters

To specify parameters for your IP core using the Qsys flow, follow these steps:

- 1. Open an existing Quartus II project or create a new project using the **New Project Wizard** available from the File menu.

- 2. On the Tools menu, click **Qsys**.

- 3. On the **Component Library** tab, expand the **Interfaces Protocols** list and then the **Ethernet** list. Double-click **Ethernet 10G MAC** to add it to your system. The relevant parameter editor appears.

- 4. Specify the required parameters in the Qsys tool. For detailed explanations of these parameters, refer to "10GbE MAC Parameter Settings" on page 2–6.

- 5. Click **Finish** to complete the IP core instance and add it to the system.

## 2.4.2. Complete the Qsys System

To complete the Qsys system, follow these steps:

- 1. Add and parameterize any additional components.

- 2. Connect the components using the Connections panel on the **System Contents** tab.

- 3. In the **Export As** column, enter the name of any connections that should be a top-level Qsys system port.

- 4. If you intend to simulate your Qsys system, on the **Generation** tab, turn on one or more options under **Simulation** to generate desired simulation files.

- 5. If you want to generate synthesis RTL files, turn on **Create HDL design files for** synthesis.

- 6. Click **Generate** to generate the system. Qsys generates the system and produces the *<system name>.qip* file that contains the assignments and information required to process the IP core or system in the Quartus II Compiler.

- 7. In the Quartus II software, click **Add/Remove Files in Project** on the Project menu and add the **.qip** file to the project.

- 8. Compile your design in the Quartus II software.

## 2.4.3. Simulate the System

During system generation, Qsys generates a functional simulation model which you can use to simulate your system easily in any Altera-supported simulation tool.

- **For information about the latest Altera-supported simulation tools, refer to the** *Quartus II Software Release Notes.*

- **For** general information about simulating Altera IP cores, refer to *Simulating Altera Designs* in volume 3 of the *Quartus II Handbook*.

- **Tor** information about simulating Qsys systems, refer to the *System Design with Qsys* section in volume 1 of the *Quartus II Handbook*.

# 2.5. 10GbE MAC Parameter Settings

You customize the 10GbE MAC by specifying the parameters on the MegaWizard Plug-in Manager, or Qsys in the Quartus II software. Table 2–1 describes the parameters and how they affect the behavior of the IP core.

#### Table 2–1. 10GbE Parameters

| Parameter                         | Description                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Speed select for 10G MAC          | Use this parameter to select the speed options. By default, the <b>10G MAC</b> option is selected. Select <b>Enable 1G/10G MAC</b> to implement the 10-Gbps and 1-Gbps MAC; select <b>Enable Multi-Speed 10M-10Gb MAC</b> to implement the 10-Mbps, 100-Mbps, 1 Gbps, and 10-Gbps MAC.                                                    |  |

| Preamble pass-through mode        | Turn on this parameter to enable the preamble passthrough mode. To enable the preamble passthrough mode, you must turn on this parameter and set the tx_preamble_control, rx_lane_decoder_preamble_control, and rx_preamble_inserter_control registers to 1.                                                                              |  |

|                                   | This parameter is disabled if you selected <b>Enable 1G/10G MAC</b> .                                                                                                                                                                                                                                                                     |  |

| Priority-based flow control (PFC) | Turn on this parameter to enable PFC. Refer to "Priority-Based Flow Control" on page 7–19 for more information on PFC and its operations.                                                                                                                                                                                                 |  |

| Number of PFC priorities          | Indicates the number of PFC priority levels that the 10GbE MAC IP core supports. The valid range is from 2 to 8. This option is enabled only if you turn on the <b>Priority-based flow control (PFC)</b> parameter.                                                                                                                       |  |

| Datapath option                   | Use this parameter to select the datapath option that determines the MAC variation to instantiate. By default, the <b>TX &amp; RX</b> option is selected. The default datapath instantiates the MAC TX and MAC RX blocks. Selecting <b>TX only</b> instantiates the MAC TX block; selecting <b>RX only</b> instantiates the MAC RX block. |  |

| Supplementary address             | Turn on this parameter to enable supplementary addresses. To enable supplementary addresses, you must turn on this parameter and set the EN_SUPP0/1/2/3 bits in the rx_frame_control register to 1.                                                                                                                                       |  |

| CRC on transmit path              | Turn on this parameter to calculate and insert CRC on the transmit datapath. To compute and insert CRC on the transmit datapath, you must turn on this parameter and set the tx_crcins_control[1] register bit to 1.                                                                                                                      |  |

| Statistics collection             | Turn on this parameter to collect statistics on the transmit and receive datapaths.                                                                                                                                                                                                                                                       |  |

|                                   | When you turn on <b>Statistics collection</b> , the default implementation of the statistics counters is <b>Memory-based</b> .                                                                                                                                                                                                            |  |

| Statistics counters               | Use <b>Memory-based</b> statistics counters to free up the logic elements (the MAC does not clear the statistic counters after the counters are read); <b>Register-based</b> statistics counters to free up the memory (the MAC clears the statistic counters after the counters are read).                                               |  |

|                                   | Register-based statistics counters are not supported for Cyclone IV GX devices.                                                                                                                                                                                                                                                           |  |

| Enable time stamping              | Turn on this parameter to enable time stamping on the transmitted and received frames.                                                                                                                                                                                                                                                    |  |

| Enable PTP 1-step clock support   | Turn on this parameter to insert time stamp on PTP messages for 1-step clock based<br>on the TX Egress Timestamp Insert Control interface.                                                                                                                                                                                                |  |

|                                   | This parameter is disabled if you do not turn on <b>Enable time stamping</b> .                                                                                                                                                                                                                                                            |  |

| Timestamp fingerprint width       | Use this parameter to set the width in bits for the time stamp fingerprint on the TX path. The default value is 4 bits.                                                                                                                                                                                                                   |  |

|                                   |                                                                                                                                                                                                                                                                                                                                           |  |

# 3. 10GbE MAC Design Examples

You can use the following 10GbE design examples and testbenches to help you get started with the 10GbE MAC IP core and use the core in your design:

- 10GbE MAC with XAUI PHY

- 10GbE MAC with 10GBASE-R PHY

XAUI PHY and 10GBASE-R PHY do not support Stratix III devices.

## 3.1. Software and Hardware Requirements

Altera uses the following hardware and software to test the 10GbE design examples and testbenches:

- Quartus II software 13.1

- Stratix IV GX FPGA development kit (for XAUI PHY)

- Transceiver Signal Integrity development kit, Stratix IV GT Edition (for 10GBASE-R PHY)

- ModelSim<sup>®</sup>-AE 6.6c, ModelSim-SE 6.6c or higher

**For more information on the development kits, refer to the following documents:**

- Stratix IV GX Development Kit User Guide

- Stratix IV GX Development Kit Reference Manual

- Transceiver Signal Integrity Development Kit, Stratix IV GT Edition User Guide

- Transceiver Signal Integrity Development Kit, Stratix IV GT Edition Reference Manual

# 3.2. 10GbE Design Example Components

You can use the 10GbE MAC IP core design example to simulate a complete 10GbE design in an Altera FPGA. You can compile the design example using the simulation files generated by the Quartus II software and program the targeted Altera device after a successful compilation.

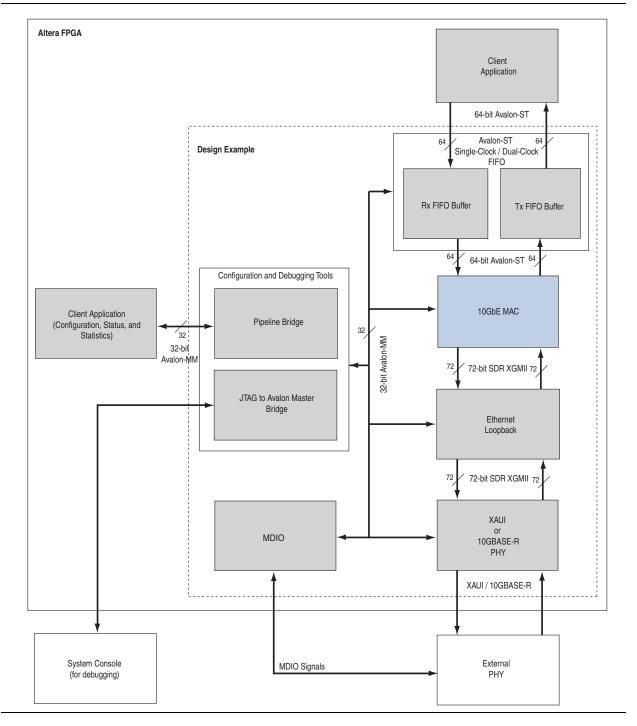

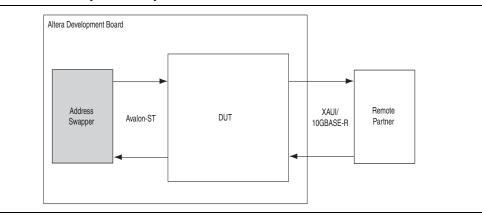

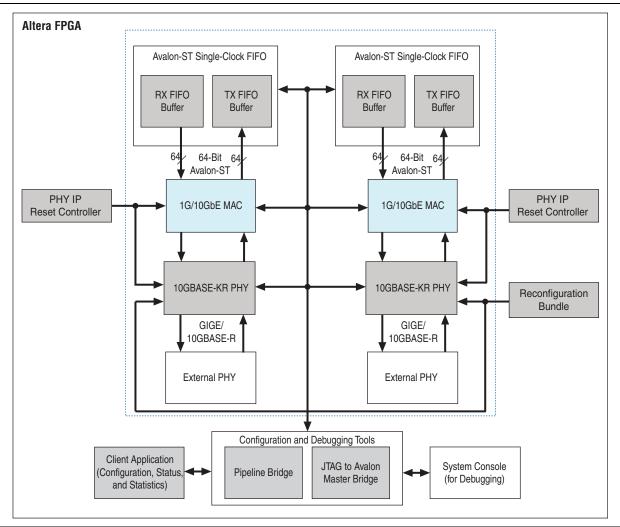

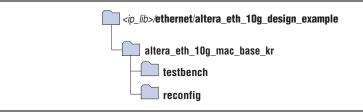

Figure 3–1 shows the block diagram of the 10GbE design examples.

Figure 3–1. 10GbE Design Example Block Diagram

The design example comprises the following components:

- 10GbE Ethernet MAC—the MAC IP core with default settings. This IP core includes memory-based statistics counters.

- XAUI PHY or 10GBASE-R PHY—the PHY IP core with default settings. The XAUI PHY is set to **Hard XAUI** by default.

- Ethernet Loopback— the loopback module provides a mechanism for you to verify the functionality of the MAC and PHY. Refer to Section 3.2.0.1, Ethernet Loopback Module for more information about this module.

- RX and TX FIFO buffers—Avalon-ST Single-Clock or Dual-Clock FIFO cores that buffer receive and transmit data between the MAC and client. These FIFO buffers are 64 bits wide and 512 bits deep. The default configuration is Avalon-ST Single-Clock FIFO, which operates in store and forward mode and you can configure it to provide packet-based flushing when an error occurs.

- To enable the Avalon-ST Single-Clock FIFO to operate in cut through mode, turn off the **Use store and forward** parameter in the **Avalon-ST Single Clock FIFO** parameter editor.

- Configuration and debugging tools—provides access to the registers of the following components via the Avalon Memory-Mapped (Avalon-MM) interface: MAC, MDIO, Ethernet loopback, PHY, and FIFO buffers. The provided testbench includes an Avalon driver which uses the pipeline bridge to access the registers. You can use the system console to access the registers via the JTAG to Avalon Master Bridge core when verifying the design in the hardware.

**To learn more about the components, refer to the respective documents:**

- XAUI PHY and 10GBASE-R PHY, refer to *Altera Transceiver PHY IP Core User Guide*.

- Avalon-ST Single-Clock or Dual-Clock FIFO, JTAG to Avalon Master Bridge, and MDIO cores, refer to *Embedded Peripherals IP User Guide*.

- Pipeline bridge, refer to Avalon Memory-Mapped Bridges in volume 4 of the Quartus II Handbook.

- System Console, refer to *Analyzing and Debugging Designs with the System Console* in volume 3 of the *Quartus II Handbook*.

#### 3.2.0.1. Ethernet Loopback Module

You can enable one of the following loopback types:

Local loopback—turn on this loopback to verify the functionality of the MAC during simulation. When you enable the local loopback, the Ethernet loopback module takes the transmit frame from the MAC XGMII TX and loops it back to the MAC XGMII RX datapath. During this cycle, the loopback module also forwards the TX frame to the PHY. While the local loopback is turned on, the loopback module ignores any frame it receives from the PHY.

• Line loopback—turn on this loopback to verify the functionality of the PHY when verifying the design example in hardware. When you enable the line loopback, the Ethernet loopback module takes the XGMII RX signal received from the PHY and loops it back to the PHY's XGMII TX signal. During this cycle, the loopback module also forwards the XGMII RX signal to the MAC. While the line loopback is turned on, the loopback module ignores any frame transmitted from the MAC.

Table 3–1 describes the registers you can use to enable or disable the desired loopback.

#### Table 3–1. Loopback Registers

| Byte Offset | Register       | Description                                                       |  |

|-------------|----------------|-------------------------------------------------------------------|--|

| 0x00        | line loopback  | Set this register to 1 to enable line loopback; 0 to disable it.  |  |

| 0x04        | Reserved       | _                                                                 |  |

| 0x08        | local loopback | Set this register to 1 to enable local loopback; 0 to disable it. |  |

### 3.2.0.2. Base Addresses

Table 3–2 lists the design example components that you can reconfigure to suit your verification objectives. To reconfigure the components, write to their registers using the base addresses listed in the table and the register offsets described in the components' user guides. Refer to Table 3–1 for the Ethernet loopback registers.

#### Table 3–2. Base Addresses of Design Example Components

| Component                             | Base Address |

|---------------------------------------|--------------|

| 10GbE MAC                             | 0x000        |

| XAUI or 10GBASE-R PHY                 | 0x40000      |

| MDIO                                  | 0X10000      |

| Ethernet loopback                     | 0x10200      |

| RX FIFO (Avalon-ST Single-Clock FIFO) | 0x10400      |

| TX FIFO (Avalon-ST Single-Clock FIFO) | 0x10600      |

P

This design example uses a 19-bit width address bus to access the base address of components other than the MAC.

# 3.3. 10GbE Design Example Files

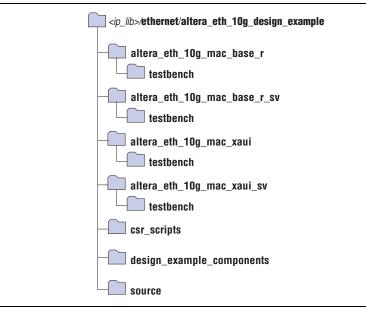

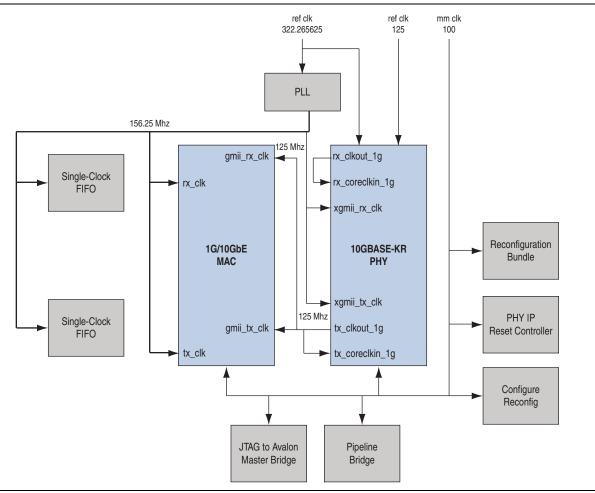

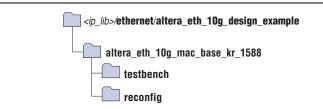

Figure 3–2 shows the directory structure for the design examples and testbenches. The ..\csr\_script directory contains the design example script files.

Table 3–3 lists the design example files. For the description of testbench files, refer to Table 3–5 on page 3–10.

Table 3–3. 10GbE Design Example Files (Part 1 of 2)

| File Name                                | Description                                                                                                                                                             |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| setup_proj.tcl                           | A Tcl script that creates a new Quartus II project<br>and sets up the project environment for your<br>design example. Not applicable for Stratix V<br>design.           |

| setup_proj_sv.tcl                        | A Tcl script that creates a new Quartus II project<br>for Stratix V design and sets up the project<br>environment for your design example.                              |

| altera_eth_10g_design_mac_xaui.qsys      | A Qsys file for the 10GbE MAC and XAUI PHY design example. The PHY is set to hard XAUI by default.                                                                      |

| altera_eth_10g_design_mac_xaui_sv.qsys   | A Qsys file for the 10GbE MAC and XAUI PHY<br>design example with the Quartus II software<br>targeting the Stratix V device. The PHY is set to<br>hard XAUI by default. |

| altera_eth_10g_design_mac_base_r.qsys    | A Qsys file for the 10GbE MAC and 10GBASE-R<br>PHY design example.                                                                                                      |

| altera_eth_10g_design_mac_base_r_sv.qsys | A Qsys file for the 10GbE MAC and 10GBASE-R<br>PHY design example with the Quartus II software<br>targeting the Stratix V device.                                       |

| File Name                                                                                                                                                                                         | Description                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| setup_SIVGX230C2ES.tcl         A Tcl script that sets the pin assign standards for the Stratix IV GX FP development board. Use this Tcl s 10GbE MAC with XAUI PHY design                          |                                                                                                                                                                                                            |

| setup_EP4S100G5H40I3.tcl       A Tcl script that sets the pin assignmen standards for the Stratix IV GT Signal I development board. Use this Tcl script 10GbE MAC with 10GBASE-R PHY des example. |                                                                                                                                                                                                            |

| setup_5SGXEA7N2F40C2ES.tcl                                                                                                                                                                        | A Tcl script that sets the pin assignments and I/O<br>standards for the Stratix V GX Signal Integrity<br>development board. Use this Tcl script for the<br>10GbE MAC with 10GBASE-R PHY design<br>example. |

| top.sdc                                                                                                                                                                                           | The Quartus II SDC constraint file for use with the TimeQuest timing analyzer.                                                                                                                             |

| top.v                                                                                                                                                                                             | The top-level entity file of the design example for verification in hardware. Not applicable for Stratix V design.                                                                                         |

| top_sv.v                                                                                                                                                                                          | The top-level entity file of the design example—<br>with the Quartus II software targeting the<br>Stratix V device—for verification in hardware.                                                           |

| common.tcl                                                                                                                                                                                        | A Tcl script that contains basic functions based<br>on the system console APIs to access the<br>registers through the Avalon-MM interface.                                                                 |

| config.tcl                                                                                                                                                                                        | A Tcl script that configures the design example.                                                                                                                                                           |

| csr_pkg.tcl                                                                                                                                                                                       | A Tcl script that maps address to the Avalon-MM control registers. The script contains APIs which is used by <b>config.tcl</b> and <b>show_stats.tcl</b> .                                                 |

| show_stats.tcl                                                                                                                                                                                    | A Tcl script that displays the MAC statistics counters.                                                                                                                                                    |

| altera_eth_10g_design_example_hw.tcl         A hardware Tcl script that contains t composition of the Ethernet system.                                                                            |                                                                                                                                                                                                            |

Table 3–3. 10GbE Design Example Files (Part 2 of 2)

# 3.4. Creating a New 10GbE Design

You can use the Quartus II software to create a new 10GbE design. Altera provides a customizable Qsys design example file to facilitate the development of your 10GbE design. Follow these steps to create the design:

- Copy the respective design example directory to your preferred project directory: altera\_eth\_10g\_mac\_xaui or altera\_eth\_10g\_mac\_base\_r from <ip library>/ethernet/altera\_eth\_10g\_design\_example.

- 2. Launch the Quartus II software and open the **top.v** file from the project directory.

3. Open the Quartus II Tcl Console window by pointing to **Utility Windows** on the View menu and then selecting **Tcl Console**. In the Quartus II Tcl Console window, type the following command to set up the project environment:

```

source setup proj.tcl←

```

- 4. Load the pin assignments and I/O standards for the development board:

- For the 10GbE MAC with XAUI PHY design example, type the following command:

```

source setup SIVGX230C2ES.tcl←

```

This command assigns the XAUI serial interface to the pins that are connected to the HSMC Port A of the Stratix IV GX development board.

• For the 10GbE MAC with 10GBASE-R design example, type the following command:

source setup\_EP4S100G2F40I1.tcl←

This command assigns the 10GBASE-R serial interface to the pins that are connected to the SMA connectors (J38 to J41) of the Stratix IV GT development board.

- For more information about the development boards, refer to the respective reference manuals: *Stratix IV GX Development Kit Reference Manual* or *Transceiver Signal Integrity Development kit, Stratix IV GT Edition Reference Manual*.

- 5. Launch Qsys from the Tools menu and open the altera\_eth\_10g\_mac\_base\_r.qsys or altera\_eth\_10g\_mac\_xaui.qsys file. For design targeting the Stratix V device family, use the altera\_eth\_10g\_mac\_base\_r\_sv.qsys or altera\_eth\_10g\_mac\_xaui\_sv.qsys file.

- By default, the design example targets the Stratix IV device family. To change the target device family, click on the **Project Settings** tab and select the desired device from the **Device family** list.

- 6. Turn off the additional module under the **Use** column if your design does not require them. This action disconnects the module from the 10GbE system.

- 7. Double-click eth\_10g\_design\_example\_0 to launch the parameter editor.

- 8. Specify the required parameters in the parameter editor. For detailed explanations of these parameters, refer to "10GbE Design Example Parameter Settings" on page 3–8.

- 9. Click Finish.

- 10. On the **Generation** tab, select either a Verilog HDL or a VHDL simulation model and make sure that the **Create HDL design files for synthesis** option is turned on.

- 11. Click Generate to generate the simulation and synthesis files.

# **3.5. 10GbE Design Example Parameter Settings**

You can customize the 10GbE design example by specifying the parameters using the parameter editor. Table 3–4 describes these parameters.

| Name                                                                                                                                | Value Description                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration                                                                                                                       |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MDIO                                                                                                                                | MDIO<br>None                      | Specifies whether the Ethernet system requires a MDIO core to access the external PHY device management registers for configuration and management purposes.                                                                                                                                                                                                                                                                                                                    |

| PHY IP                                                                                                                              | XAUI PHY<br>10GBase-R PHY<br>None | Specifies which protocol-specific PHY IP core to use for the<br>Ethernet system. For XAUI PHY, you can choose to implement the<br>system in soft or hard logic.                                                                                                                                                                                                                                                                                                                 |

| Avalon-ST Single Clock FIFO<br>Avalon-ST Dual Clock FIFO<br>FIFO Avalon-ST Single Clock FIFO<br>+ Avalon-ST Dual Clock FIFO<br>None |                                   | Specifies which FIFO buffer to use for the Ethernet system. The<br>Avalon-ST Single Clock FIFO operates with a common clock for the<br>input and output ports while the Avalon-ST Dual Clock FIFO<br>operates with independent clocks for the input and output ports.<br>You cannot enable a different FIFO option for TX datapath and RX<br>datapath. If you select <b>Avalon-ST Single Clock FIFO</b> , the design<br>includes single clock FIFO at both TX and RX datapaths. |

#### Table 3–4. Design Example Parameters

The parameter values you select on **Configuration** tab correspond with the other tabs that require further parameterization. You should only parameterize the components you selected and omit the others. Editing the component parameters that were not selected may cause the system generation to fail.

- **Tor** For more information about the parameter settings of other components, refer to the respective documents:

- 10GbE MAC, refer to "10GbE MAC Parameter Settings" on page 2–6.

- Avalon-ST Single-Clock or Dual-Clock FIFO and MDIO core, refer to *Embedded Peripherals IP User Guide*.

- XAUI PHY and 10GBASE-R PHY, refer to *Altera Transceiver PHY IP Core User Guide*.

# 3.6. 10GbE Testbenches

Altera provides testbenches for you to verify the design examples. The following sections in this document describe the testbench, its components, and use.

### 3.6.1. 10GbE Testbench

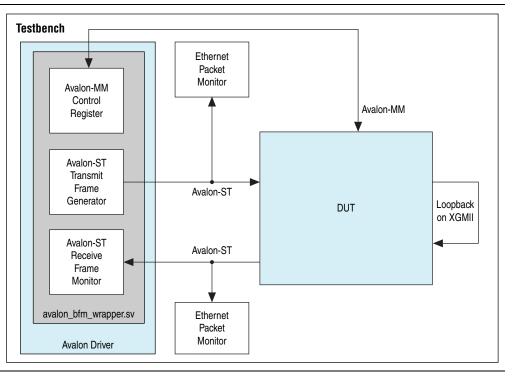

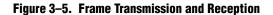

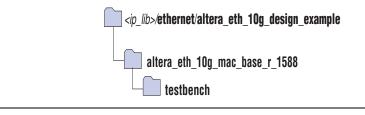

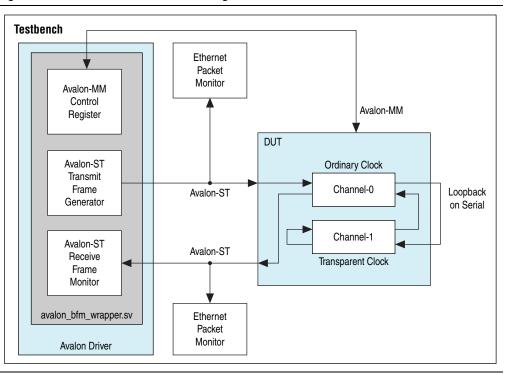

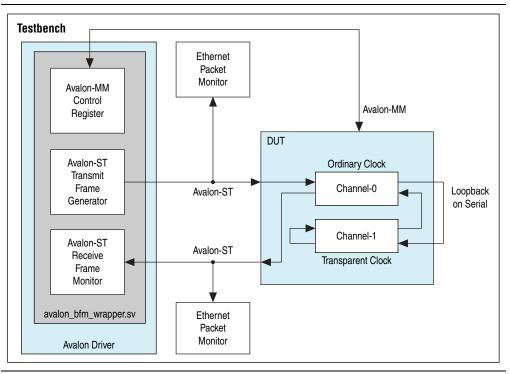

The testbenches operate in loopback mode. Figure 3–3 shows the flow of the packets.

Figure 3–3. Testbench Block Diagram

## 3.6.2. 10GbE Testbench Component

The 10GbE testbench comprises the following modules:

- Device under test (DUT)—the design example.

- Avalon driver—uses Avalon-ST bus functional models (BFMs) to exercise the transmit and receive paths. The driver also utilizes the Avalon-MM BFM to access the Avalon-MM interfaces of the design example components.

- Packet monitors—monitors the transmit and receive datapaths, and displays the frames in the simulator console.

### 3.6.3. 10GbE Testbench Files

The following directories contain the 10GbE testbench files which are in clear text:

- 10GbE MAC and XAUI PHY testbench—<*ip library*>/ethernet/ altera\_eth\_10g\_design\_example/altera\_eth\_10g\_mac\_xaui/testbench

- 10GbE MAC and 10GBASE-R PHY testbench— <*ip library*>/ethernet/ altera\_eth\_10g\_design\_example/altera\_eth\_10g\_mac\_base\_r/testbench

Table 3–5 describes the files that implement the testbench.

| Tahle | 3-5  | <b>Testbench Files</b> |

|-------|------|------------------------|

| IaNIC | J-J. | Ισοιμσιισιι Ι Πσο      |

| File Name                       | Description                                                                                                                                                                                                                                         |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| avalon_bfm_wrapper.sv           | A wrapper for the Avalon BFMs that the <b>avalon_driver.sv</b> file uses.                                                                                                                                                                           |  |

| avalon_driver.sv                | A SystemVerilog HDL driver that utilizes the BFMs to exercise the transmit and receive path, and access the Avalon-MM interface.                                                                                                                    |  |

| avalon_if_params_pkg.sv         | A SystemVerilog HDL testbench that contains parameters to configure the BFMs. Because the configuration is specific to the DUT, you must not change the contents of this file.                                                                      |  |

| avalon_st_eth_packet_monitor.sv | A SystemVerilog HDL testbench that monitors the Avalon-ST transmit and receive interfaces.                                                                                                                                                          |  |

| eth_mac_frame.sv                | A SystemVerilog HDL class that defines the Ethernet frames.<br>The <b>avalon_driver.sv</b> file uses this class.                                                                                                                                    |  |

| eth_register_map_params_pkg.sv  | A SystemVerilog HDL package that maps addresses to the Avalon-MM control registers.                                                                                                                                                                 |  |

| tb_run.tcl                      | A Tcl script that starts a simulation session in the ModelSim simulation software. Not applicable for Stratix V design.                                                                                                                             |  |

| tb_run_sv.tcl                   | A Tcl script that starts a simulation session in the ModelSim simulation software for Stratix V design only.                                                                                                                                        |  |

| tb.sv                           | The top-level testbench file. This file includes the customized<br>10GbE MAC which is the device under test (DUT), a client<br>packet generator, and a client packet monitor along with<br>other logic blocks. Not applicable for Stratix V design. |  |

| tb_sv.sv                        | The top-level testbench file for Stratix V design only. This file includes the customized 10GbE MAC which is the device under test (DUT), a client packet generator, and a client packet monitor along with other logic blocks.                     |  |

| wave.do                         | A signal tracing macro script to be used with the ModelSim simulation software to display testbench signals.                                                                                                                                        |  |

## 3.6.4. 10GbE Testbench Simulation Flow

Upon a simulated power-on reset, each testbench performs the following operations:

- 1. Initializes the DUT by configuring the following options via the Avalon-MM interface:

- a. In the MAC, enables address insertion on the transmit path and sets the transmit primary MAC address to EE-CC-88-CC-AA-EE.

- b. In the TX and RX FIFO (Avalon-ST Single Clock FIFO core), enables drop on error.

- 2. Starts packet transmission. The testbench sends a total of eight packets:

- a. 64-byte basic Ethernet frame

- b. Pause frame

- c. 1518-byte VLAN frame

- d. 1518-byte basic Ethernet frame

- e. 64-byte stacked VLAN frame

- f. 500-byte VLAN frame

- g. Pause frame

- h. 1518-byte stacked VLAN frame

- 3. Ends the transmission and displays the MAC statistics in the transcript pane.

## 3.6.5. Simulating the 10GbE Testbench with the ModelSim Simulator

To use the ModelSim simulator to simulate the testbench design, follow these steps:

- Copy the respective design example directory to your preferred project directory: altera\_eth\_10g\_mac\_xaui or altera\_eth\_10g\_mac\_base\_r from <ip library>/ethernet/altera\_eth\_10g\_design\_example.

- 2. The design example and testbench files are set to read only. Altera recommends that you turn off the read-only attribute of all design example and testbench files.

- 3. Launch the Quartus II software and open the **top.v** file from the project directory.

- 4. Open the Quartus II Tcl Console window by pointing to **Utility Windows** on the View menu and then selecting **Tcl Console**. In the Quartus II Tcl Console window, type the following command to set up the project environment:

```

source setup_proj.tcl←

```

- 5. Launch Qsys from the Tools menu and open altera\_eth\_10g\_mac\_base\_r.qsys or altera\_eth\_10g\_mac\_xaui.qsys in the File menu.

- 6. For the 10GbE MAC with XAUI design example, the default setting of the XAUI PHY is **Hard XAUI**. Follow these steps if you want to set the PHY to **Soft XAUI**:

- a. Double-click the XAUI PHY module to open the parameter editor.

- b. On the General Options tab, select Soft XAUI for XAUI Interface Type.

- 7. On the Generation tab, select Verilog simulation model.

- 8. Click Generate to generate the system.Launch the ModelSim simulator software.

- 9. Change the working directory to *<project directory*>/*<design example directory*>/**testbench** in the **File** menu.

- 10. Run the following command to set up the required libraries, compile the generated IP Functional simulation model, and exercise the simulation model with the provided testbench:

```

do tb run.tcl←

```

The ModelSim transcript pane in Main window displays messages from the testbench reflecting the current task being performed.

Upon a successful simulation, the simulator displays the following RX Statistics and TX Statistics:

```

# framesOK = 8

\# framesErr = 0

\# framesCRCErr = 0

\# octetsOK = 5138

# pauseMACCtrlFrames = 2

\# if Errors = 0

\# unicastFramesOK = 4

# unicastFramesErr = 0

# multicastFramesOK = 1

# multicastFramesErr = 0

# broadcastFramesOK = 1

# broadcastFramesErr = 0

# etherStatsOctets = 5310

# etherStatsPkts = 8

# etherStatsUndersizePkts = 0

# etherStatsOversizePkts = 0

# etherStatsPkts64Octets = 4

# etherStatsPkts65to127Octets = 0

# etherStatsPkts128to2550ctets = 0

# etherStatsPkts256to5110ctet = 1

# etherStatsPkts512to1023Octets = 0

# etherStatsPkts1024to1518Octets = 3

# etherStatsPkts15190toXOctets = 0

# etherStatsFragments = 0

# etherStatsJabbers = 0

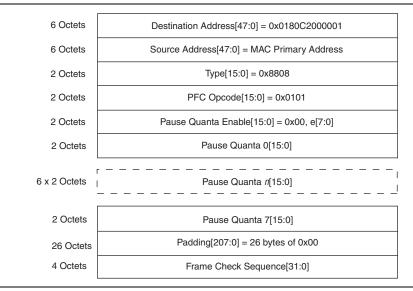

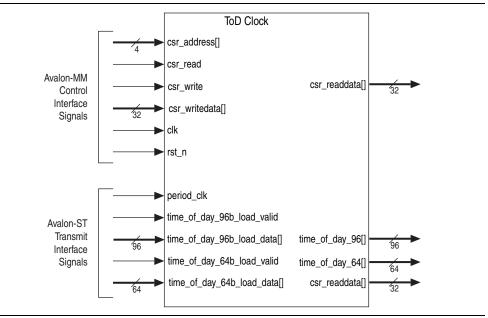

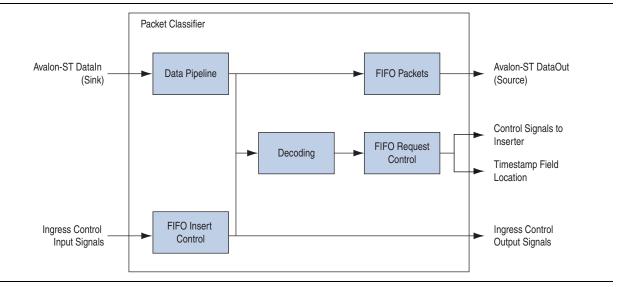

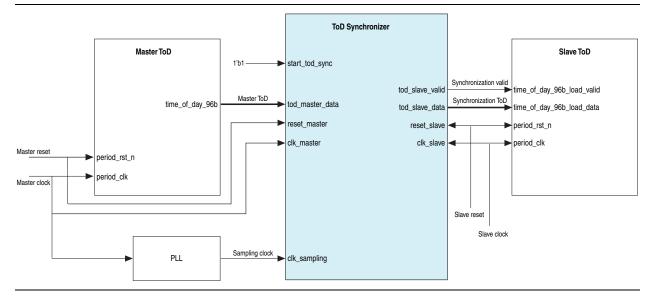

# etherStatsCRCErr = 0