- High-Performance Static CMOS Technology

- Includes the '320C2xLP Core CPU

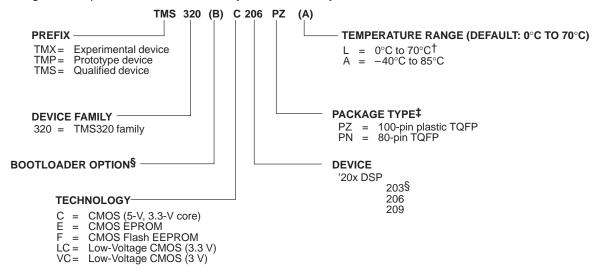

- TMS320C206, TMS320LC206 are Members of the 'C20x/'C2000 Platform Which Also Includes the TMS320C203/LC203 and TMS320F206 Devices

- Instruction-Cycle Time 25 ns at 3.3 V

- Source Code Compatible With TMS320C25 and other '20x Devices

- Upwardly Code-Compatible With TMS320C5x Devices

- Four External Interrupts

- TMS320C206, 5-V I/O (3.3-V core)

- TMS320LC206, 3.3-V core and I/O

- TMS320C206, TMS320LC206 Integrated Memory:

- 544 × 16 Words of On-Chip Dual-Access Data RAM

- 32K × 16 Words of On-Chip ROM

- 4K × 16 Words of On-Chip Single-Access Program/Data RAM

- 224K × 16-Bit Maximum Addressable External Memory Space

- 64K Program

- 64K Data

- 64K Input/Output (I/O)

- 32K Global

- 32-Bit Arithmetic Logic Unit (ALU) Accumulator

- 16 × 16-Bit Multiplier With a 32-Bit Product

- Block Moves from Data and Program Space

- TMS320C206, TMS320LC206 Peripherals:

- On-Chip 20-Bit Timer

- On-Chip Software-Programmable Wait-State (0 to 7) Generator

- On-Chip Oscillator

- On-Chip Phase-Locked Loop (PLL)

- Six General-Purpose I/O Pins

- Full-Duplex Asynchronous Serial Port (UART)

- Enhanced Synchronous Serial Port (ESSP) With Four-Level-Deep FIFOs

- Input Clock Options

- Options: Multiply-by-One, -Two, or -Four, and Divide-by-Two ( $\times$ 1,  $\times$ 2,  $\times$ 4, and  $\div$ 2)

- Support of Hardware Wait States

- Power Down IDLE Mode

- IEEE 1149.1<sup>†</sup>-Compatible Scan-Based Emulation

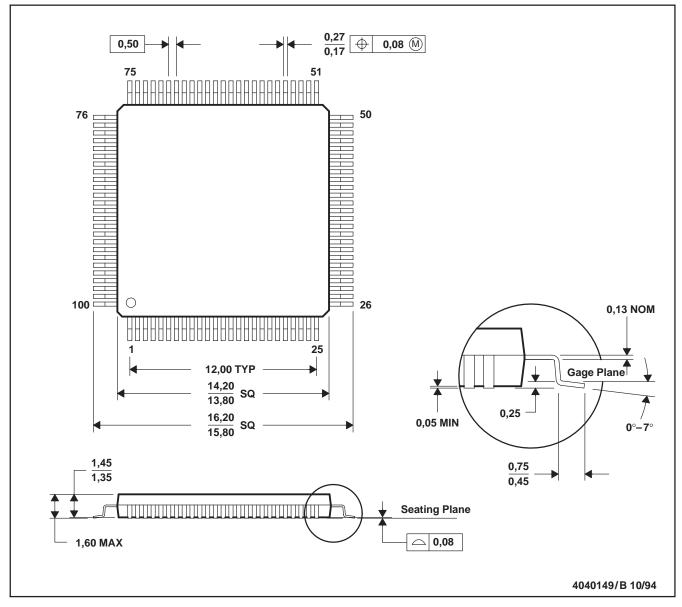

- TMS320C206, TMS320LC206 100-Pin PZ Package, Small Thin Quad Flat Package (TQFP)

- Industrial Temperature Version Planned, (-40°C to 85°C)

### description

The Texas Instruments (TI™) TMS320C206‡ and TMS320LC206‡ digital signal processors (DSPs) are fabricated with static CMOS integrated-circuit technology. The architectural design is based upon that of the TMS320C20x series and is optimized for low-power operation. The combination of advanced Harvard architecture, on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed of the 'C206.

The 'C206 offers these advantages:

- Enhanced TMS320 architectural design for increased performance and versatility

- Advanced integrated-circuit processing technology for increased performance

- 'C206 devices are pin- and code-compatible with 'C203 and 'F206 devices.

- Source code for the 'C206 DSPs is software-compatible with the 'C1x and 'C2x DSPs and is upwardly compatible with fifth-generation DSPs ('C5x)

- New static-design techniques for minimizing power consumption and increasing radiation tolerance

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†IEEE Standard 1149.1-1990, IEEE Standard Test-Access Port

‡ Device numbers are hereafter referred to in the data sheet as 'C206, unless otherwise specified.

TI is a trademark of Texas Instruments Incorporated.

Copyright © 1999, Texas Instruments Incorporated

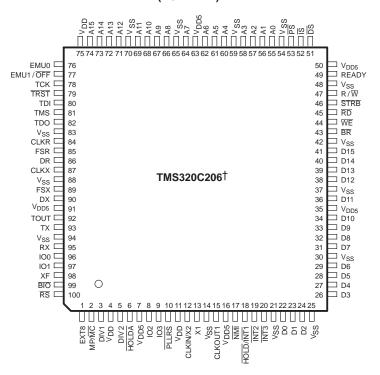

# PZ PACKAGE (TOP VIEW)

† VDD5 pins 7, 16, 35, 50, 63, and 91 represent I/O supply voltage.

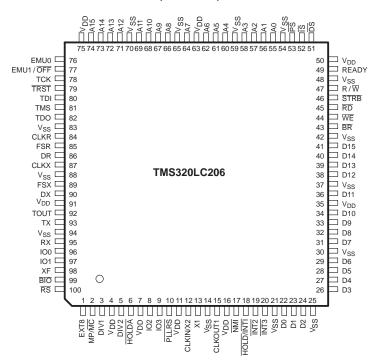

#### PZ PACKAGE (TOP VIEW)

### device features

Table 1 shows the capacity of on-chip RAM and ROM, the number of serial and parallel I/O ports, the execution time of one machine cycle, and the type of package with total pin count of the TMS320C206 and TMS320LC206 devices.

Table 1. Characteristics of the TMS320C206 and TMS320LC206 Processors

| 'x206<br>DEVICES | ON-CI | HIP MEMORY            | (16-BIT W | ORDS)           |           |          |                 |               |                      |

|------------------|-------|-----------------------|-----------|-----------------|-----------|----------|-----------------|---------------|----------------------|

|                  | RAM   |                       | ROM       | FLASH<br>EEPROM | I/O PORTS |          | POWER<br>SUPPLY | CYCLE<br>TIME | PACKAGE<br>TYPE WITH |

|                  | DATA  | DATA/<br>PROG         | PROG      | PROG            | SERIAL    | PARALLEL | (V)             | (ns)          | PIN COUNT            |

| TMS320C206       | 288†  | 4K + 256 <sup>‡</sup> | 32K       | -               | 2         | 64K      | 5 (3.3 core)    | 25            | 100-pin TQFP         |

| TMS320LC206      | 288†  | 4K + 256 <sup>‡</sup> | 32K       | _               | 2         | 64K      | 3.3             | 25            | 100-pin TQFP         |

<sup>†</sup>On-chip RAM space B1 (256 words) and B2 (32 words) can be used as data memory only.

<sup>‡</sup> On-chip RAM space B0 (256 words) can be used either in data space or program space depending on the value of the CNF bit in the ST1 register. On-chip SARAM (4K) can be mapped in program space, data space, or both.

# TMS320C206, TMS320LC206 Terminal Functions

| TERMI<br>NAME                                                                                | NAL<br>NO.                                                                                   | TYPE <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IVANIL                                                                                       | 110.                                                                                         |                   | DATA AND ADDRESS BUSES                                                                                                                                                                                                                                                                                                                                                |

| D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0                                        | 41<br>40<br>39<br>38<br>36<br>34<br>33<br>32<br>31<br>29<br>28<br>27<br>26<br>24<br>23<br>22 | I/O/Z             | Parallel data bus D15 [most significant bit (MSB)] through D0 [least significant bit (LSB)]. D15–D0 are used to transfer data between the 'C206 devices and external data/program memory or I/O devices. Placed in the high-impedance state when not outputting (RD, WE high) or when RS asserted. They also go into the high-impedance state when OFF is active low. |

| A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1 | 74<br>73<br>72<br>71<br>69<br>68<br>67<br>66<br>64<br>62<br>61<br>60<br>58<br>57<br>56       | O/Z               | Parallel address bus A15 (MSB) through A0 (LSB). A15–A0 are used to address external data/program memory or I/O devices. These signals go into the high-impedance state when OFF is active low.                                                                                                                                                                       |

|                                                                                              |                                                                                              |                   | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                |

| PS                                                                                           | 53                                                                                           | O/Z               | Program-select. PS is always high unless low-level asserted for communicating to off-chip program space. PS goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                |

| DS                                                                                           | 51                                                                                           | O/Z               | Data-select. DS is always high unless low-level asserted for communicating to off-chip data space. DS goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                      |

| īS                                                                                           | 52                                                                                           | O/Z               | I/O space select. IS is always high unless low-level asserted for communicating to I/O ports. IS goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                           |

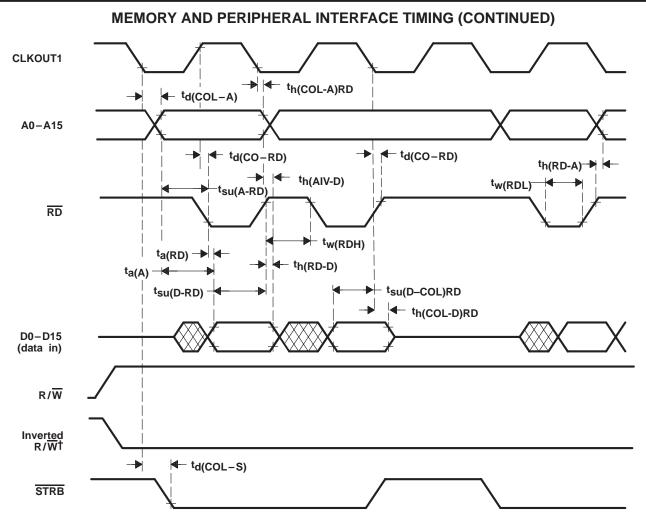

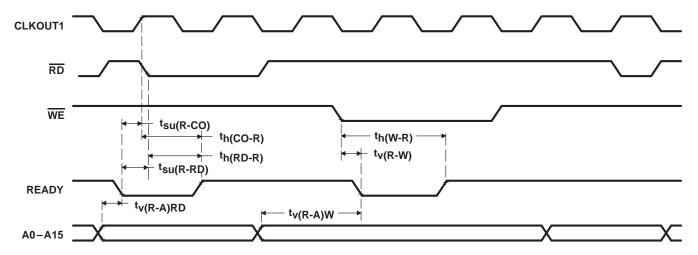

| READY                                                                                        | 49                                                                                           | ı                 | Data-ready. READY indicates that an external device is prepared for the bus transaction to be completed. If the external device is not ready (the external device pulls READY low), the 'C206 waits one cycle and checks READY again. If READY is not used, it should be pulled high.                                                                                 |

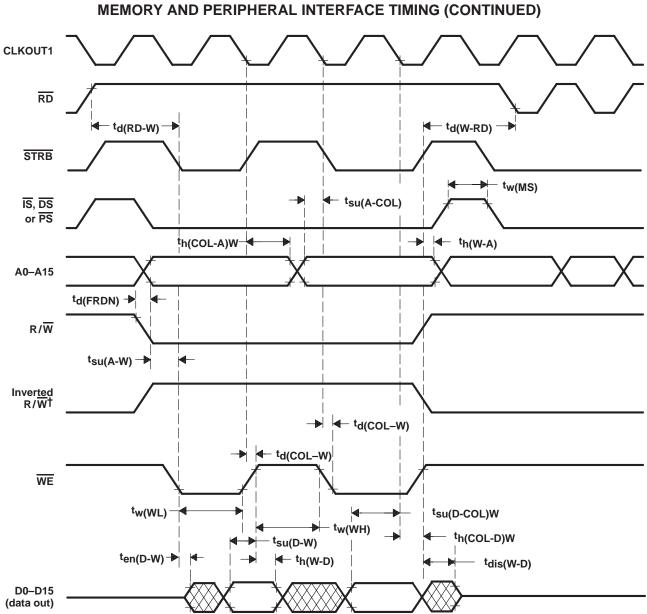

| R/W                                                                                          | 47                                                                                           | O/Z               | Read/write. R/W indicates data transfer direction when communicating with an external device. R/W is normally in read mode (high), unless low level is asserted for performing a write operation. R/W goes into the high-impedance state when OFF is active low.                                                                                                      |

<sup>†</sup> I = input, O = output, Z = high impedance, PWR = power, GND = ground

# TMS320C206, TMS320LC206 Terminal Functions (Continued)

| TERMIN                   | TERMINAL           |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------------|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                     | NO.                | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                          | ,                  |       | MEMORY CONTROL SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RD                       | 45                 | O/Z   | Read-select indicates an active, external read cycle. RD is active on all external program, data, and I/O reads. RD goes into the high-impedance state when OFF is active low. To implement a glueless zero wait-state memory interface, the inverted R/W signal can be used as the "read" signal in place of RD. The function of the RD pin can be programmed to provide an inverted R/W signal instead of RD. The FRDN bit (bit 15) in the PMST register controls this selection. FRDN=1 chooses R/W as the new "read" signal. FRDN=0 (at reset) chooses RD as the "read" signal on pin 45. |  |  |  |  |  |  |

| WE                       | 44                 | O/Z   | Write enable. The falling edge of WE indicates that the device is driving the external data bus (D15–D0). Data can be latched by an external device on the rising edge of WE. WE is active on all external program, data, and I/O writes. WE goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| STRB                     | 46                 | O/Z   | Strobe. STRB is always high unless asserted low to indicate an external bus cycle. STRB goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                          |                    |       | MULTI-PROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| BR                       | 43                 | O/Z   | Bus-request. BR is asserted when a global data-memory access is initiated. BR goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

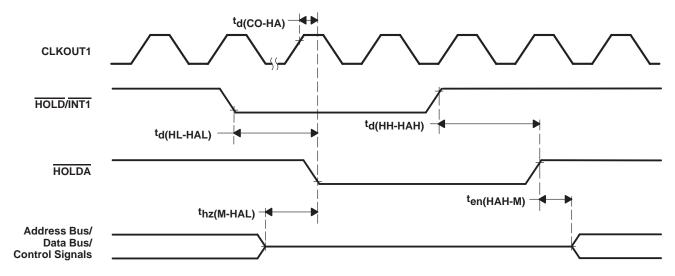

| HOLDA                    | 6                  | O/Z   | Hold-acknowledge. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and memory control lines are in the high-impedance state so that they are available to the external circuitry for access of local memory. HOLDA goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

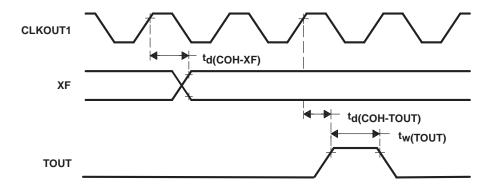

| XF                       | 98                 | O/Z   | External flag output (latched software-programmable signal). XF is used for signalling other processors in multiprocessing configurations or as a general-purpose output pin. XF goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

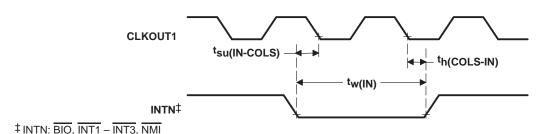

| BIO                      | 99                 | ı     | Branch control input. When polled by the BCND pma, BIO instruction, 'C206 executes a branch to the specified program memory address if BIO is low.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| IO0<br>IO1<br>IO2<br>IO3 | 96<br>97<br>8<br>9 | I/O/Z | Software-controlled input/output by way of the asynchronous serial-port control register (ASPCR). At reset, IO0–IO3 are configured as inputs. These pins can be used as general-purpose input/output pins or as handshake control for the UART. IO0–IO3 go into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                          |                    |       | INITIALIZATION, INTERRUPTS, AND RESET OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

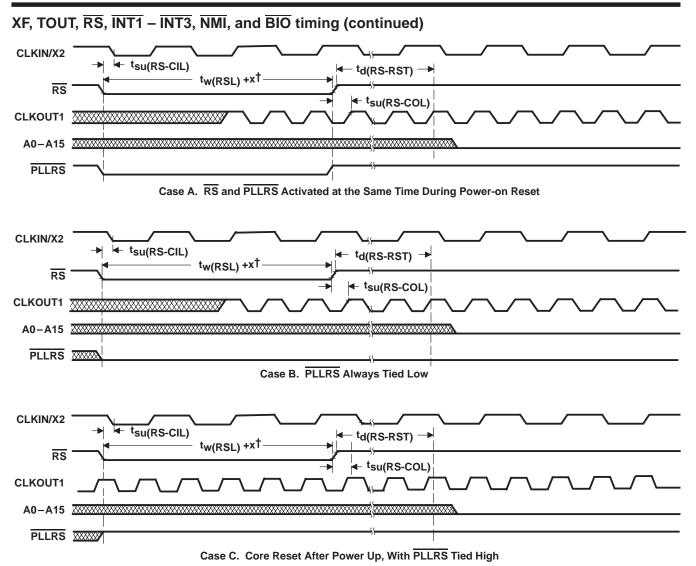

| RS                       | 100                | ı     | Reset. RS causes the 'C206 and 'LC206 to terminate execution and forces the program counter to zero. When RS is brought high, execution begins at location 0 of program memory after 16 cycles. RS affects various registers and status bits.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| PLLRS                    | 10                 | I     | Phase locked loop reset. PLLRS resets the PLL to initiate PLL locking. At power up, both PLLRS and RS should be active (low) to reset the DSP core and the PLL circuitry. The PLL can only be reset along with the core as shown in Table 2. The state of the PLLRS is not applicable for ÷2 mode and should always be tied high or low.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

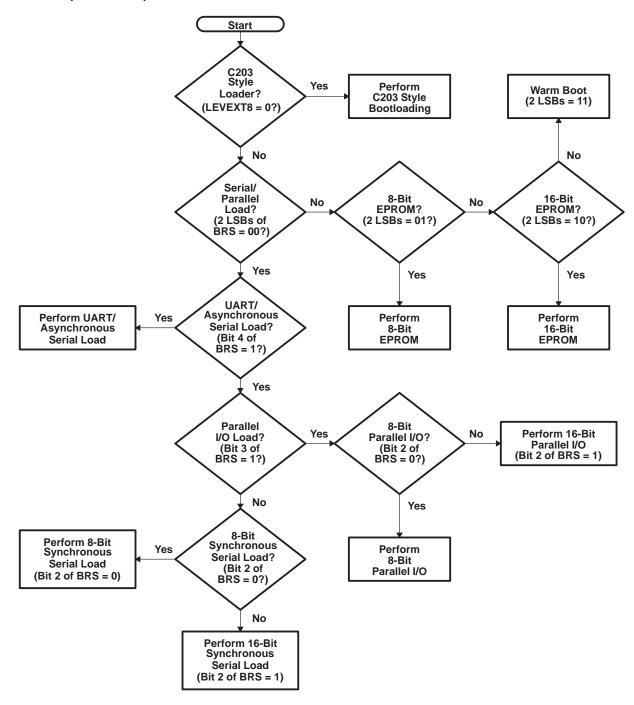

| EXT8                     | 1                  | I     | Bootloader mode pin. EXT8 is latched to bit 3 (LEVEXT8) in the PMST register. The bootloader located in ROM uses EXT8 to determine the type of boot method. If EXT8 is high, the enhanced 'C206 bootloader is used. If EXT8 is low, the 'C203 style bootloader is used. Refer to the <i>TMS320C20x User's Guide</i> (literature number SPRU127) for more details regarding the 'C203 style bootloader.                                                                                                                                                                                        |  |  |  |  |  |  |

| MP/MC                    | 2                  | I     | Microprocessor/microcomputer mode select. If MP/MC is low, the on-chip ROM memory is mapped into program space. When MP/MC is high, the device accessess off-chip memory. This pin is only sampled at RESET, and its value is latched into bit 0 of the PMST register.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| NMI                      | 17                 | I     | Nonmaskable interrupt. $\overline{\text{NMI}}$ is an external interrupt that cannot be masked by way of the interrupt-mode bit (INTM) or the interrupt-mask register (IMR). When $\overline{\text{NMI}}$ is activated, the processor traps to the appropriate vector location. If $\overline{\text{NMI}}$ is not used, it should be pulled high.                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| HOLD/INT1                | 18                 | I     | HOLD and INT1 share the same pin. Both are treated as interrupt signals. If the MODE bit is 0 in the interrupt control register (ICR), hold logic can be implemented in combination with the IDLE instruction in software. At reset, the MODE bit in ICR is zero, enabling the HOLD mode for the pin.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| INT2<br>INT3             | 19<br>20           | I     | External user interrupts. INT2 and INT3 are prioritized and maskable by the IMR and the INTM. INT2 and INT3 can be polled and reset by way of the interrupt flag register (IFR).                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

<sup>†</sup> I = input, O = output, Z = high impedance, PWR = power, GND = ground

# TMS320C206, TMS320LC206 Terminal Functions (Continued)

| TERMIN         | TERMINAL |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME           | NO.      | TYPET  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                |          |        | OSCILLATOR, PLL, AND TIMER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| тоит           | 92       | 0      | Timer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is one CLKC cycle wide. TOUT goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                                  |  |  |  |  |

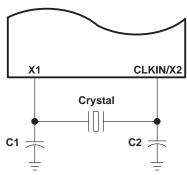

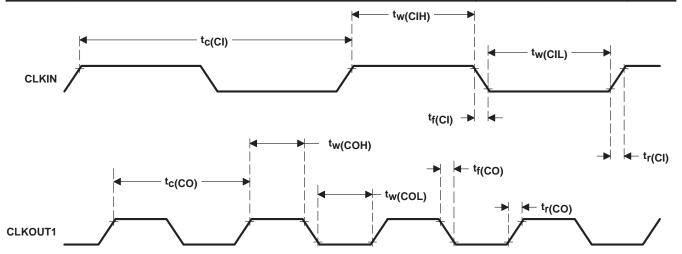

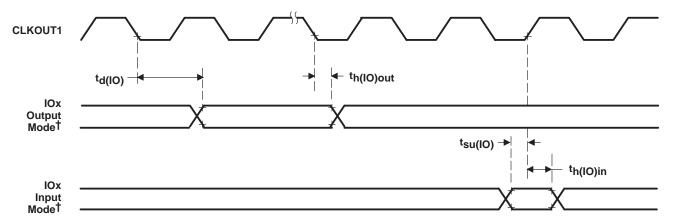

| CLKOUT1        | 15       | O/Z    | Master clock ouput. The CLKOUT1 high pulse signifies the logic phase while the low pulse signifies the latch phase.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

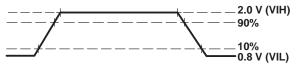

| CLKIN/X2<br>X1 | 12<br>13 | I<br>0 | Input clock. CLKIN/X2 is the input clock to the device. As CLKIN, the pin operates as the external oscillator clock input and as X2, the pin operates as the internal oscillator input with X1 being the internal oscillator output.                                                                                                                                                                                                                                |  |  |  |  |

| DIV1<br>DIV2   | 3<br>5   | I      | DIV1 and DIV2 are used to configure the on-chip PLL options, providing four clock modes $(\div 2, \times 1, \times 2, \text{ and } \times 4)$ for a given input clock frequency. Refer to clock options in electrical characteristics section. Note that in the divide-by-2 mode, the PLL is bypassed. DIV1 – DIV2 should not be changed unless the $\overline{\text{RS}}$ signal is active.                                                                        |  |  |  |  |

|                |          |        | SERIAL PORT SIGNALS (SSP AND ASP)                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

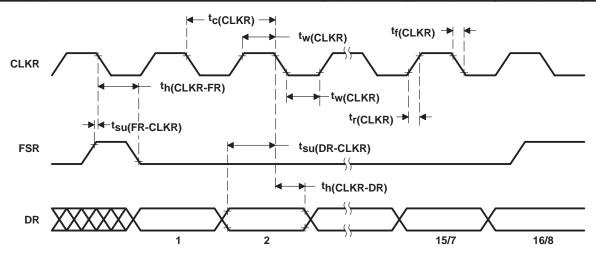

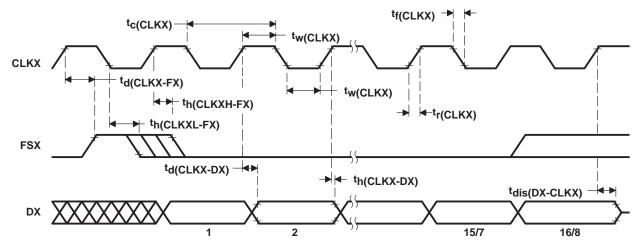

| CLKX           | 87       | I/O    | Transmit clock. CLKX is a clock signal for clocking data from the XSR (transmit shift register) to the DX data-transmit pin. CLKX can be an input if the MCM bit in the synchronous serial-port control register (SSPCR) is set to 0. CLKX can also be driven by the device at one-half of the CLKOUT1 frequency when MCM = 1. If the serial port is not being used, CLKX goes into the high-impedance state when OFF is active low. Value at reset is as an input. |  |  |  |  |

| CLKR           | 84       | I      | Receive clock. External clock signal for clocking data from the DR (data-receive) pin into the serial-port receive shift register (RSR). CLKR must be present during serial-port transfers. If the serial port is not being used, CLKR can be sampled as an input by IN0 bit of the SSPCR.                                                                                                                                                                          |  |  |  |  |

| FSX            | 89       | I/O    | Frame synchronization pulse for transmit. The falling edge of the FSX pulse initiates the data-transmit process, beginning the clocking of the SR. Following reset, FSX is an input. FSX can be selected by software to be an output when the TXM bit in the serial control register, SSPCR, is set to 1. FSX goes into the high-impedance state when OFF is active low.                                                                                            |  |  |  |  |

| FSR            | 85       | ı      | Frame synchronization pulse for receive input. The falling edge of the FSR pulse initiates the data-receive process, beginning the clocking of the RSR. FSR goes into the high-impedance state when OFF is active low.                                                                                                                                                                                                                                              |  |  |  |  |

| DX             | 90       | 0      | Synchronous serial port (SSP) data transmit output. Serial data is transmitted from the transmit shift register (XSR) through the DX pin. DX is in the high-impedance state when OFF is active low.                                                                                                                                                                                                                                                                 |  |  |  |  |

| DR             | 86       | ı      | Synchronous serial port (SSP) data receive input. Serial data is received in the receive shift register (RSR) through the DR pin.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| TX             | 93       | 0      | Asynchronous serial port (ASP/UART) data transmit output pin                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| RX             | 95       | I      | Asynchronous serial port (ASP/UART) data receive pin                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                |          |        | TEST SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TRST           | 79       | ı      | IEEE Standard 1149.1 (JTAG) test reset. TRST, when active high, gives the scan system control of the operations of the device. If TRST is driven low, the device operates in its functional mode, and the test signals are ignored. If the TRST pin is not driven, an external pulldown resistor must be used.                                                                                                                                                      |  |  |  |  |

| тск            | 78       | I      | JTAG test clock. TCK is normally a free-running clock signal with a 50% duty cycle. The changes on the test-access port (TAP) input signals (TMS and TDI) are clocked into the TAP controller, instruction register, or selected test-data register on the rising edge of TCK. Changes at the TAP output signal (TDO) occur on the falling edge of TCK.                                                                                                             |  |  |  |  |

| TMS            | 81       | I      | JTAG test-mode select. TMS is clocked into the TAP controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TDI            | 80       | I      | JTAG test-data input. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| TDO            | 82       | O/Z    | JTAG test-data output. The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when the scanning of data is in progress.                                                                                                                                                                                                                                           |  |  |  |  |

| EMU0           | 76       | I/O/Z  | Emulator pin 0. When TRST is driven low, EMU0 must be high for activation of the OFF condition. When TRST is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined as an input/output through the JTAG scan.                                                                                                                                                                                                                      |  |  |  |  |

<sup>†</sup> I = input, O = output, Z = high impedance, PWR = power, GND = ground

# TMS320C206, TMS320LC206 Terminal Functions (Continued)

| TERMINA          | AL                                                                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.                                                                              | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  |                                                                                  |       | TEST SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EMU1/OFF 77      |                                                                                  | I/O/Z | Emulator pin 1. Emulator pin 1 disables all outputs. When TRST is driven high, EMU1/OFF is used as an interrupt to or from the emulator system and is defined as an input/output through the JTAG scan. When TRST is driven low, this pin is configured as OFF. EMU1/OFF, when active low, puts all output drivers in the high-impedance state. Note that OFF is used exclusively for testing and emulation purposes (not for multiprocessing applications). Therefore, for the OFF condition, the following apply:  TRST = 0  EMU0 = 1  EMU1/OFF = 0 |

|                  |                                                                                  |       | SUPPLY PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD5</sub> | 7<br>16<br>35<br>50<br>63<br>91                                                  | PWR   | 5-V I/O power supply (Applicable for TMS320C206 only <sup>‡</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DD</sub>  | 7<br>16<br>35<br>50<br>63<br>91                                                  | PWR   | 3.3-V I/O power supply (Applicable for 'LC206 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DD</sub>  | 4<br>11<br>75                                                                    | PWR   | 3.3-V core power supply (Applicable for both 'C206 and 'LC206 devices <sup>‡</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vss              | 14<br>21<br>25<br>30<br>37<br>42<br>48<br>54<br>59<br>65<br>70<br>83<br>88<br>94 | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>†</sup> I = input, O = output, Z = high impedance, PWR = power, GND = ground

Table 2. Resetting the DSP Core and PLL Circuitry

| RS | PLLRS | CORE STATUS      | PLL STATUS        |

|----|-------|------------------|-------------------|

| 0  | 0     | Reset            | Reset             |

| 0  | 1     | Reset            | Normal Operation  |

| 1  | 0     | Normal Operation | Normal Operation§ |

| 1  | 1     | Normal Operation | Normal Operation  |

<sup>§</sup> The PLL can only be reset along with the DSP core and peripherals.

<sup>&</sup>lt;sup>‡</sup> For the 'C206, the 3.3-V and 5-V power supplies may be sequenced in any order.

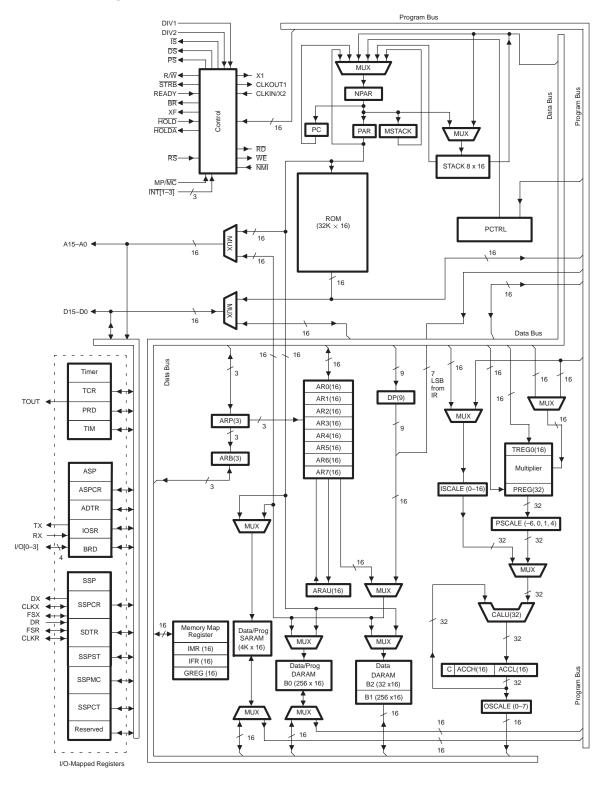

# functional block diagram of the 'C206 internal hardware

NOTES: A. Symbol descriptions appear in Table 3 and Table 4.

B. For clarity, the data and program buses are shown as single buses although they include address and data bits.

Table 3. Legend for the 'C206 Internal Hardware Functional Block Diagram

| SYMBOL                | NAME                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACC                   | Accumulator                                           | 32-bit register that stores the results and provides input for subsequent CALU operations. Also includes shift and rotate capabilities. ACCH is the accumulator high word; ACCL is the accumulator low word.                                                                                                                                                         |

| ADTR                  | Asynchronous<br>Data Transmit and<br>Receive Register | 16-bit read/write register used to transmit data from/receive data into the asynchronous serial port. Note that the ASP works with 8-bit data.                                                                                                                                                                                                                       |

| ARAU                  | Auxiliary Register<br>Arithmetic Unit                 | An unsigned, 16-bit arithmetic unit used to calculate indirect addresses using the auxiliary registers as inputs and outputs.                                                                                                                                                                                                                                        |

| ARB                   | Auxiliary Register<br>Pointer Buffer                  | See Table 4 for status register field definitions.                                                                                                                                                                                                                                                                                                                   |

| ARP                   | Auxiliary Register<br>Pointer                         | See Table 4 for status register field definitions.                                                                                                                                                                                                                                                                                                                   |

| ASP                   | Universal<br>Asynchronous<br>Receive/Transmit         | ASP is the asynchronous serial port (UART).                                                                                                                                                                                                                                                                                                                          |

| ASPCR                 | Asynchronous<br>Serial-Port Control<br>Register       | ASPCR controls the asynchronous serial-port operation This register contains bits for setting port modes, enabling/disabling automatic baud-rate detection, selecting the number of stop bits, and configuring I/O pins, etc.                                                                                                                                        |

| AUX REGS<br>(AR0–AR7) | Auxiliary Registers 0-7                               | These 16-bit registers are used as pointers to anywhere within the data space address range. They are operated upon by the ARAU and are selected by the auxiliary register pointer (ARP). AR0 can also be used as an index value for AR updates of more than one and as a compare value to AR.                                                                       |

| BR                    | Bus Request<br>Signal                                 | BR is asserted during access of the external global data memory space. READY is asserted to the device when the global data memory is available for the bus transaction. BR can be used to extend the data memory address space by up to 32K words.                                                                                                                  |

| BRD                   | Baud-Rate Divisor                                     | Used to set the baud rate of the UART                                                                                                                                                                                                                                                                                                                                |

| С                     | Carry                                                 | Register carry output from CALU. C is fed back into the CALU for extended arithmetic operation. The C bit resides in status register 1 (ST1), and can be tested in conditional instructions. C is also used in accumulator shifts and rotates.                                                                                                                       |

| CALU                  | Central Arithmetic<br>Logic Unit                      | 32-bit-wide main arithmetic logic unit for the TMS320C20x core. The CALU executes 32-bit operations in a single machine cycle. CALU operates on data coming from ISCALE or PSCALE with data from ACC, and provides status results to PCTRL.                                                                                                                          |

| DARAM                 | Dual Access RAM                                       | If the on-chip RAM configuration control bit (CNF) is set to 0, the reconfigurable dual-access RAM (DARAM) block B0 is mapped to data space; otherwise, B0 is mapped to program space. Blocks B1 and B2 are mapped to data memory space only, at addresses 0300–03FF and 0060–007F, respectively. Blocks 0 and 1 contain 256 words, while Block 2 contains 32 words. |

| DP                    | Data Memory<br>Page Pointer                           | See Table 4 for status register field definitions.                                                                                                                                                                                                                                                                                                                   |

| GREG                  | Global Memory<br>Allocation<br>Register               | GREG specifies the size of the global data memory space.                                                                                                                                                                                                                                                                                                             |

| IFR                   | Interrupt Flag<br>Register                            | The 7-bit IFR indicates that the 'C206 has latched an interrupt pulse from one of the seven maskable interrupt sources.                                                                                                                                                                                                                                              |

| IMR                   | Interrupt Mask<br>Register                            | IMR individually masks or enables the seven interrupts.                                                                                                                                                                                                                                                                                                              |

| INT#                  | Interrupt Traps                                       | A total of 32 interrupts by way of hardware and/or software are available.                                                                                                                                                                                                                                                                                           |

| IOSR                  | I/O Status<br>Register                                | IOSR detects current levels (and changes with inputs) on pins IO0-IO3 and the status of UART.                                                                                                                                                                                                                                                                        |

| IR                    | Instruction<br>Register                               | IR is the instruction register.                                                                                                                                                                                                                                                                                                                                      |

# Table 3. Legend for the 'C206 Internal Hardware Functional Block Diagram (Continued)

| SYMBOL | NAME                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISCALE | Input Data-Scaling<br>Shifter                          | 16-bit to 32-bit barrel left-shifter. ISCALE (ISFL) shifts incoming 16-bit data 0 to 16 positions left, relative to the 32-bit output within the fetch cycle; therefore, no cycle overhead is required for input scaling operations.                                                                                                                                                                                                         |

| MPY    | Multiplier                                             | $16 \times 16$ -bit multiplier to a 32-bit product. MPY executes multiplication in a single cycle. MPY operates either signed or unsigned 2s-complement arithmetic multiply.                                                                                                                                                                                                                                                                 |

| MSTACK | Micro Stack                                            | MSTACK provides temporary storage for the address of the next instruction to be fetched when program-address-generation logic is used to generate sequential addresses in data space.                                                                                                                                                                                                                                                        |

| MUX    | Multiplexer                                            | Multiplexes buses to a common input                                                                                                                                                                                                                                                                                                                                                                                                          |

| NPAR   | Next Program<br>Address Register                       | NPAR holds the program address to be driven out on the PAB on the next cycle.                                                                                                                                                                                                                                                                                                                                                                |

| OSCALE | Output<br>Data-Scaling<br>Shifter                      | 32-bit to 16-bit barrel left-shifter. OSCALE (OSFL) shifts the 32-bit accumulator output 0 to 7 bits left for quantization management and outputs either the 16-bit high- or low-half of the shifted 32-bit data to the Data-Write Data Bus (DWEB).                                                                                                                                                                                          |

| PAR    | Program Address<br>Register                            | PAR holds the address currently being driven on PAB for as many cycles as it takes to complete all memory operations scheduled for the current bus cycle.                                                                                                                                                                                                                                                                                    |

| PC     | Program Counter                                        | PC increments the value from NPAR to provide sequential addresses for instruction-fetching and sequential data-transfer operations.                                                                                                                                                                                                                                                                                                          |

| PCTRL  | Program<br>Controller                                  | PCTRL decodes instruction, manages the pipeline, stores status, and decodes conditional operations.                                                                                                                                                                                                                                                                                                                                          |

| PRD    | Timer-Period<br>Register                               | PRD contains the 16-bit period that is loaded into the timer counter when the counter borrows or when the reload bit is activated. Reset initializes the PRD to FFFFh.                                                                                                                                                                                                                                                                       |

| PREG   | Product Register                                       | 32-bit register holds results of 16 × 16 multiply.                                                                                                                                                                                                                                                                                                                                                                                           |

| PSCALE | Product-Scaling<br>Shifter                             | 0-, 1- or 4-bit left shift or 6-bit right shift of multiplier product. The left-shift options are used to manage the additional sign bits resulting from the 2s-complement multiply. The right-shift option is used to scale down the number to manage overflow of product accumulation in the CALU. PSCALE (PSFL) resides in the path from the 32-bit product shifter and from either the CALU or the DWEB, and requires no cycle overhead. |

| SDTR   | Synchronous Data<br>Transmit and<br>Receive Register   | 16-bit read/write register used to transmit data from/receive data into the synchronous serial port. This register functions as the path to the transmit and receive FIFOs of the SSP.                                                                                                                                                                                                                                                       |

| SSP    | Synchronous<br>Serial-Port                             | SSP is the synchronous serial-port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| SSPCR  | Synchronous<br>Serial-Port Control<br>Register         | SSPCR is the control register for selecting the serial port's mode of operation.                                                                                                                                                                                                                                                                                                                                                             |

| SSPCT  | Synchronous<br>Serial-Port<br>Counter Register         | SSPCT is the synchronous serial-port counter register.                                                                                                                                                                                                                                                                                                                                                                                       |

| SSPMC  | Synchronous<br>Serial-Port<br>Multichannel<br>Register | SSPMC is the synchronous serial-port multichannel register.                                                                                                                                                                                                                                                                                                                                                                                  |

| SSPST  | Synchronous<br>Serial-Port<br>Status Register          | SSPST is the synchronous serial-port status register.                                                                                                                                                                                                                                                                                                                                                                                        |

| STACK  | Stack                                                  | STACK is a block of memory used for storing return addresses for subroutines and interrupt-service routines, or for storing data. The 'C20x stack is 16-bit wide and eight-level deep.                                                                                                                                                                                                                                                       |

| TCR    | Timer-Control<br>Register                              | TCR contains the control bits that define the divide-down ratio, start/stop the timer, and reload the period. Also contained in TCR is the current count in the prescaler. Reset initializes the timer divide-down ratio to 0 and starts the timer.                                                                                                                                                                                          |

Table 3. Legend for the 'C206 Internal Hardware Functional Block Diagram (Continued)

| SYMBOL | NAME                      | DESCRIPTION                                                                                                                                                                                                        |

|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIM    | Timer-Counter<br>Register | TIM contains the current 16-bit count of the timer. Reset initializes the TIM to FFFFh.                                                                                                                            |

| TREG   | Temporary<br>Register     | 16-bit register holds one of the operands for the multiply operations. TREG holds the dynamic shift count for the LACT, ADDT, and SUBT instructions. TREG holds the dynamic bit position for the BITT instruction. |

#### architectural overview

The 'C206 advanced Harvard-type architecture maximizes the processing power by maintaining two separate memory bus structures—program and data—for full-speed execution. The multiple buses allow data and instructions to be read simultaneously. Instructions support data transfers between the two spaces. This architecture permits coefficients stored in program memory to be read in RAM, eliminating the need for a separate coefficient RAM. This, coupled with a four-instruction deep pipeline, allows the TMS320C206/TMS320LC206 to execute most instructions in a single cycle.

#### status and control registers

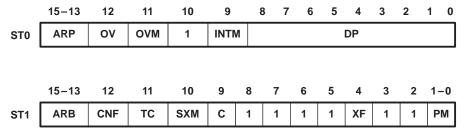

Two status registers, ST0 and ST1, contain the status of various conditions and modes. These registers can be stored into data memory and loaded from data memory, thus allowing the status of the machine to be saved and restored for subroutines.

The load-status register (LST) instruction is used to write to ST0 and ST1 (except the INTM bit which is not affected by the LST instruction). The store-status register (SST) instruction is used to read from the ST0 and ST1. The individual bits of these registers can be set or cleared by the SETC and CLRC instructions. Figure 1 shows the organization of status registers ST0 and ST1, indicating all status bits contained in each. Several bits in the status registers are reserved and are read as logic 1s. See Table 4 for status-register field definitions.

Figure 1. Status and Control Register Organization

### status and control registers (continued)

**Table 4. Status Register Field Definitions**

| FIELD | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARB   | Auxiliary register pointer buffer. Whenever the ARP is loaded, the old ARP value is copied to the ARB except during an LST instruction. When the ARB is loaded by an LST #1 instruction, the same value is also copied to the ARP.                                                                                                                                                                                                                                                                                                                                                                    |

| ARP   | Auxiliary register pointer. ARP selects the auxiliary register (AR) to be used in indirect addressing. When the ARP is loaded, the old ARP value is copied to the ARB register. ARP can be modified by memory-reference instructions when using indirect addressing, and by the LARP, MAR, and LST instructions. The ARP is also loaded with the same value as ARB when an LST #1 instruction is executed.                                                                                                                                                                                            |

| С     | Carry bit. C is set to 1 if the result of an addition generates a carry, or reset to 0 if the result of a subtraction generates a borrow. Otherwise, C is reset after an addition or set after a subtraction, except if the instruction is ADD or SUB with a 16-bit shift. In these cases, the ADD can only set and the SUB only reset the carry bit, but cannot affect it otherwise. The single-bit shift and rotate instructions also affect C, as well as the SETC, CLRC, and LST #1 instructions. Branch instructions have been provided to branch on the status of C. C is set to 1 on a reset.  |

| CNF   | On-chip RAM configuration-control bit. If CNF is set to 0, the reconfigurable data DARAM blocks are mapped to data space; otherwise, they are mapped to program space. The CNF can be modified by the SETC CNF, CLRC CNF, and LST #1 instructions. RS sets the CNF to 0.                                                                                                                                                                                                                                                                                                                              |

| DP    | Data memory page pointer. The 9-bit DP register is concatenated with the seven LSBs of an instruction word to form a direct memory address of 16 bits. DP can be modified by the LST and LDP instructions.                                                                                                                                                                                                                                                                                                                                                                                            |

| INTM  | Interrupt-mode bit. When INTM is set to 0, all unmasked interrupts are enabled. When set to 1, all maskable interrupts are disabled. INTM is set and reset by the SETC INTM and CLRC INTM instructions. INTM has no effect on the nonmaskable RS and NMI interrupts. Note that INTM is unaffected by the LST instruction. This bit is set to 1 when a maskable interrupt is acknowledged or when RS is asserted.                                                                                                                                                                                      |

| OV    | Overflow-flag bit. As a latched overflow signal, OV is set to 1 when overflow occurs in the ALU. Once an overflow occurs, the OV remains set until a reset, BCND/D on OV/NOV, or LST instruction clears OV.                                                                                                                                                                                                                                                                                                                                                                                           |

| OVM   | Overflow-mode bit. When OVM is set to 0, overflowed results overflow normally in the accumulator. When set to 1, the accumulator is set to either its most positive or negative value upon encountering an overflow. The SETC and CLRC instructions set and reset this bit, respectively. LST also can be used to modify the OVM.                                                                                                                                                                                                                                                                     |

| РМ    | Product-shift mode. If these two bits are 00, the multiplier's 32-bit product is loaded into the ALU with no shift. If PM = 01, the PREG output is left-shifted one place and loaded into the ALU, with the LSB zero-filled. If PM = 10, the PREG output is left-shifted by four bits and loaded into the ALU, with the LSBs zero-filled. PM = 11 produces a right shift of six bits, sign-extended. Note that the PREG contents remain unchanged. The shift takes place when transferring the contents of the PREG to the ALU. PM is loaded by the SPM and LST #1 instructions. PM is cleared by RS. |

| SXM   | Sign-extension mode bit. SXM = 1 produces sign extension on data as it is passed into the accumulator through the scaling shifter. SXM = 0 suppresses sign extension. SXM does not affect the definitions of certain instructions; for example, the ADDS instruction suppresses sign extension regardless of SXM. SXM is set by the SETC SXM and reset by the CLRC SXM instructions, and can be loaded by the LST #1. SXM is set to 1 by reset.                                                                                                                                                       |

| тс    | Test/control flag bit. TC is affected by the BIT, BITT, CMPR, LST #1, and NORM instructions. TC is set to a 1 if a bit tested by BIT or BITT is a 1, if a compare condition tested by CMPR exists between AR (ARP) and AR0, if the exclusive-OR function of the two MSBs of the accumulator is true when tested by a NORM instruction. The conditional branch, call, and return instructions can execute, based on the condition of TC.                                                                                                                                                               |

| XF    | XF pin status bit. XF indicates the state of the XF pin, a general-purpose output pin. XF is set by the SETC XF and reset by the CLRC XF instructions. XF is set to 1 by reset.                                                                                                                                                                                                                                                                                                                                                                                                                       |

### central processing unit

The TMS320C206/TMS320LC206 central processing unit (CPU) contains a 16-bit scaling shifter, a 16 x16-bit parallel multiplier, a 32-bit central arithmetic logic unit (CALU), a 32-bit accumulator, and additional shifters at the outputs of both the accumulator and the multiplier. This section describes the CPU components and their functions. The functional block diagram shows the components of the CPU.

### input scaling shifter

The TMS320C206/TMS320LC206 provides a scaling shifter with a 16-bit input connected to the data bus and a 32-bit output connected to the CALU. This shifter operates as part of the path of data coming from program or data space to the CALU, and requires no cycle overhead. It is used to align the 16-bit data coming from memory to the 32-bit CALU. This is necessary for scaling arithmetic as well as aligning masks for logical operations.

The scaling shifter produces a left shift of 0 to 16 on the input data. The LSBs of the output are filled with zeros; the MSBs may either be filled with zeros or sign-extended, depending upon the value of the SXM bit (sign-extension mode) of status register ST1. The shift count is specified by a constant embedded in the instruction word or by a value in TREG. The shift count in the instruction allows for specific scaling or alignment operations specific to that point in the code. The TREG base shift allows the scaling factor to adapt to the performance of the system.

#### multiplier

The TMS320C206/TMS320LC206 uses a 16 x16-bit hardware multiplier that is capable of computing a signed or an unsigned 32-bit product in a single machine cycle. All multiply instructions, except the MPYU (multiply unsigned) instruction, perform a signed-multiply operation. That is, two numbers being multiplied are treated as 2s-complement numbers, and the result is a 32-bit 2s-complement number. There are two registers associated with the multiplier:

- a 16-bit temporary register (TREG) that holds one of the operands for the multiplier, and

- a 32-bit product register (PREG) that holds the product.